Aleksei_Rostov

Свой-

Постов

313 -

Зарегистрирован

-

Посещение

Весь контент Aleksei_Rostov

-

Реализацию ещё не начал, но про проблему с фазой слышу второй раз. Речь идёт о подстройке клока и потока бит?

-

Благодарю, как раз читал данный документик ))

-

Здравствуйте. Подскажите пжл решение для след задачи: Передача кадра с платы MAX 10 по протоколу Base Camera Link. Написать сериализатор на 28 бит самому и выдать данные на диф пары (т.е. решение "в лоб") не получиться? Или есть готовые ядра? Посоветуйте пжл готовые сериализаторы, кот подключаются к пинам ПЛИС, принимают данные и преобразуют в Camera Link протокол.

-

Здравствуйте! Может кто нибудь из форумчан запускал Ethernet на Artix-7 50T FPGA Evaluation Kit? Использую Ethernet Lite + MII to RMII ядра vivado 2014.3. Просто пишу в регистры Ethernet Lite числа по структуре UDP пакета. Для Nexus 3 на Spartan 6 проект работает без проблем. На artix-7 загорается светодиод phy_error_n. и phy микросхема живет своей жизнью, или точнее отсылает одни и те же пакеты (как будто подгрузился заводской проект из флеш) . При этом ядро MII to RMII заменил согласно мануала lwIP

-

Уважаемые форумчане поделитесь пожалуйста мнением как лучше организовать транзакции по шине с AXI 4. Итак, есть слейв и два мастера. Один мастер пишет, другой читает. Оба работают с одним и тем же слейвом. Мастер пишет данные которые поступают со скоростью 10 МГц (от процессора или датамувера), шина на 100 МГц, чтение также со скоростью 100 МГц (бурстами, например читает ДМА из ДДР, БРАМ ...). Транзакции чтение/запись осуществляются одновременно, но по разным адресам. В мастере записи есть возможность реализовать ФИФО и писать в слейв бюрстами по 100 МГц. Стоит ли так делать или оставить поток на 10 МГц? Насколько я понимаю, в шине должен быть алгоритм собирания данных в бюрст? Могут мастера конфликтовать между собой? Или канал записи и чтения для слейва полностью независимы?

-

очень признателен!

-

Здравствуйте! Может кто нибудь сталкивался с документацией для board Artix 7 a50t? http://www.xilinx.com/products/boards-and-kits/1-4pilqh.html Интересует какие ноги куда выведены (ucf файл)?

-

Необходимо скачать vivado от 2013.4 версии. Каким образом с сайта xilinx не подскажите? Как завести ящик на заморских сайтах? Gmail.com или yahoo.com пробовал не подходят.

-

Буквально недавно шил в память один старый проект, собранный в Q7.1. Для заливки во флеш использовал Q 11.1. Делал следующее: Залил через программер sof Открыл flash programmer там указал sopcinfo и добавил файлы на заливку: sof + elf нажал programm flash. отключил/включил питание. Все заработало

-

Попробуйте flash programmer в Eclipse. Там вручную конвертировать и объединять sof и elf не нужно.

-

около года назад делал проект на аналогичной плате с ethernet'ом. Среда была насколько помню 9.1 для сборки системы использовал SOPC а не qsys. С платой шли примеры для ethernet (tcp/ip и web). В качестве основы взял пример tcp/ip, в примере через командную строку можно было светодиоды зажигать на плате Далее в SOPC разобрал этот пример. Нашел функции записи/чтения буфера и отправления пакетов. Так собрал свой проект. если еще актуально могу поднять проект и посмотреть

-

могу на ящик выслать. farbius mail.ru пишите

-

Если хотите использовать DCM ядро, то coregenerator в помощь. Как настроить понятно интуитивно. Но для spartan 3e данного ядра нет.

-

Может объясню неточно, знающие меня поправят. Тактируемым элементом CLB ячейки ПЛИС является D триггер. Именно он используется синтезатором при интерпретации любых тактируемых алгоритмов. Триггер имеет вход CE разрешающий клок. Когда описываете алгоритм способом, который я привел, то по идее синтезатор распознает именно D триггер. Делить сам клок чревато приобретением джиттеров и как следствие ошибок в работе Вашей схемы. Вообще для клоков лучше использовать ядра типа DCM, PLL. Напрямую подавать на клок счетчика.

-

Я использую вход CE триггера. Например получить частоту 1 MHz из 50 MHz след образом. Отрывок кода для автомата работающего на 1 МГц process(clk) begin if (rising_edge(clk)) then -- Rising clock edge if Rst = '1' then state <= WaitPushBut; INC <= '0'; leds_reg <= x"00"; elsif(CEn = '1')then ----------------------------- case state is when Idle => if (timer = 1) then ................................................. clk здесь 50 МГц и есть сигнал CEn, по которому происходит работа автомата. Сигнал срабатывает с частотой 1 МГц. Получить его просто. Берете ядро для счетчика. Там есть опция порог и сигнал срабатывания порога. Этот сигнал и завожу на CEn. Например счетчик от 0 до 49. Порог 49. тогда частота срабатывания порога при частоте работы счетчика в 50 МГц / 50 = 1 МГц. То что вам необходимо.

-

Подскажите пожалуйста способы для уменьшения времени повторной сборки проекта в ISE. Случай когда проект уже собран, а потом внесены небольшие изменения. Сборка проекта начинается заново..( а это снова много времени... Читал про smartguide и attribute incremental_synthesis. В чем принципиальное отличие? Также в Plan Ahead можно использовать Precision Synthesis, но это уже более на низком уровне.. На сколько эффективны данные способы?

-

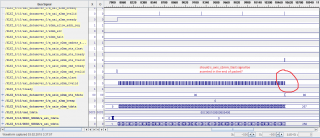

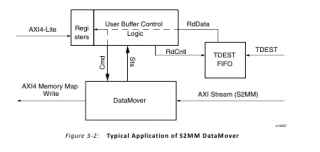

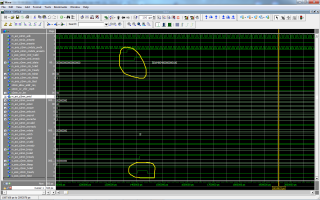

Здравствуйте! Возникла следующая проблема: Собираю систему DDR + PCie-bridge + cdma + datamover. Для DDR 3 мастера : PCie-bridge , cdma, datamover. Записал данных в DDR с помощью DataMover, дальнейшая попытка записать данные в DDR через PCIe приводит к зависанию компьютера. Есть подозрения на канал записи в AXI4. Может ли быть так: DataMover как мастер не разрешает запись в DDR другому мастеру(PCIe)? Как будто DataMover не завершает операцию записи. Скриншот сигналов DataMover Является ли сигнал s_axis_s2mm_tlast в конце пакета для завершения записи?

-

всего стрима. Моя корка была сделана также как у вас. Сигналы m_axis корки заведены на s_axis_s2mm, а сигналы s_axs - выведены наружу к фифо. Интерфейс у всех естественно стрим. Дать команду датамуверу -- значит записать слово в cmd регистр (то есть подать сигнал cmd_tvalid = '1')? Вообщем, сейчас разбираюсь в ise 14.7. Уже с мертвой точки сдвинулся: датамувер вычитывает адрес записи данных на шину с axi4. То есть датамувер начал общаться с шиной. разбираюсь далее, по окончанию отпишусь... Благодарю за ответы!

-

благодарю за шаблон, обязательно разберусь. прямое подключение есть, только корка стрим мастера (т.н. прокладка) вычитывает фифо после наполнения (т.е. весь burst), если без нее (так тоже делал), то фифо будет работать так: слово пришло, слово ушло. Корка СТрим мастер сначала ждет наполнения а потом вычитывает. Вообщем переделаю проект в новой версии среды, там видно будет.

-

Буду очень признателен за помощь)) В случаях с axi4 и axi4 light я просто создал user IP, а затем модифицировал файл user_logic.vhd. При создании своей корки для стрима, такой алгоритм не прокатил: корка становиться уже не стрим. Полагаю нужно далее ручками редактировать mpd, pao и т.д. файлы? Далее копать не стал. совершенно верно, только при опрокидывании происходит пауза для наполнения фифо. Пробывал и без этой прокладки: просто выход фифо соединил с s_axis_s2mm интерфейсом. Уже без ожидания наполнения фифо. Результат не изменился: теже 4 байта и затем сброс сигнала реади..(( Скачал 14.7 версию. Буду пробовать заново

-

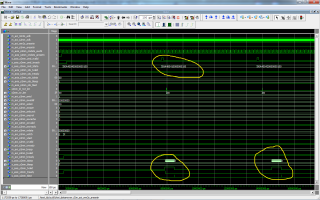

я работаю в ise 14.3 а Вы в 14.7. Поэтому у меня версия датамувера 3.0 в отличии от Вашей 4.05))) В остальном все точно также) совершенно верно я использую внешнее фифо сгенеренное coregen'ом, fifo выбрал с интерфейсом axi (а не традиционным как в Вашем случае) для согласования с аналогичным интерфейсом корки master_strm. Можно было и просто обернуть фифо. Но я использовал внешнее: обернуть как я делал до этого с user IP для axi4 или axi_light интерфейсов для user IP с интерфейсом stream не получилось, а разбираться времени пожалел, поэтому пошел по пути наименьшего сопротивления))) На самом деле это не критично: интерфейс все равно один и тот же)) Так вот master_strm как я сказал выше, контролирует наполнение фифо и соединяет это фифо со стрим интерфейсом датамувера. прокладка контролирует заполненность фифо, и дает команду датамуверу на передачу того числа байт, которое лежит в фифо. Команда в виде сигнала s_axis_s2mm_tvalid. Сигнал '1' пока фифо не выгрузит последнее слово. Потом ждем наполнения и снова '1' для выгрузки фифо.... А тут и проблема, когда s_axis_s2mm_tvalid = '1' , s_axis_s2mm_tready перекидывается датамувером в ноль.... :cranky: сигналы s_axis_s2mm_ (tlast, tvalid, tdata...) это сигналы стрим интерфейса датамувера вариант "напрямую" для меня тоже более привлекателен и я рассматривал его изначально. Не совсем понятно с наличием внутреннего фифо датамувера. В даташите сказано про режим C_S2MM_INCLUDE_SF, еще я предполагал что количество байт параметром burst_size регулирует размер внутреннего фифо, но теперь понимаю, что в датамувере не фифо, а скорее всего обычный счетчик количества байт (режим C_S2MM_INCLUDE_SF исключение).

-

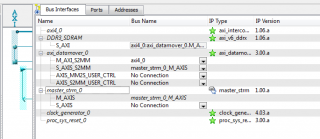

для разъяснения привожу собранный в xps проект итак, ddr + axi4 + datamover + master_strm (user IP или мой мастер стрим) master_strm подключен к datamover как мастер (M_AXIS) для s2mm через интерфейс axi stream, slave порты (S_AXIS) выведены "наружу" и подключены к выходу fifo (там где происходит буферизация потока). на вход fifo подключен генератор медленной последовательности. Прошу прощения за запутанность)) сигнал реади для fifo формирует master_strm по наполнению fifo. По этому сигналу данные из fifo потоком через master_strm подаются на вход datamover s_axis_s2mm_tdata. То есть master_srm я использую как мастер стрима для s_axis_s2mm моего datamover. Это позволяет контролировать наполнение fifo. До этого делал иначе: просто выводил сигналы s_axis_s2mm (_tvalid, _tlast, _tready ...) наружу и прикручивал к ним генератор медленной последовательности. за разъяснение отдельное спасибо.

-

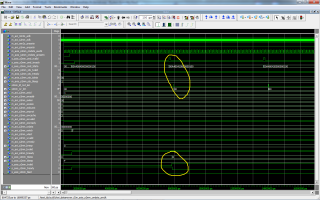

безусловно речь идет s_axis_s2mm попробовал сначала передать 4 слова и далее поток. Ситуация не изменилась. не совсем ясно. Логика проекта следующая: стрим ядро (мастер стрим для s2mm датамувера) получает валид от фифо как только началось наполнение, но реади в фифо для стрима не передает. Ждет пока фифо наполнится(запись в фифо происходит на меньшей частоте чем считывание). Это позволяет перейти от медленного клока потока к клоку для записи в ДДР, те буферизация. При считывании мастер стрим дает фифо сигнал реади, и стрим пошел в s2mm датамувера. Если так не делать, то поток будет на медленной частоте подаваться в датамувер. Тогда в составе датамувера должно быть фифо для накопления burst для трансфера. Очень может быть загвоздка в этом моменте. Как только внутреннее фифо датамувера наполняется, происходит трансфер. Размер фифо выставляется в настройках датамувера (burst size). Задумывался об этом... вы имеете в виду состав команды в cmd регистре, при которой датамувер не обращает внимание на ласт сигнал? не совсем ясно... tkeep я сейчас не использую. Но вообще сигнал выставляет стробы побайтной записи/считывания на AXI4 (побайтная адресация ).

-

просмотрел форум xilinx, ваш пост и сопутствующие посты. Обнаружил следующее у меня этот бит всегда ноль. В этом случае инкрементации не происходит, может поэтому после записи одного 32 разрядного слова датамувер переключает реади в ноль? завтра обязательно проверю

-

Приветствую. Большое спасибо за внимание. Продолжаю бороться с ентим датамувером. Пересобрал свой проект. В XPS проект имеет вид добавил стрим ядро, которое данные берет из фифо и по команде выдает датамуверу для трансфера вот мой .mhs # ############################################################################## # Created by Base System Builder Wizard for Xilinx EDK 14.3 Build EDK_P.40xd # Mon Dec 22 18:24:46 2014 # Target Board: xilinx.com ml605 Rev D # Family: virtex6 # Device: xc6vlx240t # Package: ff1156 # Speed Grade: -1 # ############################################################################## PARAMETER VERSION = 2.1.0 PORT ddr_memory_we_n = ddr_memory_we_n, DIR = O PORT ddr_memory_ras_n = ddr_memory_ras_n, DIR = O PORT ddr_memory_odt = ddr_memory_odt, DIR = O PORT ddr_memory_dqs_n = ddr_memory_dqs_n, DIR = IO, VEC = [0:0] PORT ddr_memory_dqs = ddr_memory_dqs, DIR = IO, VEC = [0:0] PORT ddr_memory_dq = ddr_memory_dq, DIR = IO, VEC = [7:0] PORT ddr_memory_dm = ddr_memory_dm, DIR = O, VEC = [0:0] PORT ddr_memory_ddr3_rst = ddr_memory_ddr3_rst, DIR = O PORT ddr_memory_cs_n = ddr_memory_cs_n, DIR = O PORT ddr_memory_clk_n = ddr_memory_clk_n, DIR = O, SIGIS = CLK PORT ddr_memory_clk = ddr_memory_clk, DIR = O, SIGIS = CLK PORT ddr_memory_cke = ddr_memory_cke, DIR = O PORT ddr_memory_cas_n = ddr_memory_cas_n, DIR = O PORT ddr_memory_ba = ddr_memory_ba, DIR = O, VEC = [2:0] PORT ddr_memory_addr = ddr_memory_addr, DIR = O, VEC = [12:0] PORT RESET = RESET, DIR = I, SIGIS = RST, RST_POLARITY = 1 PORT CLK_P = CLK, DIR = I, DIFFERENTIAL_POLARITY = P, SIGIS = CLK, CLK_FREQ = 200000000 PORT CLK_N = CLK, DIR = I, DIFFERENTIAL_POLARITY = N, SIGIS = CLK, CLK_FREQ = 200000000 PORT clk10MHz = clock_generator_0_CLKOUT4, DIR = O, SIGIS = CLK, CLK_FREQ = 10000000 PORT ARESETN = master_strm_0_M_AXIS_ARESETN, DIR = I PORT TREADY = master_strm_0_S_AXIS_TREADY, DIR = O PORT TDATA = master_strm_0_S_AXIS_TDATA, DIR = I, VEC = [31:0] PORT TLAST = master_strm_0_S_AXIS_TLAST, DIR = I PORT TVALID = master_strm_0_S_AXIS_TVALID, DIR = I PORT cmdsts_awclk = axi_datamover_0_m_axis_s2mm_cmdsts_awclk, DIR = I, SIGIS = CLK PORT cmdsts_aresetn = axi_datamover_0_m_axis_s2mm_cmdsts_aresetn, DIR = I, SIGIS = RST PORT cmd_tvalid = axi_datamover_0_s_axis_s2mm_cmd_tvalid, DIR = I PORT cmd_tready = axi_datamover_0_s_axis_s2mm_cmd_tready, DIR = O PORT cmd_tdata = axi_datamover_0_s_axis_s2mm_cmd_tdata, DIR = I, VEC = [71:0] PORT sts_tvalid = axi_datamover_0_m_axis_s2mm_sts_tvalid, DIR = O PORT sts_tready = axi_datamover_0_m_axis_s2mm_sts_tready, DIR = I PORT sts_tdata = axi_datamover_0_m_axis_s2mm_sts_tdata, DIR = O, VEC = [7:0] PORT sts_tkeep = axi_datamover_0_m_axis_s2mm_sts_tkeep, DIR = O PORT sts_tlast = axi_datamover_0_m_axis_s2mm_sts_tlast, DIR = O PORT mm2s_aresetn = axi4_0_S_m_axi_mm2s_aresetn, DIR = I, SIGIS = RST PORT s2mm_aresetn = axi4_0_S_m_axi_s2mm_aresetn, DIR = I, SIGIS = RST PORT clk100MHz = clk_100_0000MHzMMCM0, DIR = O, SIGIS = CLK, CLK_FREQ = 100000000 BEGIN proc_sys_reset PARAMETER INSTANCE = proc_sys_reset_0 PARAMETER HW_VER = 3.00.a PARAMETER C_EXT_RESET_HIGH = 1 PORT Dcm_locked = proc_sys_reset_0_Dcm_locked PORT Slowest_sync_clk = clk_100_0000MHzMMCM0 PORT Interconnect_aresetn = proc_sys_reset_0_Interconnect_aresetn PORT Ext_Reset_In = RESET END BEGIN clock_generator PARAMETER INSTANCE = clock_generator_0 PARAMETER HW_VER = 4.03.a PARAMETER C_CLKIN_FREQ = 200000000 PARAMETER C_CLKOUT0_FREQ = 100000000 PARAMETER C_CLKOUT0_GROUP = MMCM0 PARAMETER C_CLKOUT1_FREQ = 200000000 PARAMETER C_CLKOUT1_GROUP = MMCM0 PARAMETER C_CLKOUT2_FREQ = 400000000 PARAMETER C_CLKOUT2_GROUP = MMCM0 PARAMETER C_CLKOUT3_FREQ = 400000000 PARAMETER C_CLKOUT3_GROUP = MMCM0 PARAMETER C_CLKOUT3_BUF = FALSE PARAMETER C_CLKOUT3_VARIABLE_PHASE = TRUE PARAMETER C_CLKOUT4_FREQ = 10000000 PORT LOCKED = proc_sys_reset_0_Dcm_locked PORT CLKOUT0 = clk_100_0000MHzMMCM0 PORT RST = RESET PORT CLKOUT3 = clk_400_0000MHzMMCM0_nobuf_varphase PORT CLKOUT2 = clk_400_0000MHzMMCM0 PORT CLKOUT1 = clk_200_0000MHzMMCM0 PORT CLKIN = CLK PORT PSCLK = clk_200_0000MHzMMCM0 PORT PSEN = psen PORT PSINCDEC = psincdec PORT PSDONE = psdone PORT CLKOUT4 = clock_generator_0_CLKOUT4 END BEGIN axi_interconnect PARAMETER INSTANCE = axi4_0 PARAMETER HW_VER = 1.06.a PORT interconnect_aclk = clk_100_0000MHzMMCM0 PORT INTERCONNECT_ARESETN = proc_sys_reset_0_Interconnect_aresetn END BEGIN axi_v6_ddrx PARAMETER INSTANCE = DDR3_SDRAM PARAMETER HW_VER = 1.06.a PARAMETER C_MEM_PARTNO = MT41J64M16XX-15E PARAMETER C_DM_WIDTH = 1 PARAMETER C_DQS_WIDTH = 1 PARAMETER C_DQ_WIDTH = 8 PARAMETER C_MMCM_EXT_LOC = MMCM_ADV_X0Y8 PARAMETER C_NDQS_COL0 = 1 PARAMETER C_NDQS_COL1 = 0 PARAMETER C_S_AXI_BASEADDR = 0xa4000000 PARAMETER C_S_AXI_HIGHADDR = 0xa7ffffff PARAMETER C_INTERCONNECT_S_AXI_MASTERS = axi_datamover_0.M_AXI_S2MM BUS_INTERFACE S_AXI = axi4_0 PORT ddr_we_n = ddr_memory_we_n PORT ddr_ras_n = ddr_memory_ras_n PORT ddr_odt = ddr_memory_odt PORT ddr_dqs_n = ddr_memory_dqs_n PORT ddr_dqs_p = ddr_memory_dqs PORT ddr_dq = ddr_memory_dq PORT ddr_dm = ddr_memory_dm PORT ddr_reset_n = ddr_memory_ddr3_rst PORT ddr_cs_n = ddr_memory_cs_n PORT ddr_ck_n = ddr_memory_clk_n PORT ddr_ck_p = ddr_memory_clk PORT ddr_cke = ddr_memory_cke PORT ddr_cas_n = ddr_memory_cas_n PORT ddr_ba = ddr_memory_ba PORT ddr_addr = ddr_memory_addr PORT clk_rd_base = clk_400_0000MHzMMCM0_nobuf_varphase PORT clk_mem = clk_400_0000MHzMMCM0 PORT clk = clk_200_0000MHzMMCM0 PORT clk_ref = clk_200_0000MHzMMCM0 PORT PD_PSEN = psen PORT PD_PSINCDEC = psincdec PORT PD_PSDONE = psdone END BEGIN axi_datamover PARAMETER INSTANCE = axi_datamover_0 PARAMETER HW_VER = 3.00.a PARAMETER C_INCLUDE_MM2S = 0 PARAMETER C_INCLUDE_S2MM = 1 PARAMETER C_INCLUDE_S2MM_DRE = 0 PARAMETER C_S2MM_BTT_USED = 23 PARAMETER C_S2MM_INCLUDE_SF = 0 PARAMETER C_S2MM_BURST_SIZE = 256 PARAMETER C_S2MM_STSCMD_IS_ASYNC = 1 PARAMETER C_S2MM_STSCMD_FIFO_DEPTH = 4 BUS_INTERFACE M_AXI_S2MM = axi4_0 BUS_INTERFACE S_AXIS_S2MM = master_strm_0_M_AXIS PORT m_axi_s2mm_aclk = clk_100_0000MHzMMCM0 PORT m_axis_s2mm_cmdsts_awclk = axi_datamover_0_m_axis_s2mm_cmdsts_awclk PORT m_axis_s2mm_cmdsts_aresetn = axi_datamover_0_m_axis_s2mm_cmdsts_aresetn PORT s_axis_s2mm_cmd_tvalid = axi_datamover_0_s_axis_s2mm_cmd_tvalid PORT s_axis_s2mm_cmd_tready = axi_datamover_0_s_axis_s2mm_cmd_tready PORT s_axis_s2mm_cmd_tdata = axi_datamover_0_s_axis_s2mm_cmd_tdata PORT m_axis_s2mm_sts_tvalid = axi_datamover_0_m_axis_s2mm_sts_tvalid PORT m_axis_s2mm_sts_tready = axi_datamover_0_m_axis_s2mm_sts_tready PORT m_axis_s2mm_sts_tdata = axi_datamover_0_m_axis_s2mm_sts_tdata PORT m_axis_s2mm_sts_tkeep = axi_datamover_0_m_axis_s2mm_sts_tkeep PORT m_axis_s2mm_sts_tlast = axi_datamover_0_m_axis_s2mm_sts_tlast END BEGIN master_strm PARAMETER INSTANCE = master_strm_0 PARAMETER HW_VER = 1.00.a BUS_INTERFACE M_AXIS = master_strm_0_M_AXIS PORT ACLK = clk_100_0000MHzMMCM0 PORT S_AXIS_TREADY = master_strm_0_S_AXIS_TREADY PORT S_AXIS_TDATA = master_strm_0_S_AXIS_TDATA PORT S_AXIS_TLAST = master_strm_0_S_AXIS_TLAST PORT S_AXIS_TVALID = master_strm_0_S_AXIS_TVALID END результаты функционального моделирования в modelsim на рисунке виден реади на 4 такта далее после наполнения фифо считываю данные датамувером почему сигнал реади (s_axi_s2mm_tready) при появлении сигнала данных (s_axi_s2mm_tvalid) принимает нулевое значение???? То есть при наличии данных и изменении содержимого cmd регистра датамувер пишет после нескольких тактов s_axi_s2mm_tvalid что не готов их принять??? вот картина если я отключаю проверку s_axi_s2mm_tready стрим пакеты идут, но естественно не далее датамувера, т.к. s_axi_s2mm_tready не проверяется....