Aleksei_Rostov

Свой-

Постов

313 -

Зарегистрирован

-

Посещение

Весь контент Aleksei_Rostov

-

Вероятно проще поставить драйвер usb-uart для com порта, чем под jtag, если я вас правильно понял. То есть вы используете jtag для информационного обмена ПК-плата? Как FIFO позволяет увеличить скорость, это же просто буфер?

-

tcl на FPGA

Aleksei_Rostov опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Кто использует при разработке на FPGA tcl скрипты, поделитесь пожалуйста опытом, какие преимущества можно получить за счет использования tcl. Пока обнаружил только преимущество перед gui в виде автоматизации при переносе проектов с одного кристалла на другой. Если можно конкретные примеры. -

2. На Spartan-6 Nexus 3 отладочной плате была перемычка, с помощью которой можно выбирать память под загрузку. На вашей плате посмотрите вот тут описано https://www.xilinx.com/support/documentatio..._kits/ug230.pdf 4. Должен стоять тот регион памяти, в который вы желаете использовать для работы процессора (stack and heap). При этом процессор должен быть подключен к используемой памяти.

-

Если речь идет о первичной обработке радиолокационного сигнала например, то можно делать примерно так: 1. Понижаете по частоте и децимируете входной сигнал. Например, несущая частота входного сигнала 30 МГц (для вашей частоты тактирования - 125 МГц). Опорный сигнал для понижающего преобразования выбираете исходя из ширины спектра входного сигнала. Например, у вас ЛЧМ с девиацией 10 МГц. В этом случае понижаете входной сигнал на 30 МГц. Получается ЛЧМ с переходом через 0 от - 5 до +5 Мгц. Децимируете в 10 раз (т.е. новая частота дискретизации 12.5 МГц). 2. Собираете КИХ фильтр с ИХ зеркальной ЛЧМ на видеочастоте. Собрать можно самому, но без навыков будет сложновато, проще использовать ядра. 3. Наблюдаете отклик на выходе КИХ фильтра, при этом необходима синхронизация по фронту зондирующего сигнала. Относительно него отсчитываете время, когда сигнал на выходе КИХ максимален и пересчитываете в дальность/время. Для верификации используйте modelsim se: в нем есть возможность посмотреть форму сигналов. По организации проекта: моделируете весь тракт в matlab или python. записываете входной сигнал в отдельный файл, который потом будете вычитывать в тестбенче при верификации своего проекта. Как вариант, чтобы весь мусор убрать при децимации, можно CIC фильтром децимировать. Его опять же можно на ядрах собрать.

-

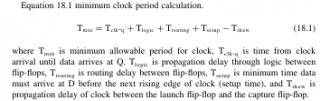

Получаемую тактовую частоту вы уже описали с помощью create_generated_clock Задержка в триггере учитывается при расчете максимально возможной частоты проекта. В данном случае это время Tq clk

-

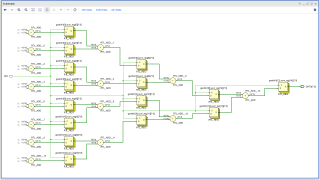

спасибо, только совсем не pipeline)) получилось так reg [7 : 0] sum [0 : N - 1]; integer k; initial begin for (k = 0; k < N; k = k + 1) begin sum[k] = 0; end end assign DATA = sum[N-2]; genvar i; generate for(i = 0; i < N; i = i + 2)begin always@(posedge CLK)begin sum[i >> 1] <= DO[i] + DO[i + 1]; sum[(i >> 1) + N/2] <= sum[i] + sum[i + 1]; end end endgenerate например для N = 16 rtl выглядит: При этом N рассчитывается: function integer clogb2 (input integer depth); begin depth = depth - 1; for(clogb2=0; depth>0; clogb2=clogb2+1) depth = depth >> 1; end endfunction localparam N = clogb2 (M);

-

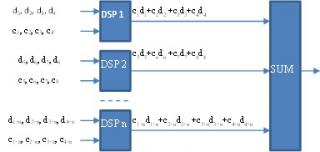

Параметризируемый pipline

Aleksei_Rostov опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! Подскажите пожалуйста, как наиболее компактней описать следующий алгоритм: есть N dsp блоков, которые создаются через generate. На каждый блок умножает суммирует 4 умножения. Далее необходимо просуммировать выходы всех блоков. Структура алгоритма приведена на рисунке: Описание N блоков DSP тривиально: /* * generate multiply and accummulate for layer */ genvar i; generate for (i = 0; i < N; i = i + 1)//H_layer_size begin: DSP DSPkernel i0( .CLK(CLK), .RST(RST), .EN(EN), .DI(DATA_IN[(i+1)*64 - 1 : i*64]), CI(CI[(i+1)*64 - 1 : i*64]), .D_VALID(DSP_VALID[i]), .DO(DO[i])); end endgenerate Каким образом можно описать параметризируемый pipline для сложения выходов DSP блоков? -

Для MAX 10 посмотрите пример https://cloud.altera.com/devstore/platform/...adc-with-linux/ Там и DMA и UART

-

Получается наоборот ): если использую sformatf то выдаёт ошибку: system call sformatf not allowed ... use system verilog mode

-

ROM memory initialization in loop

Aleksei_Rostov опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! Подскажите пожалуйста как можно инициализировать несколько блоков ROM памяти на Verilog'e? Например reg [7 : 0] MyRom [0 : N - 1] genvar i; generate for (i = 0; i < N; i = i + 1) begin initial $readmemh($sformat("Data_block_%0d.txt", i), MyRom, 0, 16); end endgenerate где Data_block_0.txt, Data_block_1.txt, ... , Data_block_N-1.txt - файлы с содержимым каждого блока ROM Синтез данной конструкции проходит. При попытке запустить симуляцию появляется ошибка на sformat -

Добрый день. Кто нибудь запускал EthernetLite на ML605? Возникла необходимость перенести проект с NExys 3 со Spartan 6 на ML605, в котором есть UDP до 100 Мбит.с. На нехусе реализовывал через EthernetLite (MII) и все прекрасно работает. На ML605 (GMII/MII) пакет в трансивер уходит, но сниффером его не вижу (причем с того же нехуса пакеты захватываются). До регистров трансивера достучаться не получается. Не может ли быть проблема при работе EthernetLite c MII через GMII ML605? Переключатели на ML выставлены для GMII/MII интерфейса. С помощью чего попроще можно реализовать обмен на ML605 (axi_ethernet или Virtex 6 Embedded TEMAC)?

-

А для чего тебе Lwip? Как я понял у тебя свое IP ядро, которое ты прикрутил к TriState Ethernet и получаешь обмен данными. Lwip запускал на Stratix, там полный UDP/ARP/TCP/IP на ртосе. У ксайлинка полнгая аналогия https://www.xilinx.com/support/documentatio...es/xapp1026.pdf

-

Привет Алексей! Lwip обращается к памяти, куда отмаппирован контроллер МАК. По идее тебе необходимо посмотреть как с памятью работает Lwip (найти где прописаны указатели на буферы приема/передачи, дополнительные регистры, например для Zynq это ДДР, для Микроблейза/ниоса можно назначать) и сообщить указатель на свой мак контроллер. Я решал немного другую задачу: убирал лишние функции из Lwip, чтобы реализовать UDP точка-точка без RTOS, реализованного в Lwip

-

modelsim

Aleksei_Rostov ответил dsp тема в Среды разработки - обсуждаем САПРы

А можно небольшой примерчик или ссылку? С помощью tcl написание тест бенчей слышал, но никогда не сталкивался ) может действительно так быстрей будет при отладке.... -

modelsim

Aleksei_Rostov ответил dsp тема в Среды разработки - обсуждаем САПРы

Вручную - это с помощью tcl скриптов? -

А что значит "распределённая в SDK память "?

-

У меня была DDR на ML605 и там была проблема записи в определенный регион памяти. я просто исключил его из работы.

-

Статусный реади я вообще в 1 поставил и не трогал больше, только отслеживал sts_tvalid.

-

Из логики тоже автомат делал и в качестве сигнала об успешной транзакции использовал статусный сигнал датамувера.

-

Привет ) Датамувер входит в состав SG DMA и выполняет транзакции на шине данных. Для обмена с ДДР датамувер подходит, но тебе каждый раз прийдется записывать указатели и стартовать датамувер заново, плюс ко всему, насколько я помню, интерфейс для записи указателей у датамувера не акси: я записывал адреса для обмена из логики, а не из СНК. Если ты при обмене для работы с указателями используешь процессор, то SG DMA очень удобное решение с точки зрения работы с указателями на массивы данных в ддр

-

Посмотри SG DMA. Там создаёшь лист дескрипторов с указателями на данные для чтения/записи. Когда нужно быстро было переключаться между разными адресами ддр я его использовал Датамувер это движок sg dma.

-

Да, получилось. Хочу пощупать возможности РТОС и применить в текущем проекте.

-

Алексей, я запустился сначала на zynq на арме, потом и на Спартане 6 на микроблейзе. И там и там базовые проекты с двумя задачками. Осталось теперь ртос под свои нужды подпилить ) Если не разберёшься могу подсказать

-

Проблема в том, как интегрировать FreeRTOS в SDK. Сейчас пытаюсь аппаратную платформу с микроблейзом прописать в исходниках FreeRTOS.

-

Добрый день! Пытаюсь запустить FreeRTOS на спартане 6 самый простой проект для старта типа мигания светодиодами и хелловорд в юарт Использую информацию из данного сайта http://www.freertos.org/Free-RTOS-for-Xili...tan-6-FPGA.html Однако не получается интегрировать FreeRTOS в SDK: постоянно ошибки на отсутствие определенных файлов и тд. Может у кого нибудь получилось запустить ОС на микроблейзе? Какой минимальный набор файлов для FreeRTOS и требования к аппаратной платформе (объем памяти микроблейза, тактовые частоты, наличие перефирии - таймеров, юартов и тд)? Достаточно использовать BSP standalone?