Aleksei_Rostov

Свой-

Постов

313 -

Зарегистрирован

-

Посещение

Весь контент Aleksei_Rostov

-

Собирал в XPS. А потом добавлял в PLAN ahead. У меня задача была обмен данными плата-пк

-

Делал на ПЛИС, ml605 board. Использовал стандартное ядро. На ПК работал с крякнутым windrive.

-

После АЦП фильтр. Его частотная характеристика зависит от разрядности при округлении.

-

Разрядность сигнала на вход я выбирал исходя из разрядности АЦП, отбросив шумящие младшие разряды. В моём случае из 14 я брал только 8. Коэффициенты фильтра рассчитал в матлабе и далее округлил до целого значения в 16ти или 32 разрядной сетке. На выходе округлил значения до требуемой разрядности. Все действия проверял матлабом.

-

vivado 2014.3

Aleksei_Rostov опубликовал тема в Среды разработки - обсуждаем САПРы

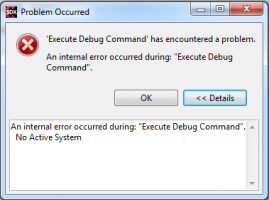

Здравствуйте. Создаю ila core для отладки проекта. Добавляют сигналы, выбираю клок, но найти кнопку implement debug core, по аналогии с plan ahead не могу. Работаю в vivado 2014.3. Либо это глюк среды, либо изменилась идеология создания ядер для отладки chipscope Разобрался. Отладка изменилась по сравнению с PA -

Как успехи с ядром? Получилось запустить?

-

Благодарю что откликнулись. Работаю в модел симе. Поставил 15 квартус. От моделировать так и не смог. Причем для циклона lvds_tx моделируется без проблем! Вообщем если получится дайте пжл знать! Пока собираюсь писать для max 10 сериализатор самостоятельно

-

Скорее да, чем нет)) Пропишите выходы в .ucf

-

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use ieee.std_logic_unsigned.all; library UNISIM; use UNISIM.VComponents.all; entity top is port(clk : in std_logic; rst : in std_logic; -- data_in : in std_logic_vector(7 downto 0); sync_p : out STD_LOGIC; sync_n : out STD_LOGIC; adcdata_p : in STD_LOGIC_VECTOR (13 downto 0); adcdata_n : in STD_LOGIC_VECTOR (13 downto 0); dacA_p : out std_logic_vector(13 downto 0); dacA_n : out std_logic_vector(13 downto 0)); end top; ARCHITECTURE beh OF top IS component convert2diffpairs Port ( diff_p : out STD_LOGIC_VECTOR (13 downto 0); diff_n : out STD_LOGIC_VECTOR (13 downto 0); data_in : in STD_LOGIC_VECTOR (13 downto 0)); end component; begin ------------------------------------------------------------------------------------------------------------------------------ i5 : IBUFDS generic map ( DIFF_TERM => FALSE, IBUF_LOW_PWR => TRUE, IOSTANDARD => "DEFAULT") port map (data_in(0), adcdata_p(0), adcdata_n(0)); i6 : IBUFDS generic map ( DIFF_TERM => FALSE, IBUF_LOW_PWR => TRUE, IOSTANDARD => "DEFAULT") port map (data_in(1), adcdata_p(1), adcdata_n(1)); i7 : IBUFDS generic map ( DIFF_TERM => FALSE, IBUF_LOW_PWR => TRUE, IOSTANDARD => "DEFAULT") port map (data_in(2), adcdata_p(2), adcdata_n(2)); i8 : IBUFDS generic map ( DIFF_TERM => FALSE, IBUF_LOW_PWR => TRUE, IOSTANDARD => "DEFAULT") port map (data_in(3), adcdata_p(3), adcdata_n(3)); i41: convert2diffpairs port map(dacA_p, dacA_n, pr(22 downto 9)); ----------------------------------------------------------------------------------------------------------------------------- end;

-

Работать наверное будет, пробуйте моделировать. Делитель лучше не использовать, а поставить pll модуль. Посмотрите на входы типа enable, или nd фильтра. Не помню как у altera в xilinx они есть. По этим сигналам загружают данные в фильтр. При этом такт может быть и 500 и 100мгц

-

Как Вам удобно будет, главное только чтобы частота тактирования совпадала с частотой при которой Вы рассчитывали коэффициенты фильтра. Если будете использовать 100МГц для 500кгц то на выходе фильтра будут отсчеты повторяться пока не придёт новый отсчёт входного сигнала.

-

electronix.ru/forum/index.php?showtopic=127684 OBUFDS, IBUFDS

-

Altera Soft LVDS MAX 10 FPGA

Aleksei_Rostov опубликовал тема в Работаем с ПЛИС, области применения, выбор

https://www.altera.com/content/dam/altera-w...ug_m10_lvds.pdf UG на данный сериализатор. Может кто нибудь запускал на MAX 10? Пытаюсь промоделировать: добавляю ядро, свой тест бенч, однако ответа от ядра никакого. -

Спасибо, уже разобрался. Получаю диф пары с выходов obufg ,кот потом вывож у в топ модуль и на пины

-

То есть в ucf прописать dac_n и dac_p констрейны, а сигнал топ модуля оставить dac? Или single ended dac сигнал сигнал завести на obufgs и получить на выходе диф пары и в топ модуль выводить _n и _p? Неужели нет возможности в топ модуль вывести только single ended сигнал, а в ucf указать что это дифпары?

-

ml605 diff pair

Aleksei_Rostov опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую! Кто сталкивался, подскажите пжл. как правильно назначать пины для диф пар на ml605 board? В проекте сигнал DDS хочу вывести на FMC разъем. В plan ahead назначаю пины, называю их диф парами, в ucf NET "dac[0]" IOSTANDARD = LVDS_25; NET "dac[1]" IOSTANDARD = LVDS_25; NET "dac[2]" IOSTANDARD = LVDS_25; NET "dac[3]" IOSTANDARD = LVDS_25; NET "clk" IOSTANDARD = LVCMOS25; NET "clk" DRIVE = 12; NET "clk" SLEW = SLOW; NET "clk" LOC = J9; NET "dac[0]" LOC = T33; NET "dac[1]" LOC = U33; NET "dac[2]" LOC = V32; NET "dac[3]" LOC = U31; при сборке ошибка ERROR:Pack:2908 - The I/O component "dac<3>" has an illegal IOSTANDARD value. The IOB component is configured to use single-ended signaling and can not use differential IOSTANDARD value LVDS_25. Two ways to rectify this issue are: 1) Change the IOSTANDARD value to a single-ended standard. 2) Correct the I/O connectivity by instantiating a differential I/O buffer. Как правильно развести выход DDS dac[3:0] на диф пары? -

Выход из ситуации нашел следующий: создал ядро в XPS 14.7, а далее просто мигрировал его в Vivado 2014.3. Теперь все работает)) Но вопрос по созданию собственных ядер с AXI4 в Vivado все равно не ясен...

-

Похожий пост с проблемой при использовании своего IP в Vivado создавал ранее. Кто нибудь пробовал использовать ядра, сгенерированные IP интегратором в Vivado? Сделал проект: Microblaze, bram, cdma, custom IP AXI4 slave. Программа в процессоре выполняет запись данных в custom IP AXI4 slave, затем трансфер данных с помощью CDMA в bram. Собрал проект для Spartan 6 (Nexus 3 board) в XPS 14.7. Проверяю данные через XMD консоль: 1. вычитываю что записал процессором в custom IP AXI4 slave 2. вычитываю что записал CDMA в bram. В XPS все работает отлично. Собираю точно такой же проект в Vivado 2014.3 только для платы с Artix 7. Настройки для микроблейза и остальных ядер аналогичны. Проверяю данные через XMD консоль: 1. вычитываю что записал процессором в custom IP AXI4 slave в консоле получаю connect mb mdm MicroBlaze Processor Configuration : ------------------------------------- Version............................9.4 Optimization.......................Performance Interconnect.......................AXI-LE MMU Type...........................No_MMU No of PC Breakpoints...............1 No of Read Addr/Data Watchpoints...0 No of Write Addr/Data Watchpoints..0 Instruction Cache Support..........off Data Cache Support.................off Exceptions Support................off FPU Support.......................off Hard Divider Support...............off Hard Multiplier Support............off Barrel Shifter Support.............off MSR clr/set Instruction Support....off Compare Instruction Support........off Data Cache Write-back Support......off Fault Tolerance Support............off Stack Protection Support...........off Connected to "mb" target. id = 0 Starting GDB server for "mb" target (id = 0) at TCP port no 1240 XMD% mrd 0x76000000 8 ERROR: Cannot Read from target Processor is stalled at memory access. XMD% В чем может быть проблема? linker script в обоих проектах одинаковы

-

Ядро которое я создаю full AXI4. Опишу проблему более просто: Есть mblz, ddr3, bram, cdma. Пишу код для процессора static u32 *PtrSrcDma = CDMA_BASE + 0x18; static u32 *PtrDstDma = CDMA_BASE + 0x20; static u32 *PtrBttDma = CDMA_BASE + 0x28; #define BTT 128 int main(void){ u8 Buffer[BTT], k = 0; int i; for(i = 0; i < BTT; i++){ k += 1; Buffer[i]=k; } *PtrSrcDma = (u8 *)Buffer; *PtrDstDma = BRAM_BASE; *PtrBttDma = BTT; return 0; } Data, code, stack&heap процессора мапирую в DDR3. Тогда Buffer заполняется в DDR, откуда пересылается в BRAM. После того как код выполнился, проверяю содержимое DDR3, BRAM, регистров CDMA с помощью XMD. Все работает отлично. Создаю и прикручиваю собственное AXI4 full slave IP. Запускаю все тоже самое. Процессор Unable to Stop. и сообщение 0x80000000 адрес DDR контроллера Data, code, stack&heap процессора мапирую в local memory bram. Процессор не виснет, но Buffer через CDMA в BRAM естественно я уже не вычитаю. В чем может быть загвоздка с custom IP?

-

В моем случае проблемы с загрузчиком нет (bootloop заливаю каждый раз). Вопросы возникают с добавлением собственного ядра. Например собрал простой проект: микроблейз, брам, дма, юарт. Проинициализировал массив в памяти процессора, далее отправил с помощью ДМА в БРАМ, считал с помощью ДМА обратно в процессор и вывел массив в консоль Eclipse. Все работает идеально. Далее добавляю к шине собственное IP c AXI 4 интерфейсом. Запускаю в Eclipse прежний проект и он не работает! (в консоле нули). Получается следующее: при добавлении собственного ядра по шине нельзя пересылать burst ами. Как будто она блокируется. При этом почисловое чтение\запись работают. Может вопрос с burst ами. И тогда вышеописанная проблема возникает при попытке инициализации с помощью burst? Может кто-нибудь создавал в Vivado собственные IP slave с AXI 4? В XPS таких проблем не было (((

-

Здравствуйте! Столкнулся с одной проблемой в Vivado 2014.3 Собрал систему с микроблейзом. Добавил собственное ядро (созданное Визардом). В ядро записываю данные процессором, при записи в ядре прибавляется константа, и при считывании процессором данных из ядра наблюдаю сумму константы и исходных данных. Код в процессоре бесконечного цикла не содержит. Запись, чтение и вывод в консоль eclipse Не понятно следующее: При размещении секций памяти микроблейза в lmb_microbl_bram все работает отлично. При размещении в другой памяти (bram, ddr) появляется ошибка и ссылка на адрес в памяти При этом если не использую собственное ядро, то без проблем размещаю Code, Data, Stack&Heap во внутренней bram (не lmb_mblz). Наиболее емким является text микроблейза. Пробовал в linker script менять расположение секций памяти. Data секцию вывожу из lmb_bram работает без проблем, вывожу text -- опять ошибка. Повторюсь: вся проблема только при использовании собственного IP AXI4 слейва без каких либо модификации (за исключением прибавления константы).

-

Бороться то зачем? DDS это обычный алгоритм вычисления функции (в Вашем случае синуса). На крайнем рисунке частота соответствует 1\4 частоты дискретизации (4 точки на период). Увеличьте частоту дискретизации и получите сигнал бОльшей частоты.

-

Большое спаисбо. Как к компьютеру подключали: переходник типа на DVI или VGA? или использовали приставку?

-

Поясните пожалуйста, поподробней. Пока камера линк тёмная тема для меня. У меня задача с платы на кот ПЛИС с lvds по протоколу камера линк передать данные на пк. Как я понял можно купить готовую микро схему сериализатор, куда просто заливаешь кадр, а микросхема раскладывает по camera link base. Какой распространенный коннектор для соединения плата-пк?

-

Пока думаю vhdci коннектор. На него заведу диф пары lvds с платы. На ПК присматриваю готовые приставки под pcie с vhdci коннектором.