BSACPLD

Свой-

Постов

922 -

Зарегистрирован

-

Посещение

-

Победитель дней

5

Весь контент BSACPLD

-

Маловата ПЛИС для AVR ядра. Я пробовал обрезать свой AVR по системе команд, но в MAX 10 меньше 2195 LUT на ядро не получалось. Вам лучше посмотреть в сторону risc16f84. https://github.com/freecores/risc16f84 Он намного меньше AVR.

-

А что нужно подредактировать?

-

Аналоги Samtec

BSACPLD ответил BSACPLD тема в Компоненты

Маркировка как раз взята с их сайта. Это ответные разъёмы для SoM. Санкции. Напрямую работать с нами не хотят. -

Коллеги, подскажите, пожалуйста, в чем может быть проблема. Есть проект в Vivado 2019.2 без каких-либо IP от Xilinx кроме MMCM. Проект нормально собирается и генерится *.mmi файл для памяти объявленной через XPM макрос. Память объявлена следующим образом: xpm_memory_spram #( .ADDR_WIDTH_A ($clog2(DATA_SIZE)), .AUTO_SLEEP_TIME (0), .BYTE_WRITE_WIDTH_A (DATA_WIDTH+DATA_WIDTH/8), .CASCADE_HEIGHT (0), .ECC_MODE ("no_ecc"), .MEMORY_INIT_FILE (INIT_FILE), .MEMORY_INIT_PARAM ("0"), .MEMORY_OPTIMIZATION ("false"), .MEMORY_PRIMITIVE ("block"), .MEMORY_SIZE ((DATA_WIDTH+DATA_WIDTH/8)*DATA_SIZE), .MESSAGE_CONTROL (0), .READ_DATA_WIDTH_A (DATA_WIDTH+DATA_WIDTH/8), .READ_LATENCY_A (2), .READ_RESET_VALUE_A ("0"), .RST_MODE_A ("ASYNC"), .SIM_ASSERT_CHK (0), .USE_MEM_INIT (1), .WAKEUP_TIME ("disable_sleep"), .WRITE_DATA_WIDTH_A (DATA_WIDTH+DATA_WIDTH/8), .WRITE_MODE_A ("no_change") ) program_ram ( .dbiterra (), .douta (q_), .sbiterra (), .addra (address), .clka (clock), .dina (data_), .ena (1'b1), .injectdbiterra (1'b0), .injectsbiterra (1'b0), .regcea (1'b1), .rsta (1'b0), .sleep (1'b0), .wea (wren) ) ; Стоит мне только добавить в проект AXI Quad SPI, как Vivado перестает генерить *.mmi файл при сборке проекта. Память не оптимизируется, проект нормально работает, но нет *.mmi файла... Если запустить write_mem_info -force xc7a_test_eth.mmi то выдается ошибка INFO: [Memdata 28-208] The XPM instance: <axi_qspi_sys_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD_GEN.QSPI_CORE_INTERFACE_I/FIFO_EXISTS.TX_FIFO_II/xpm_fifo_instance.xpm_fifo_async_inst/gnuram_async_fifo.xpm_fifo_base_inst/gen_sdpram.xpm_memory_base_inst> is part of IP: <axi_qspi_sys_0>. This XPM instance will be excluded from the .mmi because updatemem is prohibited from making changes to an XPM that is part of an IP. INFO: [Memdata 28-208] The XPM instance: <axi_qspi_sys_0/U0/NO_DUAL_QUAD_MODE.QSPI_NORMAL/QSPI_LEGACY_MD_GEN.QSPI_CORE_INTERFACE_I/FIFO_EXISTS.RX_FIFO_II/gnuram_async_fifo.xpm_fifo_base_inst/gen_sdpram.xpm_memory_base_inst> is part of IP: <axi_qspi_sys_0>. This XPM instance will be excluded from the .mmi because updatemem is prohibited from making changes to an XPM that is part of an IP. ERROR: [Common 17-69] Command failed: Failed to create the: /home/sergey/Work/DevKit/Artix/xc7a_test_eth/xc7a_test_eth.mmi file. You will not be able to use the updatemem program to update the bitstream with new data. Проблема возникает только после добавления данного IP с включенным FIFO. Если FIFO выключить, то такой проблемы не возникает. В чем может быть дело?

-

Аналоги Samtec

BSACPLD опубликовал тема в Компоненты

Коллеги, подскажите пожалуйста, существуют ли аналоги (клоны) следующих разъёмов: Samtec Razor Beam REF-189016-02, LF-04.0, 100 pins, for all 4x5 SoMs Samtec Razor Beam REF-189017-02, LF-04.0, 60 Pins, for all 4x5 SoMs Есть определенные проблемы с их закупкой... -

Все. Разобрался :)

-

Коллеги, пытаюсь запустить тестбенч с моделью M95XXX с сайта ST. Файлы компилируются без ошибок, но при запуске моделирования получаю кучу ошибок вида: (vopt-7063) Failed to find 'M95XXX_SIM' in hierarchical name 'M95XXX_SIM.M95XXX_Macro_mux.tHLQZ'. Моделирование запускаю через: vsim -gui -voptargs="+acc" work.test ModelSim SE-64 2019.2 Можно ли как-то победить данную проблему?

-

Работа сайта и сервера

BSACPLD ответил admin тема в Новости и обсуждения сайта и форума

Тоже самое. Mint 19.2, Firefox 74.0 -

Дело в том, что в некоторых моделях для симуляции той же DDR, timescale может стоять отличным от того что хотите Вы и он переопределит шаг временного моделирования во всех нижестоящих файлах. Если это память программ, то да. Ее нужно инициализировать. А во всех остальных случаях это лишь потенциальное место для некорректного состояния системы из которого она может никогда не выйти. Вот X как раз и нужны для проверки того как система выходит из некорректных состояний.

-

Так ведь нехороший человек может и не вписать себя в шапку ;) Для таких случаев как раз и есть svn / git и другие системы контроля версий.

-

Правила корректного написания кода

BSACPLD опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Коллеги, существует ли литература / сайты где подробно описаны основные правила хорошего тона при проектировании под FPGA? - что рекомендуется делать. - что не рекомендуется. - за что бить по рукам. Самому как-то лень писать, да и я тоже могу чего-нибудь не знать... Лично для себя я выработал следующий набор правил: - полностью синхронный проект, асинхронные блоки допускаются только если я точно понимаю как это будет работать, как обконстрейнить и их количество должно стремится к нулю. - чем меньше разных тактовых доменов, тем лучше. - для понижения частоты работы блоков использовать clock enable, а не generated clock. - асинхронный сброс при отпускании должен быть синхронизирован с тактовой частотой триггеров которые он сбрасывает. - все переменные объявляются в начале файла, а не по мере их использования. - все переменные объявляются явно. - для знаковых чисел указывается их знаковость (signed). - аппаратно зависимые блоки оборачиваются во врапперы. - никаких LPM в проекте (Altera/Intel). - никакой схематики и устаревших языков (исключение Block Design в Xilinx и QSYS в Altera). - по возможности использовать стандартные шины (APB, AXI, Avalon, Wishbone). - код пишется максимально кроссплатформенным и параметризованным. - в начале файла обязательно налиличе timescale. - все переменные инициализируются X при моделировании. - код проверяется на соответствие стандарту в ModelSim/NCSim. Это так сказать набор правил выработанный за долгие годы работы, но не факт что он полный / достаточный. Хотелось бы почитать подходящую литературу и узнать мнение знающих людей. -

Спасибо.

-

Поставил VX2.7 есть пара вопрсов. - как переключить язык на Английский? В схемном редакторе нашел, а вот Layout никак не могу найти :( - куда пропали кнопки переключения режима выделения Place, Route, Draw и как включить их отображение?

-

Под 1G есть стандартные покупные свичи под тот же CompactPCI, например. https://www.kontron.com/products/boards-and-standard-form-factors/cpci/6u-switches/cp6925.html И там стандартизована разводка (какие дифпары на какие пины). См. стандарт PICMG 2.16. Сам Ethernet обычный 1000Base-T на медь через трасформатор. Я делал платы как раз для такого форм-фактора. PHY был 88E1111. Работало на ура без каких-либо проблем.

-

Да там не только плату, а саму идеологию передачи данных нужно переделывать :(

-

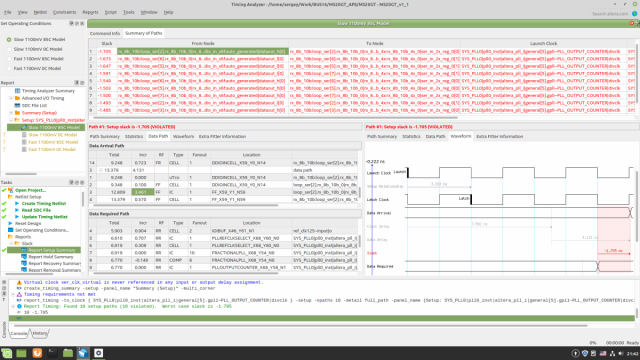

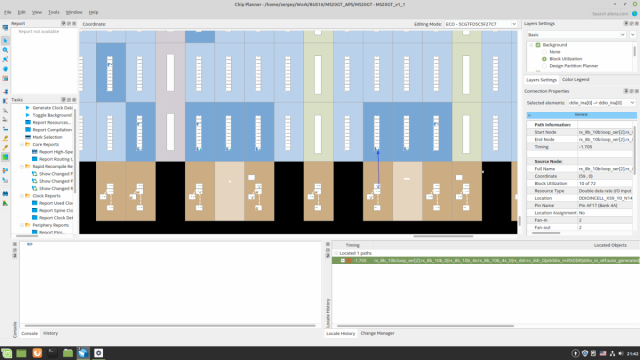

У меня тоже получалось достичь нормальных частот на той же ПЛИС на другом проекте. Разница только в распиновке и количестве каналов. UPD. Да даже на этом проекте. Один из каналов укладывается во времянки (задержка 1,5 нс), а остальные нет (задержка 3,4 нс).

-

Так ведь там PLL для этого отдельный нужен. У меня 8 каналов. Нет у меня столько PLL... Вся загвоздка в том, что нельзя ее подобрать. У разных типов плат подключаемых к данному коммутатору она будет разной. А платы нужно иметь возможность подключать в любом порядке.

-

-

Вивада приятно удивила

BSACPLD ответил des00 тема в Языки проектирования на ПЛИС (FPGA)

Да. Но только если память объявлена как двумерный массив. Если сделать трехмерный, то получим кучу логики. Причем это давняя проблема: https://www.xilinx.com/support/answers/53507.html -

Через Logic Lock? Или есть более красивый способ?

-

Вот отчет с ковейером увеличенным в 3 раза. Ругань на путь от DDIO до триггера. Хотя теперь там их уже 3 подряд и Quartus если бы мог, сделал ретайминг. print.pdf

-

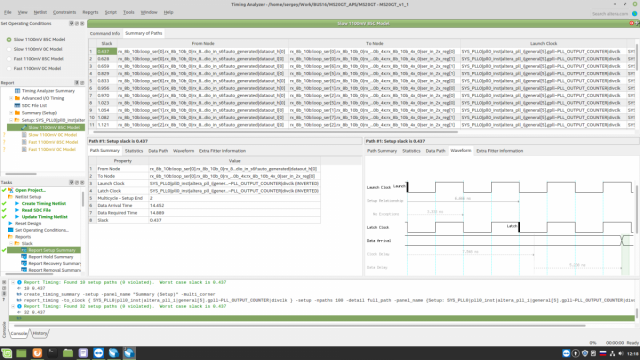

Я пробовал увеличивать длину конвейера - не помогло.

-

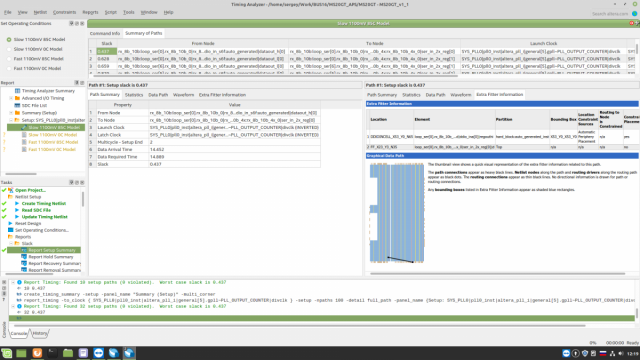

Нет. Это 8 независимых 1-битных линков. Текущий проект это что-то вроде роутера Ethernet в 8 независимых LVDS линков. Вот отчет. На 150МГц собирается без мультициклов. На 300МГц нужно ставить мультицикл 2. print.pdf

-

Так после DDIO сразу идет триггер. Там больше ничего нет. rx_ddr #( .WIDTH (1), .FPGA_VENDOR (FPGA_VENDOR), .DEVICE_FAMILY (DEVICE_FAMILY) ) rx_ddr_0 ( .datain (ser_in), .inclock (clk_sys_2x), .dataout_h (ser_in_2x[0]), .dataout_l (ser_in_2x[1]) ) ; always @(negedge clk_sys_2x) begin ser_in_2x_reg <= ser_in_2x ; end Данные я забираю каждый такт, но частота изменения данных в 4 раза ниже частоты семплирования данных. Высокая частота семплирования нужна чтобы в цифре можно было динамически выбирать момент семплирования данных. Что-то вроде управляемой ЛЗ.

-

Получилось :) Я забыл еще на hold мультицикл прописать :( Вот так нормально собирается: set_multicycle_path -from {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -setup -end 2 set_multicycle_path -from {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_l[0]} -to {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[1]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[0].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[1].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[2].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[3].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[4].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[5].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[6].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1 set_multicycle_path -from {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|rx_ddr:rx_ddr_0|altddio_in:RXDDR|ddio_in_s6f:auto_generated|dataout_h[0]} -to {rx_8b_10b:loop_ser[7].rx_8b_10b_0|rx_8b_10b_4x:rx_8b_10b_4x_0|ser_in_2x_reg[0]} -hold -end 1