ilkz

Участник-

Постов

132 -

Зарегистрирован

-

Посещение

Весь контент ilkz

-

Решено: была ошибка в коде.

-

вопрос по использованию HPS loan io

ilkz опубликовал тема в Среды разработки - обсуждаем САПРы

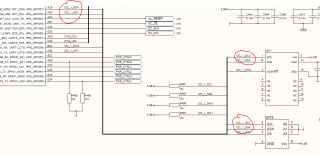

Хочу использовать HPS'ные пины в качестве обычных для i2c контроллера. Для этого настроил в QSys'е нужные мне ноги как LOAN IO и подцепился к ним: inout I2C_1_SDA, inout I2C_1_SCL, assign {loan_out[52], loan_out[51]} = {2'b00}; i2c i2c_inst ( ... .scl_pad_i (loan_in[52]), .scl_padoen_o (~loan_oe[52]), .sda_pad_i (loan_in[51]), .sda_padoen_o (~loan_oe[51]), ) hps hps_inst ( ... .hps_0_h2f_loan_io_in (loan_in), .hps_0_h2f_loan_io_out (loan_out), .hps_0_h2f_loan_io_oe (loan_oe), .hps_io_hps_io_gpio_inst_LOANIO51 (I2C_1_SDA), .hps_io_hps_io_gpio_inst_LOANIO52 (I2C_1_SCL), ) Завел контроллер (который от opencores), но столкнулся со следующей проблемой: при попытке отправить по i2c байт - на выходе плиски ничего нет. Причем, сигналтап показывает что сигналы sda_padoen и scl_padoen формируются нормально, но осциллографом на ногах ничего не вижу. Прелоадер пересобирать обновлять не забывал. Кусок схемы (DD17, DD18 что стоят, что нет - SCL и SDA всегда висят в единице): Самое обидное что если использовать HPS-ный I2C, то всё работает - можно из-под Линукса читать-управлять слейвами. Куда копать? Почему ноги плис могут молчать? -

parameter N=8, parameter pNUM=4 ... input [N*pNUM-1:0] input_bus; wire [N-1:0] bus0=input_bus[0*N +: N]; wire [N-1:0] bus1=input_bus[1*N +: N]; wire [N-1:0] bus2=input_bus[2*N +: N]; wire [N-1:0] bus3=input_bus[3*N +: N]; Только так - объединением в одну общую толстую шину. По-другому - почти что никак. Ограничения верилога. Используйте систем верилог. UPD: А чисто конкатенация будет вот так: parameter N=8, parameter pNUM=4 ... input [N-1:0] bus0, input [N-1:0] bus1, input [N-1:0] bus2, input [N-1:0] bus3, output [N*pNUM-1:0] output_bus ... assign output_bus = {bus3, bus2, bus1, bus0}; Опять же, параметризовать этот ассигн в рамках верилога - невозможно.

-

см личку )

-

Скорее всего дело в пайке, да. Рекомендую понаблюдать TopJTAG-ом (вытаксиваете ноги в нем на времянку и наблюдаете, давите на плис и т.п.). У меня было похожее: ПЛИСина не заводится вообще -- перепаяли, заводится частично -- перепаяли, заводится еще больше -- перепаяли вот прям вообще вдумчиво - завелась норм. Симптоматика была такой: частичная работа (либо только ПЛИС, либо HPS и тот частично), либо если пальцем нажать на чип то он оживает, либо он оживает сам после долгой запитки и прогрева, а потом снова отмирает (похоже на перемыкание шаров при тепловом расширении).

-

Силиконовые шайбочки решат проблему

-

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Up. Освежу тему. Мы занимаемся разработкой проводного и беспроводного телеком-оборудования: мультиплексоры (STM-1/4/16, E1, Ethernet-10/100/1G), радиорелейных станций связи (для Ethernet 1G), а также ряда других проектов (например, системы учета с применением беспроводных технологий типа LoRa). Разрабатываем полностью с нуля свою схемотехнику, нижнее и верхнее ПО. В телекоме используем ПЛИС Altera Cyclone III/IV/V, включая чипы с SoC. К нам в команду требуется программист ПЛИС, который "подхватит" существующие наработки и продолжит их развитие совсемстно с командой. В основном задача проектов ПЛИС - распаковка потоков STM/E1/Ethernet на каналы, перекоммутация их друг с другом и упаковка обратно. В проекте радиорелейной связи есть ЦОС радиоканала, можно подхватить и это направление. Другие проекты построены на процессорах STM и т.п. Общие условия работы: полностью белая з/п, график 5/2, отпуск 32 календарных дня, командировок нет (либо крайне редко), весьма уютный офис, гибкий рабочий график, молодой коллектив. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Первое. Вот допустим мне надо перекинуть, например, резюк MSEL для смены конфигурации плис. И есть два варианта - идти отвлекать монтажника от пайки какой-нибудь вязанки капризных LGA-шных микросхем ради моей маааленькой хотелки или потратить три (3, Карл!) минуты на решение этой задачки самостоятельно. Ну или подцепить проводок, чтоб осциллографом поудобнее подключиться. Тоже нести монтажнику? Не, конечно, если он сейчас свободен, то я отнесу ему, но во всех остальных случаях - имхо, быстрее и эффективнее сделать самому. Ну либо если человек действительно не умеет в паяльник (бывает и такое, ничего страшного). Второе. Я с огромным удовольствием возьму специалиста и без опыта пайки и работы с измериловкой, если он хорошо разбирается в разработке под плис. Вот вообще не проблема. Тем более что есть миллион интересных задач под разработку ПЛИС, которые, скажем так, сидят глубоко внутри ПЛИС, не затрагивая внешний мир. Ему на 100% хватит сигналтапа, system console и issp для того чтоб эффективно отлаживаться в железе, не лезя во внешний мир. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Актуально. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Друзья, мы расширяемся и к нам в команду нужны еще ПЛИСеры. Направление - проводной телеком, разработка алгоритмов коммутации, маршрутизации, управления. Требования к кандидату в целом такие же, за некоторыми исключениями (не нужен ЦОС и embed): • Опыт реальной работы - от 3 лет • Глубокий опыт работы с ПЛИС Altera, Quartus II, Modelsim (или любым другим симулятором) • Сильно приветствуются знания в области телекома (STM, E1, Ethernet и подобные штуки) • Умение оптимизировать потребляемые ресурсы ПЛИС • Умение работать с SignalTap • Умение писать констрейны • Создание тестбенчей • Знание Verilog/System Verilog • Работа с системами контроля версий (SVN, HG, Git) • Умение разбираться в чужом коде и схематике • Умение использовать измерительную аппаратуру (логический анализатор, осциллограф и т.п.) и подпаять-отпаять пару резисторов Дополнительные навыки, которые будут плюсом: • Знание System Verilog • Умение автоматизировать сборку ПЛИС (tcl скриптинг) • Опыт работы с System Console, QSys, HPS • Верификация и анализ покрытия • Прямые руки в плане припаять-отпаять что-нибудь в процессе отладки • Навыки командной работы Территориально - Москва, недалеко от Нагатинской. З/П полностью белая, соцпакет стандартный, хотя есть и пара приятных бонусов в виде увеличенного отпуска и достаточно гибкого графика. Уровень зп хороший, согласуется индивиуально, поскольку напрямую зависит от опыта кандидата. Поэтому никаких цифр здесь озвучивать не буду. Если Вы подающий надежды студент с мозгами, который не вафлит задачи, а хочет и старается их выполнять, то возможно обучение в процессе. Также возможно содействие в продвижении аспирантской деятельности. Все дальнейшие подробности – в личной беседе. Почта для связи: ilkz yandex ru, также можно писать сюда в личку. Прошу не флудить и отвечать по делу. -

Я очень надеюсь, что людей у вас тоже как-то защищают от этой гадости...

-

CyUSB под QT

ilkz ответил ilkz тема в В помощь начинающему

Всем спасибо за помощь, заработало. Нужно было подключить следующие либы (в особенности, последнюю): CyAPI.lib user32.lib setupapi.lib legacy_stdio_definitions.lib Помогла эта ссылка: http://www.cypress.com/forum/usb-high-spee...cyapilib-vs2015 -

CyUSB под QT

ilkz ответил ilkz тема в В помощь начинающему

В виде отдельного проекта работает и под VS2010 и под VS2015. Из-под Qt (ага, теперь пишу правильно :maniac: ) пробовали с VS2015 - не хочет. Пробовали от 0 до 255 :) Тоже толку ноль... DeviceCount всегда дает 1, если устройство подключено. -

CyUSB под QT

ilkz ответил ilkz тема в В помощь начинающему

Я конечно не настаиваю, но как мне кажется, из контекста вопроса понятно о чем идет речь. И давайте не будем разводить оффтоп. -

CyUSB под QT

ilkz ответил ilkz тема в В помощь начинающему

Причем тут QuickTime? Я говорю о QT Creator ))) -

CyUSB под QT

ilkz опубликовал тема в В помощь начинающему

Добрый день. Впрсо имею я. Не получается под QT открыть устройство функцией USBDevice->Open(0). Если полезть в недра, то почему-то не формируется DevPath - он всегда равен "/", хотя должен быть большим и длинным с vid/pid и прочими штуками. Код такой: ... pUSBDevice = new CCyUSBDevice(); int deviceCount = pUSBDevice->DeviceCount(); // <- отрабатывает нормально pUSBDevice->Open(0) // <- вот тут, если полезть внутрь Open, то DevPath почему-то оказывается пустой ... Такое поведение и с компилятором Mingw и с VS2015. Тот же самый код, но собранный в виде проекта VS, работает нормально. Что я не докрутил или куда хотя бы копать для решения проблемы? Гугл молчит по данному вопросу. Спасибо. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Вакансия закрыта. Спасибо всем за отклики. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

К сожалению, уже не могу :) Ограничение форума. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Возможно, я в вопросах PCI не спец. Но если все так, как Вы говорите, то задача сильно упрощается. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

1. Как я сказал выше, если искомый человек сможет корректно составить требования к драйверу и спецификацию на свой плисовый модуль, то драйвер можно будет сделать совместно. 2. Всегда считал, считаю и буду считать что плисер должен уметь в паяльник, осциллограф, генератор и, возможно, спектроанализатор. Ничего сложного в этом нет. И никто в здравом уме не будет заставлять плисера паять (и уж тем более разводить) какие-либо платы-схемы, тем более - высокоскоростные. К тому же, моя фраза в самом начале "припаять-отпаять что-нибудь", как мне кажется, прямо говорит о навыках припаять-отпаять провод-другой (например, чтобы зацепиться осциллографом или питание пробросить или кнопку/светодиод подпаять), а не BGA-шный Stratix. Для серьезной пайки у нас есть монтажники. 3. Я четко разграничил основные требования (совпадение по которым ожидается на не менее 80%) и дополнительные (то есть - необязательные), отсутствие которых совершенно некритично. 4. ЦОС и ПЛИС так и вообще почти созданы друг для друга. Тем более, что я также написал уровень владения ЦОС (это не Витерби и прочие LDPC, а вполне базовые алгоритмы, которые во многом можно прекрасно и довольно быстро смоделировать в том же матлабе). 5. И да, я ищу человека, который сможет разработать прошивку (набор прошивок) ПЛИС, содержащую как интерфейсную часть, так и математическую. Написать тестбенчи на нее. Отладить ее в железе совместно с программистами-системщиками. Вполне реальные пожелания. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Мне кажется, что работа с шиной PCI все-таки подразумевает определенное знакомство с тем как устроен и работает драйвер в ОС. Недостаточно ведь просто написать корку под ПЛИС - нужно ее еще как минимум отладить, да и научить работать в системе неплохо бы. А без драйверов этого не сделаешь. Добавлю, что с ПК-шной стороны у нас есть программисты, следовательно, по данному вопросу возможна совместная работа, что несколько упрощает задачу. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz ответил ilkz тема в Предлагаю работу

Предложение все еще актуально. -

Инжернер ПЛИС и немного микроконтроллерщик

ilkz опубликовал тема в Предлагаю работу

Коллеги, приветствую. В команду по разработке высокотехнологичного оборудования сбора и анализа данных требуется разработчик ПЛИС. Первоочередная задача – подружить компьютер с существующей платой сбора данных, имеющей USB 2.0 (FX2LP) и PCI(PLX PCI9054)-интерфейс. Далее – обвязка проекта относительно несложной математикой (фильтрация, предобработка), перенос части математики из ПК в ПЛИС, а также непосредственное участие в дальнейшем развитии платы. Естественно, придется написать драйвер для работы с PCI по Win. Ключевые требования к кандидату: • Знания в области ЦОС (цифровая фильтрация, преобразование Гильберта, преобразование Фурье и т.п.) • Опыт реальной работы - желательно от 3 лет • Глубокий опыт работы с ПЛИС Cyclone III, САПР Quartus II, Modelsim (или любым другим симулятором) • Умение оптимизировать потребляемые ресурсы ПЛИС • Знание принципов работы высокоскоростных интерфейсов и протоколов: USB 2.0, PCI/PCIE, LVDS (до 500Мбит/с), DDR, Ethernet (может потребоваться в дальнейшем) • Умение работать с SignalTap • Умение писать констрейны • Создание тестбенчей • Знание Verilog • Работа с системами контроля версий (SVN, HG, Git, etc) • Умение разбираться в чужом коде (кода под проект по плате сбора данных пока нет, но есть смежные проекты и люди где можно что-нибудь спросить/подсмотреть) • Умение использовать измерительную аппаратуру (логический анализатор, осциллограф и т.п.) Дополнительные навыки, которые будут плюсом: • Знание System Verilog • Умение автоматизировать сборку ПЛИС • Верификация и анализ покрытия • Умение писать драйвера (Windows) под железо • Прямые руки в плане припаять-отпаять что-нибудь в процессе отладки • Навыки командной работы (навыки управления командой – ещё лучше) Все дальнейшие подробности – в личной беседе. Почта для связи: ilkz yandex ru, также можно писать сюда в личку. -

Какого рода проекты? Интерфейсы, математика, управление, что-то еще?

-

AD7799

ilkz ответил ilkz тема в В помощь начинающему

Ребята, все нормально: обнаружилась ошибка в разводке - вход не был подключен. :) Спасибо всем за помощь!