drozel

Свой-

Постов

107 -

Зарегистрирован

-

Посещение

Весь контент drozel

-

Выбор протокола

drozel ответил drozel тема в Wireless/Optic

А почему без координатора сеть превращается в анархию? Я этот момент не совсем понимаю -

Выбор протокола

drozel ответил drozel тема в Wireless/Optic

А можете в двух словах чуть более подробнее? Или ссылку, если есть чего понятного почитать. Пока каша в голове. Если говорить про динамический координатор, возможно ли такое на ZigBee? Готовое рабочее решение -

Выбор протокола

drozel опубликовал тема в Wireless/Optic

Поставим цель: Есть N равнозначных устройств: никаких выделенных координаторов и т.д. Все эти устройства каким-то образом настраиваются: указывается некий SSID, прогружаются одним ключем, настраиваютсян а один канал - не суть. Все имеют уникальный MAC. Любое из устройств может показать список МАКов, которые он видит в пределах действия сети (идеально, если бы каждый при этом расширял область действия сети, выступая репитером (хопом)). Любому доступному MAC в радиусе действия можно послать пакет и получить ответ. Пропускная способность - не критична, команды короткие. Теперь ближе к реализации: Есть CC2538. Вопросы: Помогите с выбором стека/протокола. ZigBee позволяет строить mesh, но вся дока, которую я видел, говорит о том, что должен быть отдельный координатор (не подходит). В принципе, рассмотрю возможность написание своего стека, но пока не вырисовывается картина. Надеюсь, поможете -

А если взять шире, но использовать бит? Объем то не супер большой требуете..

-

Снова вопрос по qtouch к тем, кто пользовался: удалось ли добиться приемлемой частоты опроса сенсоров? У меня qt_measure_sensors(), которая в примерах вызывается по тику таймера каждые 25мс, выполняется больше сотни милисекунд на atmega 328 с клоком 4МГц. Т.е. добиться частоты обновления состояния кнопок порядка хотя бы сотни милисекунд - нереально, т.к. для обнаружения нажатия функция qt_measure_sensors() вызывается несколько раз.

-

Вот и именно. Вообще не понимаю, откуда растут ноги у ассемблерного стартапа: вроде даже сам ARM поставляет сишный стартап для ядра. Даже если нет, написать структуру на сях - делов на 20 минут. Заодно обработчики дефолтные можно накидать, используя прелести __weak

-

Вот и мне так показалось Теперь убедился, что мне не показалось, и лучшего способа, похоже, и вправду нет( Жаль, редактор крутейший, а с настройками сущий ад

-

понял. А чего делать с настройками среды? Он, как я понял, даже цветовую схему хранит в воркспейсе.

-

Помогите с Eclipse+SVN (GIT). Вот есть проект для ARM на IAR. Создаю структуру папок: soft ---mcu ------prj --------IAR -----------workspace -----------project ------src ---------some_c_files ------inc ---------some_h_files И все это в репозиторий. В workspace хранится список проектов (почти всегда один, хотя бывает и 2, если программа из 2 прошивок - загрузчик например есть и обновляемая прошивка) Теперь переходим на eclipce. Он в workspace хранит кучу всякой гадости - тут тебе и настройки программы (ладно, хрен с ним, закоммитим), и куча папок плагинов. Поправил один исходник - svn тут же ругается на гору missing и modified. Как предполагается использовать его с svn? Держать проект и воркспейс вне репы? А где? Я привык, что в репе есть все, готовое к работе - через полгода вернусь к проекту - checkout и работаем. А тут я что, достану исходники, создам воркспейс, настрою его, создам проект, сделаю импорт из файловой системы? Так? Где я не прав? Направьте на путь истинный

-

Да мне не мешают, наоборот. Чего тут объяснять то.. Шифратор bin to BCD для часов на логике, написанный в лоб. Ни одной защелки там не будет, сплошная комбинационная логика.

-

Блин, регистры не регистры. В коде это регистры, после синтеза регистров не будет, они сделаны для возможности присвоения в always, как сказал masics.

-

Дык это же bin->BCD, 3 курс университета.. Я, помнится, в то время, его на верилоге через деление описывал) Интересно скормить синтезатору, наверняка можно и более компактно описать. Ну, хотя бы вынести кусок в модуль, ведь секундный и минутный - одинаковые

-

А как Вы "делаете в обычном усарте"? В прервании в буфер складываете? Ну так и тут так сделайте

-

А можно ли для этих целей использовать Modelsim? Скармливать ему sdf и нетлист из design compiler? Уступает ли этот метод тому же vcs?

-

Как мне сказали, работает на сусе. Правда, возможно, на более старой версии. Думаете, без шансов?

-

Проблема с Synopsys

drozel опубликовал тема в Разработка цифровых, аналоговых, аналого-цифровых ИС

Пытаюсь скомпилировать исходник для симуляции: vcs ../src/module.v -sverilog -full64 +v2k -debug_all drozel@PC:/media/sf_shareFolder/work/verilog/sim> /vcs ../src/module.v -sverilog -full64 +v2k -debug_all Warning-[LNX_OS_VERUN] Unsupported Linux version Linux version 'openSUSE 42.1 (x86_64) VERSION = 42.1 CODENAME = Malachite # /etc/SuSE-release is deprecated and will be removed in the future, use /etc/os-release instead' is not supported on 'x86_64' officially, assuming linux compatibility by default. Set VCS_ARCH_OVERRIDE to linux or suse32 to override. Please refer to release notes for information on supported platforms. Warning-[LINX_KRNL] Unsupported Linux kernel Linux kernel '4.1.13-5-default' is not supported. Supported versions are 2.4* or 2.6*. Chronologic VCS (TM) Version G-2012.09_Full64 -- Tue Jan 19 14:06:20 2016 Copyright (c) 1991-2012 by Synopsys Inc. ALL RIGHTS RESERVED This program is proprietary and confidential information of Synopsys Inc. and may be used and disclosed only as authorized in a license agreement controlling such use and disclosure. Parsing design file '../src/module.v' Top Level Modules: module No TimeScale specified Starting vcs inline pass... 2 modules and 0 UDP read. However, due to incremental compilation, no re-compilation is necessary. Assertion failed "rename(tmp_file, out_file) == 0" at line 833 in file cgmop.c Command line: /soft/vcs/amd64/bin/cgmop1 -pic -gen_obj rmapats.m rmapats_mop.o --- Stack trace follows: sh: 26924: command not found No context available filelist.hsopt:2: recipe for target 'rmapats_mop.o' failed make: *** [rmapats_mop.o] Error 255 Make exited with status 2 CPU time: .080 seconds to compile + 0 seconds to elab + .008 seconds to link Кто знает, в чем может быть проблема? OS: OpenSUSE 13.2 x64 Пробовал запускать и 32 и 64-битный vcs - ошибка одна -

Сейчас считается приличным иметь веб-версию, клиент для android+IOS. По желанию, еще Windows 10.

-

Жаль, тут нет репутации пользователей, как на ixbt или 4pda. Очень полезная вещь. Спасибо :rolleyes:

-

Попробовал. Ожидаемо уменьшилось кол-во гейтов: теперь на входе каждого регистра-счетчика - по мультиплексору 2 в 1. На вход управления приходит mode[1]. Т.е. по сравнению с предыдущим вариантом просто упростилась логика определения условия остановки. Спасибо за идею. Я на FPGA частенько напарывался на такую глупую ошибку: есть готовый модуль с шиной на выходе module mod1( input [7:0]a, output c, output [7:0]b); используешь его в проекте, пишешь mod1 mod( .a(a), .c(c), .b(b); а a,b,c - не объявлены заранее. Синтезатор создает их сам, только все шириной 1 бит. Потом только в RTL или в симуляции докапываешься, в чем дело. Тогда я принял за правило писать .b(b[7:0]) - так, если она не объявлена, синтезатор хотя бы ругнется. Потом пришел более опытный товарищ (гораздо более опытный) и сказал, что такое написание бъет по глазам - будто бы я только часть шины b подключил к этому блоку.

-

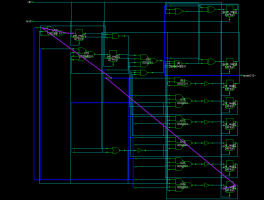

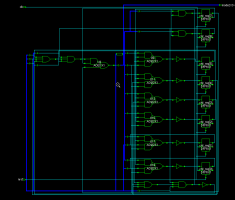

module top ( input clk, input nrst, output reg [1:0]mode ); reg [7:0]cnt; always @(posedge clk, negedge nrst) begin if (~nrst) begin cnt <= 0; mode <= 0; end else begin if(cnt<200) cnt <= cnt + 1; if(cnt==99 || cnt==199) mode <= mode+1; end end endmodule Вы говорили про тайминги. Я не до конца понял, что Вы имели ввиду, посмотрел отчет по slack. У варианта 2 они чуть лучше, кроме одного пути: младший бит cnt - сумматор - старший бит через логику. К слову про глитчи: предположим, что на выходе mode еще одна защелка, которая защелкивает по окончанию счета. Вариант 2: Вариант 1:

-

Хорошее замечание, спасибо. Кстати, отловил еще одно отличие: в синхронном примере нет насыщения счетчика. После того, как добавил, площадь второго варианта стала почти в 1.5 раза больше. Т.е. синхронный более накладный. Видимо, все таки синтезер очень сильно упрощает логику сравнения, даже если речь идет о диапазонах. Еще, в синхронном отстал один critical path.

-

1. Сорри, делал второпях, не суть, просто пример. Поправил. 2. Опять же недоглядел. Поправил. 3. Опять суть в константах, не критично. Спасибо, из вашего ответа следует "и так и так можно делать, т.к. второй вариант более экономичен, можно и нужно делать по второму варианту"?

-

Особенности логики

drozel опубликовал тема в Разработка цифровых, аналоговых, аналого-цифровых ИС

Добрый день. Пытаюсь адаптировать свой verilog, проверенный на fpga, для реализации в кремнии. Периодически возникают те или иные вопросы, ответ на которые хочется найти тут, у спецов. Первый вопрос: Представим 8-разрядный счетчик, считающий по клоку. По достижению им числа 100 нужно переключиться в режим 1, по достижению 200 - в режим 2 и остаться в нем до сброса. Раньше, в ПЛИС (в связи с избыточностью ячеек), я бы сделал так: reg [7:0]cnt; always @(posedge clk, negedge nrst) begin if (~nrst) cnt <= 0; else begin if(cnt<200) cnt <=cnt + 1'b1; end end always @* begin if(cnt<100) mode <= 0; else if(cnt <200) mode <= 1; else mode <= 2; end Теперь, представляю, во что выльется этот код: синтезатор реализует 3 компаратора (причем для определения диапазона) из простых элементов для декодирования значения счетчика. Думаю, как упростить схему. Рождается код: reg [7:0]cnt; always @(posedge clk, negedge nrst) begin if (~nrst) begin cnt <= 0; mode <= 0; end else begin cnt <= cnt+1; if(cnt==100 || cnt==200) mode <= mode+1; end end Тут уже компарирование не диапазона, а конкретных значений, зато логика mode становится синхронной. Проверил в DC - действительно, экономия по площади и кол-ву ячеек - почти в 2 раза. Не имеет ли второй вариант каких-то подводных камней? -

Поясните? Я тут недавно маялс с ZLP, читал спеи, про это слышу впервые, может быть, корень и моих проблем -тут

-

Вопросы начинающих 2015г

drozel ответил Uladzimir тема в Altium Designer, DXP, Protel

Подскажите, когда на схеме выделяешь компонент, в окне PCB происходит зуммирование и выделение соответствующего футпринта. Можно ли провернуть это в обратную сторону? Т.е. выделять футпринт на PCB и получать отцентрированный символ на схеме?