-

Постов

1 039 -

Зарегистрирован

-

Посещение

Весь контент arhiv6

-

Сохранить серийный номер в памяти.

arhiv6 ответил jenya7 тема в ARM, 32bit

Jenya7, да, можно так делать. Единственный минус - для записи участок памяти надо стереть, стирается она секторами по 4кб. Например, можно использовать последний сектор flash хранения номера. Подробнее тут. -

Прошу покритиковать схему..

arhiv6 ответил sanya221 тема в RF & Microwave Design

К сожаления, Александр Анатольевич скончался в июле прошлого года. -

Методики расчета цепей согласования

arhiv6 ответил arhiv6 тема в RF & Microwave Design

Действительно, такая глупая ошибка. Вчера весь вечер просидел, несколько раз проверил - и не увидел... Спасибо! -

Методики расчета цепей согласования

arhiv6 ответил arhiv6 тема в RF & Microwave Design

Я же пишу, что мне не готовая программа нужна, а методика. Есть программа Qucs. Бесплатная, с открытыми исходниками. Я ей пользуюсь, при этом не заплатил за неё ни копейки. Одна из форм благодарности - поучаствовать в разработке (что и делаю по мере своих возможностей). Сейчас появилась идея улучшить расчет согласующих цепей (такая функция в программе есть но сделана на очень примитивном уровне). Поэтому, повторю, вопрос не в том, какую выбрать программу, а в том, где найти алгоритм расчёта или найти, в чём ошибка при расчёте по статье из первого поста. -

Методики расчета цепей согласования

arhiv6 ответил arhiv6 тема в RF & Microwave Design

Aner, программу видел, но ёе исходников нет. Вопрос не в том, какую выбрать программу, а в том, где найти алгоритм расчёта или найти, в чём ошибка при расчёте по статье из первого поста. -

Методики расчета цепей согласования

arhiv6 ответил arhiv6 тема в RF & Microwave Design

Это всё платно. Я для проекта Qucs (open source симулятор) сделать хочу. Там есть функция согласования, совсем простенькая, хочу функционала добавить. -

Методики расчета цепей согласования

arhiv6 опубликовал тема в RF & Microwave Design

Добрый день. Я хочу написать программу-калькулятор, которую можно будет использовать для автоматизации расчёта согласующих цепей. Поискал методики, нашёл статью "Аналитический расчет согласующих цепей лестничной структуры"276.pdfАлгоритм, формулы вроде расписаны... но уже на первом примере результат расчета не сходится с моделированием. Например, цепь, изображённая на рисунке 1.а, F=100МГц, Rг=50, Rн=75, Lн=10нГн Расчёт: Частота w0= 2*pi*F=628*10^6 Т.к. Rн>Rг, то r=75/50=1.5 g1=sqrt(r-1)=sqrt(0.5)=0.707 g2=sqrt(r-1)/r=0.707/1.5=0.47 C=g1/(w0*Rг)=0.707/(50*628*10^6)=22.5пФ L=g2*Rг/w0-Lн=0.47*50/(628*10^6)-10нГ=37.5нГ-10нГ=27.5нГ Но импеданс цепи, изображенной на рисунке 1.а с такими номиналами на частоте 100МГц даёт значение 47.6-j*40.6, т.е. цепь не согласованна. Я что-то не так считаю или в статье ошибка? Или где можно найти расписанные методики расчёта? -

Выпрямители и сглаживающие фильтры

arhiv6 ответил James D. тема в В помощь начинающему

Эпюры напряжений на выходе мостовой схемы и схемы со средней точкой будут идентичны. Соответственно, пульсации у них будут одинаковы. -

Выпрямители и сглаживающие фильтры

arhiv6 ответил James D. тема в В помощь начинающему

Двухполупериодный - это мостовой или со средней точкой. Схемы разные, а смысл тот-же - для выпрямления использются 2 полупериода, формулы для расчёта у них одинаковые. Для однопулопериодного средняя эдс равна Uпик/pi. Коэффициент пульсаций 3.14. Для двухулопериодного средняя эдс равна 2*Uпик/pi. Коэффициент пульсаций 1.57. Вывод этих значений для всех трёх схем (однополупериодный, мост Гретца, двухполупериодный со средней точкой) есть в википедии. -

Поставлю вопрос по-другому: почему для этих контроллеров (например, тот же FAN6208) подчёркивают, что они применимы для полумостовых схем именно в резонансных топологиях? И не приводят примера использования в нерезонансной топологии? Если я буду использовать этот контроллер в нерезонансной схеме, точно проблем не будет (интересен опыт практического применения)?

-

Если всё так просто, то почему я не могу найти реального примера такого выпрямитель для полумоста (не резонансного)?

-

"Всё есть"... А можно примеры?

-

Синхронный выпрямитель для полумоста

arhiv6 опубликовал тема в Силовая Преобразовательная Техника

Добрый день. У многих производителей (IRF, Farchild и т.д.) есть готовые микросхемы для построения синхронных выпрямителей следующих топологий: прямоходов, обратноходов и резонансных (LLC) полумостов. А есть в природе такие же микросхемы, но для обычной полумостовой топологии? Или схемы таких выпрямителей на "рассыпухе"? -

Правила монтажа QFN

arhiv6 ответил RA9YSS тема в Пайка и монтаж

Где вы такой способ видели? Возможно, для домашних поделок сгодится (как раз для пайки паяльником). Но даже для домашней поделки я так делать не стал. А для увеличения теплоотвода используют via под центральным падом, соединённые с полигонами на нижнем и внутренних слоях (примеры можете посмотреть в пункте 2.4 Thermal Vias этого документа). -

Докуметация по СВЧ-технике

arhiv6 ответил KuzmaPrytkov тема в RF & Microwave Design

Ищу книгу "Envelope Tracking Power Amplifiers for Wireless Communications" Автор: Zhancang Wang", 2014год. -

Похоже CPLD придётся использовать. На verilog алгоритм написал (оказывается, это не сложно). В симуляторе (iverilog+vvp) проверил - работает. module mod_logic( input wire clock, input wire [3:0]in_a, input wire [3:0]in_b, output reg [3:0]out_c ); integer i=0,shift=0,position=0; initial out_c = 4'b0001; always @(posedge clock ) begin shift=0; // проверка if((in_a != 4'b0000) & (in_b != 4'b0000)) out_c <= 4'b1000; // обработка ошибок else begin // определяем позицию на выходе for(i=0; i<4; i=i+1) begin if(out_c[i]) position=i+1; end // считаем сдвиг в +, если это возможно if((in_a != 4'b0000) & (out_c != 4'b1000)) begin for(i=0; i<4; i=i+1) begin if(in_a[i]) shift=shift+1; end // сдвигаем if (shift > (4-position)) out_c <= 4'b1000; else out_c <= out_c << shift; end // считаем сдвиг в -, если это возможно if((in_b != 4'b0000) & (out_c != 4'b0001)) begin for(i=0; i<4; i=i+1) begin if(in_b[i]) shift=shift+1; end // сдвигаем if (shift > (position-1)) out_c <= 4'b0001; else out_c <= out_c >> shift; end end //$display("position %d",position); //$display("shift %d",shift); end endmodule Один только минус - для симулирования всей схемы (в основном аналоговые компоненты), в которой эта CPLD будет стоять, нужен какой-то mixed-mode симулятор (spice+HDL(Verilog)). Обычную логику многие spice симуляторы умеют моделировать, а вот которые умеют файлы verilog подключать - не видел.

-

Ради 12 ножек? + её программировать ещё надо, а для плис ни разу не писал прошивок. Хочется всё-таки на логике попытаться собрать.

-

Реализация алгоритма на логически элементах

arhiv6 опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Потребовалось реализовать следующую схему: Входов 9 штук: clk + a1,a2,a3,a4,b1,b2,b3,b4. Выходов 5 штук c1,c2,c3,c4,c5. Всегда только один из выходов находится в лог 1 (после подачи питания по умолчанию это выход с1). По фронту на входе clk состояние на выходе меняется по следующему алгоритму (перечислены все возможные состояния на входах): - на на всех входах лог 0 - состояние на выходе не меняется. - a1 в лог 1 - на выходе произойдёт сдвиг на +1. - a1,a2 в лог 1 - на выходе произойдёт сдвиг на +2. - a1,a2,a3 в лог 1 - на выходе произойдёт сдвиг на +3. - a1,a2,a3,a4 в лог 1 - на выходе произойдёт сдвиг на +4. - b1 в лог 1 - на выходе произойдёт сдвиг на -1. - b1,b2 в лог 1 - на выходе произойдёт сдвиг на -2. - b1,b2,b3 в лог 1 - на выходе произойдёт сдвиг на -3. - b1,b2,b3,b4 в лог 1 - на выходе произойдёт сдвиг на -4. Сдвиг на +1 означает, что , например, если лог 1 было на выходе с3, то по фронту на clk на выходе с3 станет лог 0, а на выходе с4 - лог1. Сдвиг нужен без переноса - если, например, лог 1 было на выходе с5, любой сдвиг в + ничего на выходе не изменит. Вопрос: на каких логически микросхемах (сдвиговые регистры, счётчики и т.п.) можно реализовать такую схему? (микроконтроллер не предлагать :) ) -

В тему - можете почитать статью "Как (не)надо развязывать высокоскоростные операционные усилители", там тема расстановки конденсаторов затрагивается. Разумеется, тоже не в пользу соединения через виа.

-

Заморочился с компаратором

arhiv6 ответил TOG тема в Схемотехника

Подобный вопрос на форуме уже обсуждался ТУТ. -

csv - это простая таблица в текстовом формате. Если размер файла небольшой, то можно LibreOffice Calc или Exel. Если файл большой, то gnuplot или математический пакет какой-нибудь. Пока писал ответ, уже всё то же самое ответили...

-

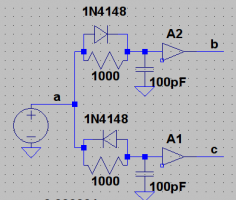

Управление ключом на MOSFET'ax

arhiv6 ответил TOG тема в Схемотехника

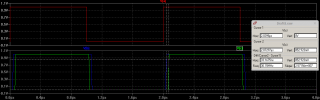

TOG, а где у вас на схеме драйвера? Пологий фронт и должен получиться, а задержка появится сама - драйвер срабатывает по определённому напряжению, затянули фронт-он сработает немного позже. У вас, как я понял, сейчас есть рабочая схема (первый пост), в которой для управления требуется 2 сигнала с разницей 10нс, а вы хотите, чтобы она управлялась одним сигналом? тогда не меняйте её, только перед драйверами поставьте RD цепочки вот так: здесь С - входная емкость драйвера (посмотрите в даташите, +можно добавить внешнюю емкость). A1,A2-ваши драйвера. Увеличивая R или С - увеличим задержку. Вот что получилось: a-сигнал на входе. b,c-на выходах драйверов. В данном случае задержка 33нс. -

Управление ключом на MOSFET'ax

arhiv6 ответил TOG тема в Схемотехника

Не смотрите на МАХ4420, это первая попавшаяся картинка. На ней я показал, ка включать RD цепочки. -

Управление ключом на MOSFET'ax

arhiv6 ответил TOG тема в Схемотехника

Если сильно не менять вашу схему, то можно подавать на драйвера один сигнал, но перед драйверами поставить RD цепи, как на рисунке. Они обеспечивают небольшую задержку на включение транзистора, почти не влияя на скорость выключения, тем самым и обеспечивая мёртвое время (ваши 10нс).