vik0

-

Постов

381 -

Зарегистрирован

Сообщения, опубликованные vik0

-

-

Амплитуда строба 5 В

Вы только по-аккуратнее там - у фина входы НЕ толерантны в 5В.

-

Во время ACK сенсор прижимает линию SDATA к земле, и уровень на линии упадет до нулевого вне зависимости - вход ли SDATA или выход. Или я неправ?

Может прижмет. А может и нет. Смотря у кого выходной драйвер сильнее. В любом случае так лучше не делать. Нехорошо (мягко говоря) когда линией пытаются управлять два устройста.

-

...выставляю на линии SDATA высокий уровень...

А вы SDATA переводите в режим входа?

Это фраза из официальной документации по сенсору mt9v022. Насколько я понимаю, для обработки поступающей информации сенсору необходимо некоторое время, которое выражается в количестве тактов. Но почему "master clock cycles", если речь идет о подчиненном устройстве? Ведь мастер - это процессор?Под фразой "master clock" имеется ввиду тактовый генератор для сенсора работающий на nn МГц. Там речь идет о десяках нс.

-

А может лучше просто использовать кварцевый генератор и не мучаться?

-

Пользуюсь оперой (конкретно 9.51). Когда первый раз читал Ваше сообщение, то не понял о чем Вы. Заходил в ПОИСК правым кликом мыши, открывая на другой вкладке и всё было нормально, но сейчас напрямую кликнул ссылку ПОИСК и просто всплыла простейшая форм

Opera 9.52. В простейшей форме можно выбрать "More search options" и попасть в "классическое" окно поиска.

Не правда, прикрепляются.Угу.. Только при попытке просмотреть ваши файлы, я получаю сообщение "Sorry, but you do not have permission to use this feature. If you are not logged in, you may do so using the form below if available." :unsure:

-

ARM чип с FPU, кроме IXP425 (см выше).

-

...По совету коллег из Германии удалили из шин адреса и данных резисторы...

Убивать за такие советы надо :(

Память рассчитана на 133 МГц. M12L64322AВам принципиально использование конкретной этой памяти? Если нет, то попробуйте промоделировать с памятью другого производителя (Samsung, Micron).

При разводке печатной платы укажите трассировщику выравнивать длины дорожек адреса, данных и сопровождающих сигналов.:cranky: Эээ.. А какое это имеет отношение к обсуждаемой здесь проблеме under/overshoot???

-

С CCS не работал, но..

Попробуйте собрать проект из директории в пути к которой нет пробелов и русских символов.

-

На вход 5V с USB через диод Шоттки типа 5817/5819

от него же будет запитана SDRAM и мелочи типа eeprom, кодека

А вы уверены что 500мА @ 5В вам на все хватит?

P.S. сколько тока жрет фин 532й на VddInt при частоте 400 мГц? я посмотрел в EE229v04.pdf - чуть более 500 мА - это правда или не то смотрел?См http://www.analog.com/static/imported-file...BF532_BF533.pdf

Табл. 15 и 17 на стр. 24 и 25.

У http://www.enpirion.com/ есть интегрированные преобразователи со встроенными катушками.А вы их использовали? Как впечатления?

-

1. Выбросить всю эту "инициализацию" и конфигурировать только те регистры, которые нужны вам (для начала вообще можно ничего не настраивать - сенсор со значениями по умолчанию прекрасно работает с фином).

2.1. Проверить адрес сенсора на I2C шине - у микроновских сенсоров есть ножки, позволяющие задавать им разные адреса.

2.2. Сигнал reset сенсора случайно не установлен?

2.3. Смотреть осциллографом что именно происходит на шине.

-

1) Насколько я понимаю керамика на 1-10 мкФ намного эффективнее в цепях развязки, чем танталы?

2) Нужно ли ёмкости этих (в. 1) больших блокировочных конденсаторов увеличить(уменьшить) ?

3) В схемах отладочных плат применяют память с параметром -75, что соответствует CLK<=100 МГц при CAS Latency=2 или CLK<=133 МГц при CL=3

Можно ли взять память с параметром -7E и запустить её на 167 МГц (CL=3) или 133 МГц (CL=2) ? Кто нибудь ставил такую?

Просто хочется иметь быстрый обмен (понимаю, есть кеши, но быстрый обмен на шине не помешает)...

1) AFAIK, да.

2) В принципе - все равно. Я у себя ставлю 10мкФ.

3) 167/CL3 - точно нет, так как system clock у фина - 133 максимум. 133/CL2 - не ставил, но никаких проблем не вижу (главное не забыть подправить инициализацию).

-

...6:1- что это значит?

Максимальное отношение толщины платы к диаметру переходного отверстия. Т.е. при отверстии 0.25, ваша плата должна быть не толще 1.5 мм.

Как остальные сигналы поведете, через разрез?Не смертельно. Фин на верхнем слое, питание - на третьем. Между ними нерезаная земля.

И на мой взгляд блокировочные конденсаторы надо было сразу поставить.Т.к. их рекомендуется размещать как можно ближе к выводам питания чипа,

начнете устанавливать, придется все остальное двигать.

А тут действительно, скорее всего возникнут проблемы :(

PS. evg123 вам очень хорошую книгу посоветовал. Из категории "must read".

-

развёл вручную за пол-дня SDRAM+BF.

Вот видите. А то сразу "нереально" :)

1) Корректно ли такое соединение...Абсолютно.

...про конденсаторы развязки......вам уже ответил _pv. От себя добавлю что чем меньше физические размеры конденсаторов - тем лучше.

...запаздыванием сигналов на 133МГц мы можем пренебречь?. Будет работать???Да и да.

- русский даташит с SDRAM- ссылку на хвалёный здесь автороутер PADS (который лучше спекктры)

- "И - боже вас сохрани - не читайте до обеда

советских газетпереведённых даташитов." (с)- PADS. Правда это не столько автороутер, а законченная система проектирования ПП.

-

Значит так. По порядку :)

1. можно поменять местами BA0, BA1 ?2. Можно поменять местами байты данных(биты каждого байта в пределах байта!) при этом поменять DQML, DQMH ?

Можно и можно.

3. Как допустимо мешать адреса?Лучше всего - никак.

RC-звенья? если да, то какая топология(вблизи чего, что и как) ?Если трассы длинные (> 5 см). Не RC, а просто последовательный резистор. Возле источника сигнала.

5. из внутренней плоскости питания вырезать площадку под фином на vddint(1,2v)?Остальное вокруг на vddext(3,3v)?

Да

Вторую плоскость земли(gnd) надо также резать или оставить сплошной?Оставить сплошной.

полагаю что при этом нужно:DQML (SDRAM) на ABE1 (BF) и

DQMH (SDRAM) на ABE0 (BF)

Правильно.

что скажете об использовании кондёров X5R:0805 10uF, 22uF, 4.7uF в качестве блокировочных?

а также 0402 X5R на 0.1uF ?

Лучше смесь из 0402 на 100 и 10 нФ.

пятый слой(vddint) так и напрашивается:)Расточительство :)

Если получится (ничего не обещаю!), попробую к вечеру прикинуть вам пример разводки.

-

1. Питание vddint подаётся справа внизу от источника 1.2в на прямоугольную площадку под фином. От площадки разносится питание по ногам(+кондёр на каждую ногу)

2. внутрение слои заняты vddext, gnd.

На слое с vddext можно легко выделить участок для vddint

3. у меня clock в десять раз короче остальных.4. память от фина на растоянии около 1см.

5. буфер на данных после сдрам(тоесть к фину на ноги данных сдрам и буфер)

Давайте внесем немного ясности - что такое u1, u2 и u3?

6. в ручную развести всё НЕРЕАЛЬНО! Использую specctra15.АБСОЛЮТНО реально. В крайнем случае, не поленитесь написать толковые правила для specctr-ы.

7. не рискнул поменять биты:д0..д7

д8..д15

в отладочных платах почему-то так не сделано.

В отладочных платах слоев побольше :)

а вдруг возникнут проблемы с командами инициализации сдрам?Внимательное чтение datasheet на память открывает простой факт - линии данных не используются для задания команд.

убедительная просьба- объясните,как в моём случае расположить память к фину(впритык)Выложите файл трассировки - по картинкам среднего качества достаточно трудно что-либо советовать..

-

Расположил SDRAM к BlackFin'у так, чтобы дорожка CLKOUT была наикратчайшей (для остальных трасс такое расположение очень невыгодно - очевидно)

Вы крайне неудачно расположили компоненты. Короткий CLKOUT - это конечно хорошо, но только не тогда, когда он в десятки(!) раз короче остальных сигналов.

Планируется ещё один банк асинхронной памяти (для LCD - заложил буфер 74LCX16245)Буфер лучше поставить после SDRAM.

Конденсаторы блокировочные (к каждому пину 0.1мкф(керамика) и на чип 10 мкф(тантал))На всякий случай - вы не забыли конденсаторы на VddInt?

О! Кстати, если я правильно понял - полигон под фином это - VddInt? И он подается только через тонкий "огрызок" к 25-й ноге?

Значительно лучше выделить под VddInt островок на слое питания.

P.S. с наступившим 2009 :santa2:И вас с тем же :)

-

Или может кто нить объяснит как делаются ассемблерные вставки, ассемблерные процедуры (описание входов/выходов), я по этой теме не нашел ни одного путного документа (конкретно для TS-x01).

Все прекрасно расписано тут.

Стр. 1-102: Inline Assembly Language Support Keyword (asm)

Стр. 1-261: C/C++ Run-Time Model and Environment

Стр. 1-289: Register Classification

Стр. 1-298: Calling Assembly Subroutines From C/C++ Programs

-

2) может ли проц сначала быть загруженным в режиме раб (с ПЛИС), а потом выступать мастером по отношению ко флеш-памяти?

А почему бы и нет? Естественно ПЛИС должна об этом знать и не пытаться управлять линиями SPI :)

Так и не понял причем тут PCI. С двумя приведенными вариантами тоже как-то туманно. Не могли бы как-то по-другому задать вопрос и расписсать структура планируемого изделия, возможно даже алгоритм загрузки в каком случае с памяти в каком с ПЛИС.+1

3. В ЕЕ240 рекомендовано ставить подтяжку на MISO и CS.На MISO подтяжка требуется

-

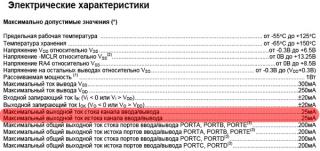

Обратите еще внимание на то, что это - максимально допустимые значения и длительная работа МК при таких значениях не гарантируется..

-

И ещо, почему не рекомендуется из сдрам выполнять программы? как же тогда линукс эксплуатируют?

Выполнять можно. Только это будет весьма меделенно. А ядро RTOS должно выполнятся с максимальной производительностью. Иначе это будет недо-

RTOS.. -

Что-то мне припоминается что в VDSP со второго или третьего апдейта можно не использовать эти макросы, компилятор сам подсовывает то что надо. По крайне мере щас с пятым апдейтом не использую эти макросы, проблем не наблюдаю.

Э.. А откуда информация? В последней anomaly list все еще отправляют к макросам.. (да, и со второго апдейта этого точно не могло быть - там только появились макросы :))

...Проблемы есть...Извините за глупый вопрос. Вы случайно не работаете с флагами из одного регистра двумя ядрами одновременно? Если да, то не забыли про ssync?

-

...с PADS2005 возился...

Ну вообще последняя версия - 2007. И скоро выйдет 2009 :)

не очень удобно, особенно в logic.В полной версии PADS присутствует DxDesigner - намного более функциональный/комфортный схемный редактор (и не только).

PS. А еще в PADS входит HyperLynx - [почти] незаменимая вещь для SI на высоких частотах.

-

А кто знает где в Киеве прикупить себе TFT для забав с графикой в uLinux недорого? Как вариант у меня есть из єдектронной фоторамки, но под него нет доки...

:bb-offtopic:

Ну про недорого не скажу... Но EZKIT-BF548 - обалденная вещь. И TFT (с touchscreen) и клавиатурка и HDD на 40 Гб... Правда цена кусючая.. :05:

PS. Порадовало видео в котором под uсLinux на данном EZKIT-те гоняли Doom :)

-

4) не перемешивать между собой адресные(A0..A?), данные(DQ0..15) и управляющие(CS,WE,OE,CAS,RAS,DQML,DQMH,CLK,CKE,...)

Данные в пределах одного байта (т.е. DQ0-7 и DQ8-15) свободно можно менять между собой. Управление - однозначно не трогать. Адрес - можно, но очень осторожно (при изменении не выходить за пределы адресов строки/страницы) и с привязкой к конкретной микросхеме SDRAM.

5) блокирующие конденсаторы крепить ПОД микросхемой сдрам, соединения не к пинам, а сразу в плоскости питания, земли.Не обязательно под. Главное максимально близко к пинам.

7) конденсаторы 0.1 мкф керамика на все блокировочные пины, и один танталовый 10мкф на какой -нибудь один блокировочный пин.Тантал просто на плате в районе мс памяти и фина, без привязки к конкретной ноге.

Скажите, при вышесказанных правилах каковы шансы запустить верно SDRAM на 133 Мгц? в сдрам нужно выполнять программы (типа RTOS).Не плохие шансы. Зависит от качества трассировки (только выполнять из SDRAM код RTOS - отнюдь не самая удачная идея..)

Что можно к правилам добавить или убрать или исправить?Вот тут почитайте, поучительно. И еще - не игнорируйте моделирование SI.

UART передача по DMA

в Сигнальные процессоры и их программирование - DSP

Опубликовано · Пожаловаться

А ничего что ff - некорректное значение для iar? Зачем вам вообще эти строки? uart ведь и так на 10-м ivg.

И где инициализация DMA_START_ADDR?

Да нет, вам память изменяет :laughing: Он как раз UART TX.