vik0

Свой-

Постов

381 -

Зарегистрирован

Весь контент vik0

-

Нет, не нужно. PS. В DDR3 тоже не нужно, если нормальный контроллер (не i.Mx)

-

И опять DDR3. В паре со странным SoC. Прошу критику.

vik0 опубликовал тема в Примеры плат

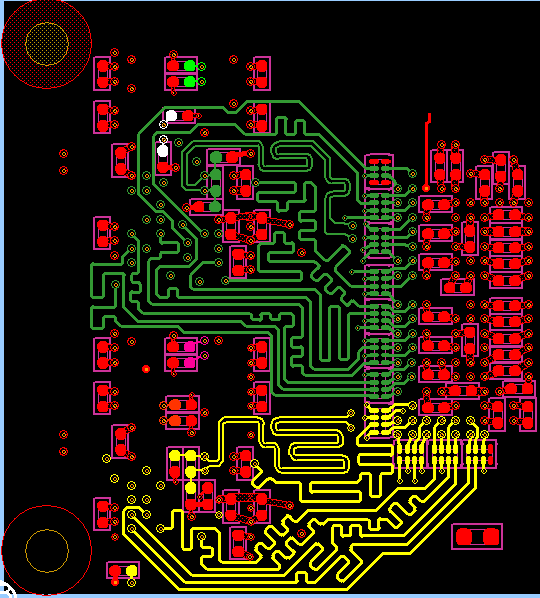

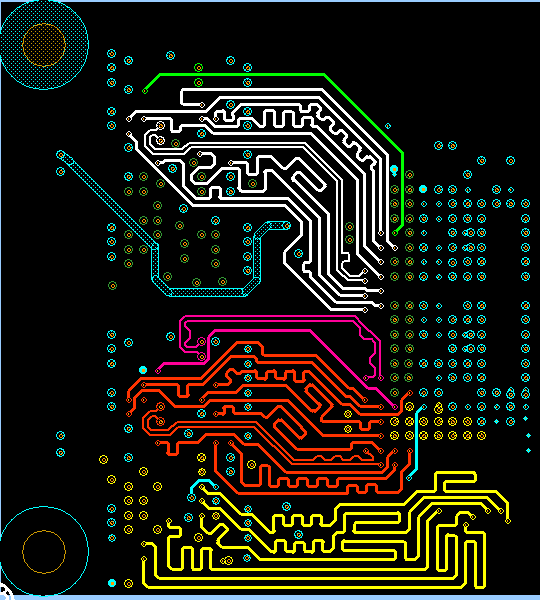

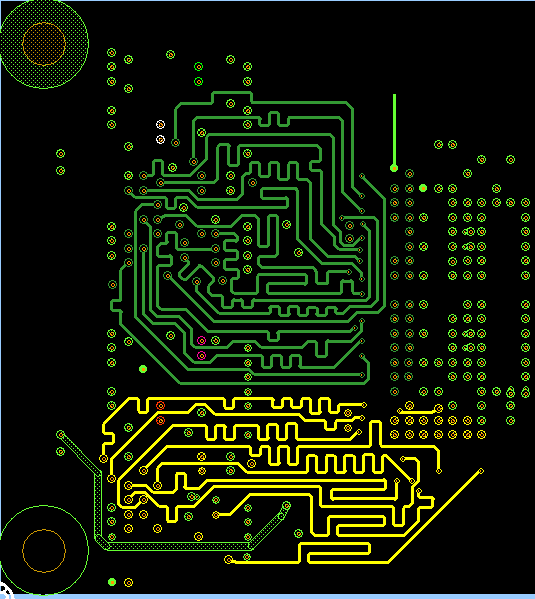

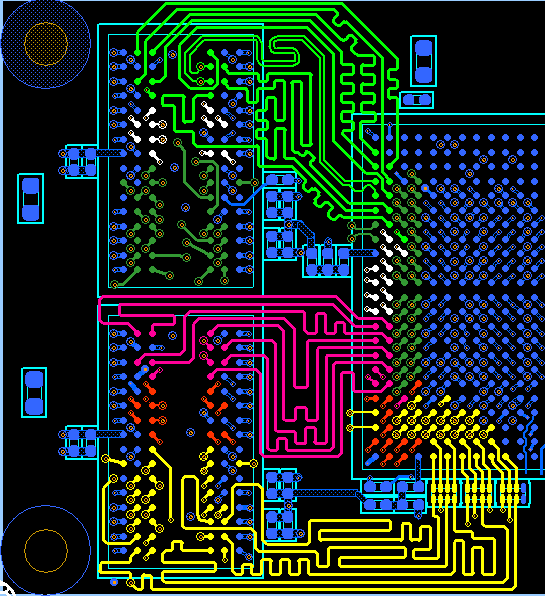

Форумчане привет, Прошу покритиковать трассировку DDR3. Вводная информация: SoC - ADSP-SC587 (Analog Devices) 2 независимых контроллера памяти, каждый поддерживает 16-bit single memory IC У производителя несколько необычные рекомендации по терминированию: десятки Ом последовательно для control and address сотни Ом на землю/питание для pull-up/down для индивидуальных сигналов дифф пар подробнее тут - https://www.analog.com/media/en/technical-documentation/application-notes/ee387.pdf Во вложение скриншоты по слоям Трассы выделены цветами: Memory controller 0: Control/address/clock - желтый Lower byte lane - сиреневый (pink) Upper byte lane - красный Memory controller 1: Control/address/clock - темно-зеленый Lower byte lane - белый Upper byte lane - светло зеленый Стек: везде импеданс 50 Ом, по рекомендации производителя 2-й слой: сплошная земля 5-й слой: +1.5В. Минимальное расстояние от трасс до края полигона - 1.5мм Буду рад любой критике, спасибо. -

Vitesse? Там и документация доступна. И покупка - на digikey-е хоть поштучно бери. (речь, естественно, про однопортовые) Сами использовали в паре проектов VSC8211 - все хорошо, проблем не было.

-

Буквально на днях было: http://electronix.ru/forum/index.php?showt...t&p=1002770 Может и не актуально для ТС (т.к. не все контроллеры поддерживают данную feature), но решил добавить для полноты картины.

-

EE-240 Только мне кажется, что вы и uriy говорите о разных вещах. Если я правильно понял вам необходимо дизассемблирование/декомпилирование, а uriy говорил о модификации загрузочного файла. Поправьте, если я не прав. ps. Не знаю какое у вас семейство, но, ЕМНИП, у 54x (и скорее всего у 50x, 51x и 52x) семейства немного изменился формат ldr. Описание изменений - в hardware reference manual

-

Извините, но это полнейший бред. Используйте atof (или sscanf) и не заморачивайтесь

-

ARM9+матрица Аptina MT9P031

vik0 ответил Игорь Кищак тема в ARM

То, что матрица ничего не знает о том, что ей надо по своему входу ОЕ игнорировать обмен по i2c. Еще раз уточню, что под фразой ТС "выбор самой матрицы делать через порт OE" я подразумеваю что он собирается использовать ОЕ вход матрицы чтобы отключать реакцию матрицы на обмен по i2c. Если я не прав, пусть ТС меня поправит. -

ARM9+матрица Аptina MT9P031

vik0 ответил Игорь Кищак тема в ARM

OE - это output enable матрицы? Если да, то не получится, т.к. он применим только шине данных, но не к i2c. Да. А у MT9P031 они одинаковые и без возможности изменения. -

Расширение оперативной памяти

vik0 ответил Александр77 тема в Схемотехника

Правильно подключать к 548 блекфину DDR память -

:bb-offtopic: Улыбнуло :) А ничего что родоначальником i2c является NXP (в те времена еще Philips)? И именно их реализация является стандартом де-факто :laughing:

-

disel Спасибо! GetSmart http://depositfiles.com/files/9rqiy28hb

-

Схема UCF файл User guide Документация Reference designs

-

Полный UCF файл

-

Где-то так: .... I0=0; R0=[P0++]; LSETUP (lp_begin, lp_end) LC0=P5; lp_begin: (R7,R6) = byteunpack r1:0; // r7.h=Y2; r7.l=cr1; r6.h=Y1; r6.l=cb1 R5 = pack (R7.h, R6.h) || W[I2++]=R7.L; [P1++]=R5; lp_end: MNOP || W[I3++]=R6.L || R0=[P0++]; .... За правильность не ручаюсь - проверить нет возможности. PS. Еще можно попробовать с помощью DMA...

-

А вам нужно именно внутри одного проекта? Так, afaik, нельзя. А скопировать проект со схемой и разводкой можно через "Job management wizard".

-

PCI-Express 8 lanes

vik0 ответил dysan тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

А вы возьмите какой-либо reference design и измерьте... Вот, например. Проверено, данная плата прекрасно входит в 1-х слот и работает :) -

микросхема SDRAM

vik0 ответил Bakradze тема в Цифровые схемы, высокоскоростные ЦС

54х серия позволяет -

А посмотреть в product selection guide религия не позволяет?

-

Windows 7

vik0 ответил Hellper тема в Операционные системы

Да, тоже. Другое дело, что в AMD64 их в два раза больше (16). -

Режим 0 - это выполнение из флэш, без загрузки. Вам нужен режим 1.

-

Которые компенсируются большой тактовой частотой. http://www.freertos.org/ IMHO, VDK - кака. Помимо вышеназванной freertos, советую посмотреть на ucOS/II и scmRTOS.

-

Есть ли такое ОЗУ

vik0 ответил IXFN50N80Q2 тема в Микросхемы

Есть. Двухпортовое ОЗУ называется. Например: http://www.cypress.com/?id=82 http://www.idt.com/?catID=58642&loc=col1 Только стоят они весьма серьезно. -

Выше под "memory space" подразумевается банк асинхронной памяти.

-

FSM и лог состояний

vik0 ответил Kuzmi4 тема в Работаем с ПЛИС, области применения, выбор

ЭтоСтильПаскаль вотЭтоКэмел а_это_с_подчеркиваниями -

И это понятно. Но речь шла не про "C vs ASM" в общем случае, а про "C optimizer vs ASM". И от AD: http://www.analog.com/static/imported-file...160113EE149.pdf http://www.analog.com/static/imported-file..._transcript.pdf http://www.analog.com/static/imported-file...kfin_slides.pdf