-

Постов

3 012 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент GenaSPB

-

Срок поставки 7 месяцев

-

Ясность появилась. Сохранение/восстановление перделал как надо (32 без двух целочисленных регистров и 32 double). сохранение/восстановление mstatus, mpc, mcause вокруг вызова обработчика (под запрещенным через mstatus.MIE запросами). void VMEI_Handler(void) { const uint_fast16_t int_id = PLIC->PLIC_MCLAIM_REG; PRINTF("VMEI_Handler enter: int_id=%u\n", int_id); if (int_id != 0) { //const uint32_t prio = PLIC->PLIC_MTH_REG; #if WITHNESTEDINTERRUPTS const uint_fast8_t priority = PLIC->PLIC_MTH_REG; /* текущий уровень приоритета */ PLIC->PLIC_MTH_REG = PLIC->PLIC_PRIO_REGn [int_id]; /* обрабатываемый уровень приоритета */ const uint_xlen_t mepc = csr_read_mepc(); const uint_xlen_t mcause = csr_read_mcause(); const uint_xlen_t mstatus = csr_read_set_bits_mstatus(MSTATUS_MIE_BIT_MASK); /* раразршение прерываний */ ASSERT((mstatus & MSTATUS_MIE_BIT_MASK) == 0); /* прерывания были запрещены при входе в обработчик */ #endif /* WITHNESTEDINTERRUPTS */ __FPU_Enable(); ASSERT(int_id < MAX_IRQ_n); (plic_vectors [int_id])(); #if WITHNESTEDINTERRUPTS csr_write_mstatus(mstatus); csr_write_mcause(mcause); csr_write_mepc(mepc); PLIC->PLIC_MTH_REG = priority; /* восстанавливаем обрабатываемый уровень приоритета */ #endif /* WITHNESTEDINTERRUPTS */ //PLIC->PLIC_MTH_REG = prio; PRINTF("VMEI_Handler exit: int_id=%u\n", int_id); PLIC->PLIC_MCLAIM_REG = int_id; /* EOI */ } } Я правильно понял, что сперва в архитектуре источники запосов проходят через регистр mie - а затем фильтруется mstatus.MIE ? ... осталось разобравтьс с PLIC - выдает прерывания того же приоритета до EOI обрабатываемого. Ожиждаемое поведление - прерывается только более высоким приоритетом

-

Так я все gp и плавучку сохраняю . В Isa не понял откуда адрес берет.

-

Но хоть lr или еще что-то должно... mret ведь предполагает что-то для возврата... зы: rv64 должен сохранять 8 байт ргистры. Вот мой стартап файл: Так и в Cortex-A это ручками делается... Смысл диктуется имеющимся многоплатформенным проектом. Короче вопрос уточняю - что использует mret кроме сосотояния флага? На Corex-A содержимое стекового фрейма обработчика переносится в общий стек

-

Пытаюсь сделать вложенные прерывания = но нигде не могу найти инфу, что же в стеке сохраняется из стсотояния процессора. Судя по отладке, 64 быайта сохранены... RV64.

-

У вас есть код фильтрации из примера cmsis. Построить массив параметров функциями что я прислал или любым генератором. И всё.

-

Это расчеты для симметричных FIR (с нечетным количеством отводов) - формирует половинку от массива. Для увеличения крутизны скатов еще "оконную" функцию к массиву применяют.

-

CMSIS-DSP\Examples\ARM\arm_fir_example не?

-

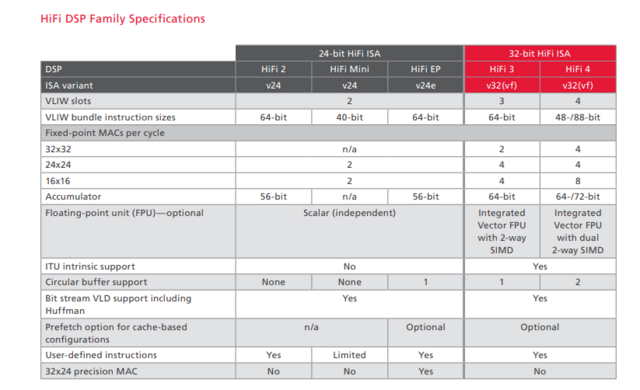

Mimxrt685-EVK Cadence Xtensa HiFi4 DSP опыт работы

GenaSPB ответил LexaryStyle тема в NXP

Cadence Xtensa HiFi4 DSP Так же и в составе Allwinner T113-S3 есть. Где-то должен существовать компилятор С для этого процессора от Cadence - XCC https://docs.zephyrproject.org/3.2.0/develop/toolchains/cadence_xcc.html Есть документ по архитектуре HiFi 3- hifi_3_dsp.pdf -

Грамотный выбор видео процессора/контроллера

GenaSPB ответил AntonGaribov тема в ARM

На гитхабе можете полный cmsis header скачать с тем что описано в доке и что удалось расковырять. Тут Бранч develop -

Грамотный выбор видео процессора/контроллера

GenaSPB ответил AntonGaribov тема в ARM

Колега поднял CAN на Allwinner-t113-s3 Не забыть в CCU тактирование включить и reset отпустить... -

Коллега специально не хочет оптимизацию включать... -O1 у него предел.

-

и unbuffered это разные свойства логики

-

Специфическое это gic, mmu, axi в ccu.. кеш. T113s3 это два ядра а не одно, тут чего уж сравнивать... в dsp приложениях у меня существенно.

-

Творческий интерес. Ну очень много шума про risc-v вокруг, а тут подвернулось устройство, которое можно запустить не изучая периферию а сосредоточившись чисто на новой архитектуре... на ядре. Периферия этого процессора совпадает с t113s3 той же фирмы. Кроме специфического для ARM. И запущена Cmsis dsp библиотека. Этакий угон совершил. Но там качественно написано, всё просто комплиоируется. Тестировал на проекте sdr. Те же openvg картинки гонял - как проверка устойчивости работы под нагрузкой для fpu.

-

Ну и как впечатления относительно кортекса? Подитожу. Производительность на одинаковых мегагерцах сопоставима с кортексами А.

-

Разобрался с сильно мешавшей ошибкой в чужом коде управления кеш-памятью с использованием ассемблерных вставок. Начиная с того что работало только на минимальном уроне оптимизации (-Og), так у оригинала была еще ошибка в коде операции dcache.cpa Вот так выглядит работающее: Танцы вокруг работы со специфическими для ядра С906 командами, которых не знает riscv gcc/as

-

Hex Contact Bounce Eliminator MC14490 MC14490.pdf

-

вложенные прерывания - архитектура

GenaSPB ответил addi II тема в В помощь начинающему

Контроллеры прерываний в современной технике обычно поддерживают вложенность, на некоторых архитектурах требуются программные извращения (Cortex-A) для поддержки вложенности. -

вложенные прерывания - архитектура

GenaSPB ответил addi II тема в В помощь начинающему

Cortex-A (GIC), Cortex-M (NVIC), RISC-V (PLIC) - все три проверено - поддерживают -

Подразобрался с загрузчиком с SPI NOR FLASH. Научил свою утилиту формировать команду перехода на начало образа в кодах risc-v. Выяснилось, что адрес загрузки всегда 0x20000 вне зависимости от того значения, что в заголовке написано. Используемый мною код инициализации DDR(2) не очень работает на этом процессоре. А вариант прямого использования образа что грузит утилита xfel не получается простыми способами - скомпилировано под стартовый адрес 0x20000 https://raw.githubusercontent.com/ua1arn/hftrx/develop/tools/egontool/egontool.c

-

ноль в этом регистре вроде про это

-

В этом режиме не требуется

-

Есть режим трансляции один-в-один - его используете? // 3.1.6 Virtualization Management Field in mstatus Register // Table 3.3: Encoding of virtualization management field VM[4:0]