-

Постов

502 -

Зарегистрирован

-

Посещение

Весь контент Losik

-

если не секрет в какой области проекты?

-

если менедмент умеет налаживать удаленную работу(скажем как в айти), то да можно всех на договора посадить и пусть работают удаленно. как минимум выбор сотрудников будет шире и можно поиграться с фондом ЗП, релокация отдельная боль. многие боятся удаленки, но в европе/сша это норм, не очень много но есть, главное будет грамотно распределять и контролировать рабочие процессы. из самого затратного это покупка софта и фонд ЗП. на софте можно экономить, есть варианты свести все в ноль, если найти кад инженера или сотрудника с богатым опытом. зп это 200-300т.р. в месяц на сотрудника, может больше так как это разовый контракт, в разделе работа есть вакансии от kraftway с зп от 250т.р.

-

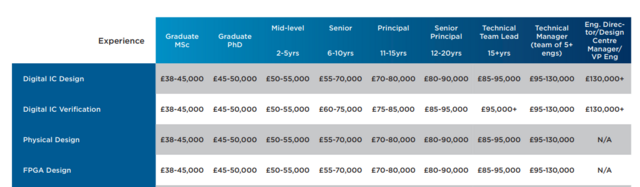

На интузиазме можете и за 0рублей сделать) по опыту, физ лицо не поднимит разработку, тестирование, софт, изготовление и менеджмент, ооооочень мало людей которые могут в полный маршрут и финально все равно понадобится юр лицо для общения с фабом. да и зачем кому-то с опытом в это влазить, им и так хорошо платят. пример ЗП в UK, вам нужен хотя-бы сеньер чтобы он что-то самостоятельно делал. Возможно несколько разработчиков такого уровня, так как область знания обширная даже чисто цифрового дизайна. но собрать свою команду будет конечно дешевле, чем заказать разработку у соответствующих компаний, там будут коммерческие аппетиты ничем не ограниченые.

-

In the context of a system with two Phase Locked Loops (PLLs), coherence refers to the ability of the two PLLs to maintain a consistent phase relationship with their respective input signals, while also being synchronized with each other. This synchronization ensures that the phase difference between the output signals of the two PLLs remains constant or predictable over time, leading to a stable and controlled system behavior. The coherence between two PLLs can be quantified by measuring the phase difference between their output signals and monitoring its variation over time. A highly coherent system will exhibit a stable phase difference, whereas a low coherence system will have a varying or unpredictable phase difference.

-

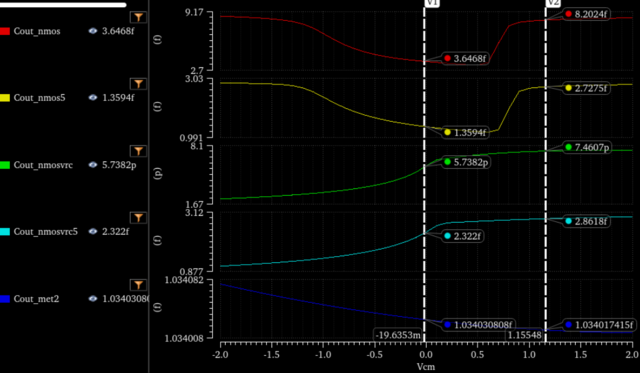

пример расчёта емкостей pn перехода и ёмкости оксида для cmos технологии (finfet не проверял). Соответственно можете прикинуть размер транзисторной емкости или её значение, зная размер. Есть еще варакторы, их емкость более линейна но удельное значение не сильно выше будет. Еще есть метальные емкости(MIM-MOM), их параметры зависит от технологии. Если нужна большая емкость набирают стеком, снизу mos устройство, сверху MIM/MOM. нужно понимать для каких применений емкость, не все подойдут для rf, а для LDO будет норм пойти любая. mos емкость нелинйная. вот пример набор емкостей доступных в одной из технологии и их параметры, на графиках емкость на квадрат(1umx1um), для low voltage nmos, high voltage nmos, varactors low/high voltages and met cap: соответсвтенно емкость 100pF для low voltage 165umx165um если поверх положить метал емкость в стек то получим +27pF 127pF уже норм ескость для LDO на чипе, с ядром ~65umx65um до 250pF ёмкости считаются норм для стандартных технологий. можно и десяток нан получить, заполняя дырки емкостными структурами. если есть цифра то там в спец ячейках для заполения(филлеры) емоксть стоит. суммарная емкость может быть очень большой, зависит от цифры. чем ниже нод тем емкость больше. + емкость может быть ограничена величиной утечки, проблема для mos емкостей например ток утечки на выходе CP в PLL попортит жизнь.

-

Устойчивость ФАПЧ с активным фильтром

Losik ответил Waso тема в RF & Microwave Design

ядро у ИОН быстрое, микросекунды на включение, если специально не замедляют схему включения для исключения появления всплесков на выходе при включении. подстройка идет через ток или резисторы, процесс быстрый. но обычно на выходе ИОН стоит фильтр, соответственно его полоса и задает скорость перестройки ИОН. Если ИОН внутри PLL с подстройкой, то он используется для формирования опорных токов на внешнем резисторе, в путях формирования токов стоят свои фильтры, там да мс легко набегают. Вариант через внешний резистор, формирующий опорные токи, должен быть приблизительно такой же по скорости как с ИОН. Не совсем понятно как вы хотели модулировать частоту выходного сигнала таким способом, изменение ИОН и R приведет к изменение тока и полосы у PLL. я бы ожидал влияние но минимальное, основная обратная связь должна душить модуляцию, или там тоже сигнал модулировался в фазе? пропустил что вне основной полосы меняли, тогда понятно. но не понятно как изменние опорного тока в плл приведет к модуляции в ВСО, если он конечно не в режиме ограничения тока. -

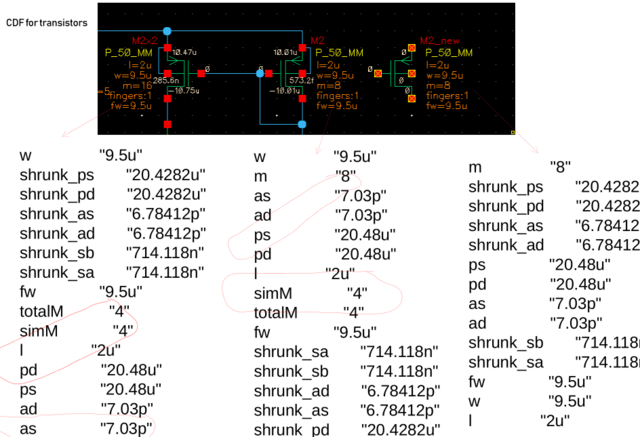

возможны ошибки в CDF параметрах транзисторов, схематики которых вы будете моделировать. пример, старые схемы содержали simM=4 а m=1 после миграции, LVS/DRC проходили а в моделировании каша. если вставлять новый девайс то все ок, исправлялось посредством скрипта. еще в топологиях слои могут поменяться) и давать чистый DRC/LVS

-

1. пользуюсь, например для парсинга экстрактов и построение карты паразитов, проверки падения напряжения на разводке без доп тулов(экономия на лицензиях), генераторы топологий, проверка сквозных имен и нагрузки на выходы ячеек; 2. пользуюсь для автоматизации тестов, использую ocean+spectremdl or python; в спектре или виртуозо (каких-то версиях) были туториалы по AMS, на офф сайте есть примеры подробные; 3. Baker, R: Cmos: Circuit Design, Layout, and Simulation.

- 3 ответа

-

- virtuoso

- layout suite

- (и ещё 5 )

-

если у вас есть купленный софт то вы регестрируете на сайте пользователя и он получает доступ к внутренним обучающим ресурсам. просто что-то выкладывать запрещают, например у меня во многих документах идут персоональные watermarks.

-

Вопросы по Cadence Virtuoso

Losik ответил APEHDATOP тема в RF & Microwave Design

когда в calculator выбираете функцию, внизу справа будет кнопочка help с примерами использования функции. поповоду спектральной оценки почитайте APPENDIX A SPECTRAL ESTIMATION в книге Understanding Delta-Sigma Data Converters Shanthi Pavan и у него же была лекция на ISSCC Simulation Techniques for Data Converter Design Instructor: Shanthi Pavan -

Вопросы по Cadence Virtuoso

Losik ответил APEHDATOP тема в RF & Microwave Design

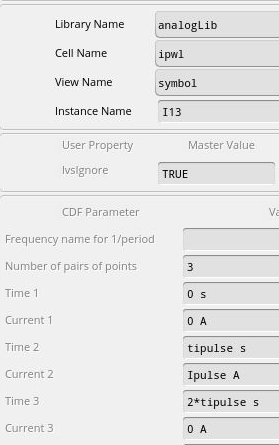

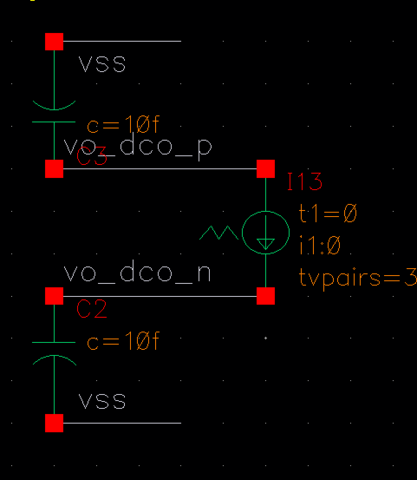

не помню такую ошибку в tran анализе, это не pss? с идеальной катушкой у вас только L, с реальной RLC схема и условия генерации могут не выполняться. VCO в tran анализе нужно иногда пнуть немного, чтобы он начал генерировать, например посредством пилообразного ipwl источника тока подключенного между дифф плечами(добавить смещение в плечах, см картинку), или ставить очень маленький шаг. или включать её из состояния которое приводит к началу генерации( например подавать питание от нуля нарастанием, добавить шум). у VCO кроме режима генерации могут быть и стабильные состояния. -

Вопросы по Cadence Virtuoso

Losik ответил APEHDATOP тема в RF & Microwave Design

шумы VCO нужно измерять с реальными источниками тока, без них у вас и будут +/- хорошие результаты. погуглите Design Challenges In Multi-GHz PLL Frequency Synthesizers Adrian Maxim там есть соображения по шумам для VCO. -

@Doka привет) я смотрел эти IP раньше, большой плюс ефаба что они дали свободный доступ к софту и китам разработчикам. но мне кажется они так и не не смогли привлечь хороших разработчиков и все аналоговые IP в лучшем случае студенческого уровня. но это хороший старт для них, на который можно опираться.

-

Добрый, не пользователь цифровых тулов, но насколько я знаю некоторые команды перестают поддерживать от версии к версии или меняется их формат. если есть ошибка в логе то нужно её исследовать, обычно там достаточно информации чтобы понять в чем причина. По поводу cds.lib вы можете в одном этом файле указать путь ко всем библиотекам которые вам нужны, даже если они из разных PDK. Будет проблема с просмотром топологий, если библиотеки имеют разные display.drf и будут проблемы с загрукой настроект для PDK .cdsinit. Все это можно решить при необходимости, но лучше никогда не смешивать разные библиотеки.

-

слишком мелко) они должны задавать тренды запросами и деньгами, а не заниматься дизайном. почему я считаю полезным иметь свое "референсные" проекты, это аккумулирует опыт который останется с вами и может быть использован в виде схем/идей/документации/подходов в других проектах или собеседованиях. условно вот такой блок я сделаю так-то, тесты такие-то, ожидаемые параметры такие-то, интерфейс такой-то, документация вот в таком виде. имея такой проект вы можете структурированно накапливать свою компетенцию и упрощать свою работу от проекта к проекту. конечно есть тонкие вопросы связанные с програмным обеспечением и правами на результаты работы. работодатель в 99% стремится забрать все результаты труда себе)) но можно обговаривать что ты можешь оставить себе, не нарушая договоров или делая эти референсы более абстрактными.

-

а у вас как дизайнеров чипов есть свои референсы? ну хоть в виде схемы и документации? почему спрашиваю, в интернете их не особо но есть, понятно что не все захотят выкладывать пример https://github.com/muhammadaldacher/Analog-Design-of-Asynchronous-SAR-ADC а вот среди знакомых таким никто не занимается. хотя мне кажется это очень полезно.

-

точно не помню но вроде в доках были картинки с новым интерфейсом

-

да, все верно, если через iScape устанавливаете то указываете первый диск, потом выбираете опции что установить, при установке он попросит путь к следующему диску если там нужная ему информация для установки. перед установкой нужно стандартным для кэденса образом указать путь к лицензионному серверу( файлу) где есть фича AMS_Methodology_Kit

-

насколько я помню AMSKIT идет обычным пакетом но при установке by iScape нужна лицензия для расшифрования, feature AMS_Methodology_Kit

-

не, у меня нету, с кэденса их давно уже нельзя скачать, прекратили поддержку. когда-то на eetop выкладывали но возможности скачать от туда у меня небыло, слишком большие но отдельные документы и сейчас доступны. Также у кэденса есть Verification KIT он поставлется с INCISIVE до 18 или 19 версии вроде.

-

Референсы есть. Из легко доступного кэденс раньше поставлял RFKIT/AMSKIT/LPKIT пакеты: RFKIT wifi приемопередатчик AMSKIT - FLASH ADC/Frac-N PLL LPKIR - ARM processor with misc IP Это скажем большие законченные учебные проекты выполненные в GPDK. Есть еще маленькие учебные проекты, условно как сделать CPU от верилога до GDS или ADC они идут в их обучалках. Средней доступности у фабов есть референсные проекты которыми иногда дают попользоваться (PLL/BGR/LDO) Так же были/есть обучающие центры в которых учат проектировать на реальных проектах.

-

Вопросы по Cadence Virtuoso

Losik ответил APEHDATOP тема в RF & Microwave Design

>>Ну и отвратительные фазовые шумы используйте резистор вместо токового зеркала от питания к катушкам, поможет снизить шум. с реальным источником опорного тока шум значительно увеличится. у вас полу идеальная схема, для RF используйте rf элементы из кита, там же есть и готовые индуктивности. >>Подскажите как организовать трансформатор (балун) из имеющегося набора индуктивностей, или это как-то по-другому делается? для проверки идей можно сделать модель из элементов библиотеки analogLib. для реальной схемы трансформаторы делаются вручную с характеризацией спец программами или с помощью генераторов трансформаторов/индукторов. у кэденса это EMX или сторонние программы типа Heilic, Sonnet. Они требуют наличие тех файлов в PDK с описанием электрических свойств слоев в процессе. -

Вопросы по Cadence Virtuoso

Losik ответил APEHDATOP тема в RF & Microwave Design

LC-VCO не переключается в большом диапазоне, скажем +/-1.5GHz макс с учетом того что вам еще нужен запас чтобы скомпенсировать уход по корнерам. но можно использвать несколько LC-VCO параллельно. и 20GB/s по отдной линии в 65nm я не видел, возможно и делают) пример как делают на ring https://biblio.ugent.be/publication/8550815/file/8551234.pdf В образовательных целях: https://people.engr.tamu.edu/spalermo/ecen720.html -

Вопросы по Cadence Virtuoso

Losik ответил APEHDATOP тема в RF & Microwave Design

должен заводиться и при 0fF нагрузке, 120f это слишком много для 10G) поменяйте max timestep, я писал про это. вам нужно не просто запустить генератор но и понять в каких условиях он не будет работать и почему. процесс не должен влиять, в целом отличие logical процесса от RF+logical в наличии дополнительных RF устройств, но в вашей схеме вы используете "logical" транзисторы. _rf элементы имеют фиксированную топологию и лучше измерены, более точные модели, но в моделировании схемы они будут давать результаты хуже чем версия с "logical" элементами. они заранее учитывают паразиты из фиксированной топологии. CDR бывают разные)) если они расчитаны на широкий диапазон частот то часто используют комбинацию Ring/LC-VCO. если на CDR на одну высокую частоту то лучше LC в одноканальном исполнении. если много каналов то смотрите цифровые CDR, там один PLL который формирует высокочастотный опорный сигнал для всех каналов CDR. -

Вопросы по Cadence Virtuoso

Losik ответил APEHDATOP тема в RF & Microwave Design

точно не помню какие задержки в 65nm, но 10GHz вроде можно на цепочке из 3 инверторов получить. если при увеличении W в ядре не увеличивается частота, добавьте больше тока( можно и просто на питание подключить ядро, будет работать в режиме ограничения напряжения а не ограничения тока, чатотой можео управлять меняя напряжение питания ядра) поменяйте регулярные транзисторы на транзисторы с уменьшеным порогом nch_lvt/nch_slvt/nch_elvt pch_lvt/pch_slvt/pch_elvt используйте структуру с ограничением амплитуды сигнала в ядре, диф усилители с резисторами в нагрузке вместо инверторов.