-

Постов

3 864 -

Зарегистрирован

Весь контент Maverick_

-

Реализация медианного фильтра

Maverick_ ответил BAMBINATOR тема в Алгоритмы ЦОС (DSP)

Могу поделиться примером для реализации для ПЛИС на VHDL Когда-то сам на основе предложенной реализации - реализовал фильтр 7х7 PS там описана реализация для окна 3х3 окна, но думаю преобразовать его в окно NxN не будет большой проблемой Еще можете посмотреть у Xilinx xapp 953 "Two-Dimensional Rank Order Filter"(доступен пример на VHDL языке) Mediane_filter.rar -

:a14: :a14: :a14:

-

Вы правы :) Именно ее я и имел ввиду Спасибо :) посмотрел и все таки, реализация не по предложенному мною алгоритму (описанный в pdf файле). PS это только мое мнение

-

Чтобы спора не было надо бы кому-то просто реализовать по данному алгоритму. Потом произвести сравнение результатов синтеза :) Можно ссылку на предложенную схему des333, которая реализована по данному алгоритму (я что-то ее не увидел, может плохо смотрел :().

-

В книге Shevkoplias "Microprocessornye Structury" (стр 479) предлагают такой алгоритм. Вырезка этого алгоритма во вложении Когда-то давно я реализовал на VHDL логический элемент, который считает число единиц во входных данных так (он реализован на сумматорах) Описание портов: data – N разрядный вход add – N разрядный выход library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Vcnt1s is Port ( data : in std_logic_vector(15 downto 0); add : out std_logic_vector(4 downto 0)); end Vcnt1s; architecture Behavioral of Vcnt1s is begin process (data) variable S : std_logic_vector(4 downto 0); begin S := "00000"; for i in 0 to 15 loop if data(i) = '1' then S := S + "00001"; end if; end loop; add <= S; end process; end Behavioral; Shevkoplias.MicroprocessornyeStructury.pdf

-

Понимаете, что в Verilog, что в VHDL имеется стандартные конструкции - описания различных цифровых устройств (счетчики, тригеры, дешифраторы и т.д.), которым если следовать тогда взаимопонимание Ваше с синтезатором будет 100%. Иначе будет очень плохо.

-

Согласен :cheers:

-

Так я Вам и предоставил описание на VHDL. Попытаюсь Вам объяснить период формируемого сигнала это 0 - максимальное значение счечика. Как Вы уже правильно поняли с помощью компаратора формируется "еденичный полупериод" и "нулевой полупериод" |-------1--------|________0_______|----------1-и так далее. Если Вам нужен переменный коэффициент деления - делаете счетчик с предустановкой или производите его сброс по достижении определенного значения (можно сделать второй компаратор, по которому производиться сброс счетчика, а значение ему подается на вход.), таким образом уменьшаете период сигнала. Можно сделать если у Вас коефициентов деления некоторое постоянное число (N), можно сделать N параллельно вставить мое описание, а выходы пропустить через мультиплексор (N в 1). Таким образом, управление сводиться к управлению мультиплекссором.

-

Так Ваша идея полностью реализована в привенных примерах (в моем VHDL описании и в описании на Verilog предоставленном MAXXXX (PS на первый взгляд и беглом просмотре предоставленного MAXXXX описания)). Я привел даже краткое описание работы. Вы проверяли предложенные описания и пытались понять их, разобраться в них? Чем они Вас не устраивают конкретно? Что именно Вам не понятно? обсуждение похожих вопросов: ссылка ссылка

-

Попробуйте так library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity shim is Port ( clk : in STD_LOGIC; kod_in : in STD_LOGIC_VECTOR (15 downto 0); out_shim : out STD_LOGIC ); end shim; architecture Behavioral of shim is signal count_shim : STD_LOGIC_VECTOR (15 downto 0); begin process (clk) begin if clk'event and clk = '1' then count_shim <= count_shim + "0000000000000001"; end if; end process; process (clk) begin if clk'event and clk = '1' then if count_shim < kod_in then out_shim <= '1'; else out_shim <= '0'; end if; end if; end process; end Behavioral; Первый процесс описывает 16 разрядный счетчик, а второй описывает компаратор. Компаратор сравнивает значение счетчика со значением, которое подается на вход kod_in и соответственно формирует выход: if count_shim < kod_in then out_shim <= '1'; else out_shim <= '0'; end if;

-

на мой взгляд это уже нюансы - главное слово описание :) :) :) наверное здесь никогда не будет найден общий знаменатель :laughing: Мне кажется здесь каждый отстаивает, то что ему ближе, но с сутью на мой взгляд здесь все согласны. Сейчас идет посто "придерание к словам/выражением" - это обычно не приводит ни к чему хорошему! PS Давайте останемся каждый со своим мнением. Ребята давайте жить дружно! (Кот Леопольд). :)

-

пример ссылка

-

процесор реализован внутри ПЛИС? --да, тогда может стоит подумать как реализовать ввод/вывод отдельно(насколько я помню(уточните, так как Вы не указали тип и производителя ПЛИС) в ПЛИС буферы с Z состоянием имеются только в блоках ввода-вывода); --нет(процессор не внутри ПЛИС), тогда через двунаправленный ввод/вывод(через Z состояния) и никаких проблем. PS Посмотрите архитектуру ПЛИС

-

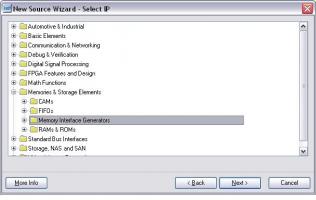

Это написано Userguide (ссылка на него ниже) для ISE 10.1.03 The Memory Interface Generator (MIG) generates DDRII SRAM, DDR SDRAM, DDR2 SDRAM, QDRII SRAM, and RLDRAM II interfaces for Virtex®-4 FPGAs and generates DDR SDRAM, DDR2 SDRAM, QDRII SRAM, and and DDRII SRAM interfaces for Virtex-5 FPGAs. It also generates DDR and DDR2 SDRAM interfaces for Spartan®-3, Spartan-3A, Spartan-3E, and Spartan-3A DSP FPGAs. The tool takes inputs such as the memory interface type, FPGA family, FPGA devices, frequencies, data width, memory mode register values, and so forth, from the user through a graphical user interface (GUI). The tool generates RTL, SDC, UCF, and document files as output. RTL or EDIF (EDIF is created after running a script file, where the script file is a tool output) files can be integrated with other design files. ссылка Для ускоррения разработки может стоит и поставить ISE 9.1.03 или 9.2.03 или даже более поздние версии (насколько я помню там MIG поставляется отдельно) но это Вам решать самому :) Ниже приведен скриншот где искать сам MIG в ISE 10.1.03

-

Квадратный корень

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

спасибо, но это чуть-чуть не то что надо -

обновил DDS, просто ранее я его удалил DDS.pdf

-

Я проголасовал за описание схемы. Так как напимер по многим книгам в определении и назначении языка VHDL звучат именно эти слова. Источники: Osnovy_Jazyka_VHDL_Bibilo_2002.djvu Сергиенко_VHDL для проектирования вычислительных устройств_2003.djvu Суворова Е.А. Шейнин Ю.Е. Проектирование цифровых систем на VHDL.djvu и т.д. PS Да и по форуму правят, если кто-то говорит что написал "программу на HDL языке" на "описание цифровой схемы(автомата, вычислителя, процессора)"

-

Квадратный корень

Maverick_ ответил Maverick_ тема в Языки проектирования на ПЛИС (FPGA)

Ее самую. Прямое попадание!!! :) Пока думаю производить сравнение следующего значения в квадрате с подкорневым значением. формула из п.6 (которую требуется реализовать), по ссылке приведенной ниже формулы для N =16, короче итоговое значение N кратное степени двойки, чтобы вместо деления можно было выполнить обычный сдвиг. Межу соседними отсчетами имется 16-18 тактов. Большое спасибо буду разбираться -

Согласен Так можно, сделать несколько основных страниц для каждой тематики и одну главную (корневую) для выбора тематики PS это мое предложение

-

Квадратный корень

Maverick_ опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Возможно ли реализация вычисления квадратного корня за один(максимум 2-4 тактов, чем меньше, тем лучше) такт 100 МГц частоты. Если да, подскажите где и куда копать. Интересуют различные алгоритмы и реализации Кристал фирмы Xilinx Spartan 3 - XC3S400 PS Данные 16 битные. PS PS Я начал смотреть в табличный вариант реализации. -

вопрос о Verilog

Maverick_ ответил MechaniX тема в Языки проектирования на ПЛИС (FPGA)

PS и что из этого следует? -

вопрос о Verilog

Maverick_ ответил MechaniX тема в Языки проектирования на ПЛИС (FPGA)

Почему Вы так считаете? PS я бы Вам рекомендовал прислушаться к des00 -

Реализация БПФ на ПЛИС

Maverick_ ответил ZED тема в Языки проектирования на ПЛИС (FPGA)

Полностью согласен Sefo - очень классный учитель, хорошо и толково объясняет!!! Дай Бог чтобы у них все получилось!!! ZED - не в обиду будет сказано, хороший ученик и видно, что хочет дойти до конца и во всем разобраться! PS Надеюсь своим детищем поделяться :rolleyes: -

вопрос о Verilog

Maverick_ ответил MechaniX тема в Языки проектирования на ПЛИС (FPGA)

можно вопрос: почему частота должна быть в 16/32 раза выше, а например не в 2/4/8 раза выше? Просто для манчестера тоже берется тоже частота в 16 раз выше. -

Оцените протокол

Maverick_ ответил левша тема в Документация

1. Плиз заархивируйте word документ, тогда он будет занимать намного меньше места. 2. Вы наверное ошиблись веткой - если протокол под какой-то мкропроцессор/микроконтроллер то там и надо оставить данный пост, если реализация протокола будет под ПЛИС - то ветка, где обсуждается работа с ПЛИС. Здесь скорее всего Вам не подскажут. 3. Пользуйтесь тегами. 4. Посмотрите протокол ModBus, ProfiBus PS Это мое мнение.