-

Постов

1 951 -

Зарегистрирован

-

Посещение

Весь контент sonycman

-

Проверьте, почему образ zimage побился. Вы используете уже готовые файлы прелоадера, юбута и линукса или собирали сами?

-

Сорри, вы же про включение моста... Приведите полностью текущий скрипт u-boot.scr Судя по логу, прошивка ПЛИС загружается нормально, вот в этом месте: reading soc_system.rbf 7007204 bytes read in 331 ms (20.2 MiB/s) ## Starting application at 0x3FF79584 ... ## Application terminated, rc = 0x0 Если пины bootsel выставлены правильно на загрузку с SD карты, то флеш epcs не должна считываться никоим образом.

-

Настроить пины надо будет всё равно: // Setup GPIOs // Reset GPIO module alt_gpio_init(); ALT_GPIO_CONFIG_RECORD_t gpio_init_pins[] = { // HPS_LED { ALT_GPIO_1BIT_53, ALT_GPIO_PIN_OUTPUT, ALT_GPIO_PIN_LEVEL_TRIG_INT, ALT_GPIO_PIN_ACTIVE_LOW, ALT_GPIO_PIN_NODEBOUNCE, ALT_GPIO_PIN_DATAZERO }, // HPS_KEY { ALT_GPIO_1BIT_54, ALT_GPIO_PIN_INPUT, ALT_GPIO_PIN_LEVEL_TRIG_INT, ALT_GPIO_PIN_ACTIVE_LOW, ALT_GPIO_PIN_DEBOUNCE, ALT_GPIO_PIN_DATAZERO } }; status = alt_gpio_group_config(gpio_init_pins, ARRAY_COUNT(gpio_init_pins)); assert(status == ALT_E_SUCCESS); И затем уже можно будет изменять значение на пине функцией alt_gpio_port_data_write

-

Что значит "в fpga прошивка по умолчанию"? Сгенерируйте свою прошивку и положите её на карту памяти под именем soc_system.rbf, затерев таким образом оригинальную. Скрипт uboot изменять не нужно.

-

Можно отбросить Yocto и попробовать Buildroot. Я делал сборку по этому гайду. Плата тоже DE10-Nano. Проблем особых не было.

-

Попробуйте выполнить на хосте: $ sudo apt-get install gawk wget git-core diffstat unzip texinfo gcc-multilib \ build-essential chrpath socat cpio python python3 python3-pip python3-pexpect \ xz-utils debianutils iputils-ping Required Packages for the Host Development System

-

Ну а если проверить, почему компилятор на хост машине даёт ошибку? Попробуйте скомпилировать любой исходник для хоста.

-

Так от конденсатора хуже не будет для FPGA, у которых нет триггеров шмидта на входах? Кондёр сделает фронты более пологими, что может привести к многократному переключению на входе в момент перехода сигнала через пороговый уровень.

-

Доброго! Да, как уже подсказали, нужен антидребезг. Это либо простой фильтр с достаточным временным периодом (десяток-другой миллисекунд), либо просто считывание состояния кнопки с ещё большим периодом, к примеру - один раз в 100 миллисекунд.

-

Казалось, что современный инструментарий как раз всё больше уходит от рисования схем. Я за Verilog.

-

Аналогично было. Я не стал парится, а просто положил пустой файл с именем cstdbool в папку с исходниками и проблема ушла. Нужные исходники hwlib тоже пришлось скопировать в отдельную папку проекта, чтобы они подключились и компилировались. По поводу эклипса и билда - использую компилятор ARM, и в настройках C/C++ Build у меня включено Generate Makefiles Automatically. Работает чётко, все изменения в проекте отслеживаются правильно, компилируются только модифицированные файлы. Это интегратор системы, в котором задаются настройки модулей и их соединения. В том числе QSys генерирует код, на основе которого загрузчик будет инициализировать процессор, настраивать пины, SDRAM, PLL и т.д. К примеру, пины GPIO настраиваются в свойствах HPS на вкладке Peripheral Pins. А планировщик ножек - это PinPlanner. Вы бы матчасть поизучали получше. Иначе SoC вам поднимать будет непросто :) Вот в GHRD всё, что надо, подключено, изучайте его. Загрузчиком - bootloader называется. Тут было несколько тем, где подробнее разжёвано.

-

Попробуйте сначала хотя бы снять сигнал сброса с модуля GPIO, вызвав alt_gpio_init() В настройках HPS в QSys нужные пины настроены как GPIO?

-

Вероятно, здесь ошибка в коде hwlib библиотеки от Альтеры. Посмотрите код функции сброса флага прерывания alt_gpio_port_int_status_clear: /******************************************************************************** ********/ /* Clear the interrupt pending status of selected signals of the specified GPIO */ /* register. */ /******************************************************************************** ********/ ALT_STATUS_CODE alt_gpio_port_int_status_clear(ALT_GPIO_PORT_t gpio_pid, uint32_t clrmask) { volatile uint32_t *addr; if (clrmask & ~ALT_GPIO_BITMASK) { return ALT_E_ERROR; } if (gpio_pid == ALT_GPIO_PORTA) { addr = ALT_GPIO0_INTSTAT_ADDR; } else if (gpio_pid == ALT_GPIO_PORTB) { addr = ALT_GPIO1_INTSTAT_ADDR; } else if (gpio_pid == ALT_GPIO_PORTC) { addr = ALT_GPIO2_INTSTAT_ADDR; } else { return ALT_E_BAD_ARG; } /* argument error */ alt_write_word(addr, clrmask); return ALT_E_SUCCESS; } Как видно, запись идёт в регистр статуса gpio_intstatus, который вообще read only и никак не может сбросить флаг. Правильный регистр - gpio_porta_eoi. Исправьте код функции, заменив для всех портов адрес ALT_GPIOx_INTSTAT_ADDR на ALT_GPIOx_PORTA_EOI_ADDR.

-

Спасибо, запустил уже обмен через ACP. Когда данных не много, пусть лежат себе в кэше, даже запись в SDRAM может не потребоваться. ЗЫ: не знаю, как у хилых, но у альтеры создание порта AXI не очень удобно - требуется, чтобы присутствовали практически все сигналы для всех каналов - и записи, и чтения. Было бы лучше, если бы система QSys не заставляла описывать не используемые каналы.

-

Интересно, а у Xilinx тоже, при создании модуля с шиной AXI, необходимо создавать абсолютно все сигналы для всех каналов? Например, если нужен только канал записи - сигналы канала чтения все равно требуется описывать?

-

Вышла новая книга RTL Modeling with SystemVerilog for Simulation and Synthesis: Using SystemVerilog for ASIC and FPGA Design. Буду премного благодарен, если кто даст ссылочку. А вообще хотелось бы печатный вариант, но дешевле будет самому распечатать, чем у буржуев покупать за 120 долларов...

-

Не верю :) VHDL - это просто жуткое количество совершенно лишнего текста. Verilog же - компактный и красивый язык. Ещё бы заменили begin\end чем нибудь кототеньким... :)

-

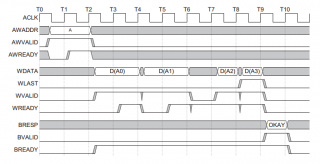

Спасибо, учту на будущее. Хотя в моём случае проблема была в том, что я поднимал awvalid и ждал, когда в ответ поднимется awready. А слэйв со стороны моста поднимает awready только тогда, когда будут активны и awvalid, и wvalid. Подправил код и все пошло...

-

Хочу записывать данные сразу в кэш процессора, а для этого записывать их надо через ACP (Accelerator Coherency Port) порт. Этот порт требует установки линий AWCACHE и AWUSER, которых в Avalon-MM нет. Видел посты буржуев, что они всё равно работают в этом случае через Avalon, но путём правок сгенерированных файлов interconnect вставляют нужные AWCACHE и AWUSER. Но это чистое шаманство и необходимость править файлы на низком уровне после каждой генерации - глупость какая-то. Поэтому логично было бы вместо авалона (и обёртки Avalon -> AXI, которую генерирует QSys) использовать напрямую AXI. Вроде простая шина, но вот затык случился нехороший... Авалон очень удобно работает - присутствует только то направление, которое нужно - только запись, к примеру, или только чтение с минимумом сигналов. AXI вроде тоже имеет независимые каналы записи и чтения, но при создании модуля в QSys порт AXI требует наличия ВСЕХ сигналов, и для записи, и для чтения, не зависимо от того, используются ли они в коде. У меня чтение не используется, и я просто жёстко задал неактивные уровни для этого канала. Может быть это и является причиной, по которой синтезатор удаляет шину? И пофигу ему, что запись-то необходима! Может, стоит попробовать 17 версию квартуса? Хотя не думаю, что поможет, если честно... Нашёл косяк, с моей стороны, конечно. Ещё раз повнимательнее почитал условия транзакций, и понял, что нарушил парочку: Слишком много свободы и вариативности ;)

-

Приветствую! Плис SoC Cyclone V, в QSys собрана HPS и несколько подключенных модулей, все на AvalonMM. Проблем не было. Но вот пробую добавить ещё один свой модуль, подключить надо к мосту FPGA-HPS теперь уже через AXI шину (надо тянуть AxCACHE и AxUSER линии). Нужно всего-то записывать около сотни байтов в память HPS. Написал простенький AXI мастер, подключил в QSys - всё нормально вроде бы, компилируется и синтезируется, но Квартус, собака, выкидывает после оптимизации почти весь код модуля! Как я понял, шерстить он начинает внутренности сгенерированного QSys интерконнекта (судя по логам), а затем выбрасывает и мой модуль, так как считает, что данные отправить мне уже никуда не получится... :( Если путём недолгих корректировок заменить AXI на Avalon - то всё остаётся на месте, ничего лишнего не "оптимизируется". Что же за чертовщина получается? Может, я что-то не то делаю, как правильно организовать обмен по AXI? Вот кусок кода с записью одного слова, простая машина состояний адрес->данные->ответ: always_ff @(posedge clk or negedge reset_n) begin if (!reset_n) begin axi_state <= 0; axm_awvalid <= 0; axm_wvalid <= 0; axm_bready <= 0; axm_awaddr <= 0; axm_wdata <= 0; start <= 0; end else begin if (avs_write) begin if (!avs_address) axm_awaddr <= avs_writedata; else begin axm_wdata <= avs_writedata; start <= 1'b1; end end case (axi_state) 2'd0: begin if (start) begin axm_awvalid <= 1'b1; start <= 0; axi_state <= 2'd1; end end 2'd1: begin if (axm_awready) begin axm_awvalid <= 0; axm_wvalid <= 1'b1; axi_state <= 2'd2; end end 2'd2: begin if (axm_wready) begin axm_wvalid <= 0; axm_bready <= 1'b1; axi_state <= 2'd3; end end 2'd3: begin if (axm_bvalid && axm_bid == axm_awid) begin axm_bready <= 0; axi_state <= 0; end end endcase end end Делал на основе этой диаграммы: Версия квартуса 16.0.1, попробую обновится на днях...

-

Расчет CRC16 для прошивки

sonycman ответил zheka тема в В помощь начинающему

При записи флеш памяти её биты могут только устанавливаться в 0. То есть стёрли страницу - все биты в 1. Записываем - нужные биты сбрасываются в 0. Если у вас после первой записи содержимое по адресу +2 будет отличаться от 0xFFFFFFFF, то последующая запись будет неверной. -

Расчет CRC16 для прошивки

sonycman ответил zheka тема в В помощь начинающему

Так первое слово у вас двухбайтное, поэтому оно не портится. А портится четырехбайтное слово потому, что по адресу page_address+2 значения, отличные от 0xFF, из-за первой записи. -

Блин, почитал внимательнее доку по хардовому контроллеру DDR SDRAM - для шины Авалон нет поддержки подтверждения записи (write response). Получается, нужен AXI. Насколько я понял, в циклоне AXI-3. Попробую написать мастер для записи. Подумал тут - лучше воспользоваться портом ACP, чтобы сразу делать запись в кеш процессора. Будет быстрее, чем напрямую в sdram. Кто нибудь работал с ACP? Там кучу условий надо выполнить. Доступ к нему через мост FPGA->HPS, который AXI3, но что интересно - для доступа к ACP нужны сигналы AxUSER AXI4! Я не пойму, почему такая мешанина разных шин?

-

Да, спасибо! Данные пойдут через AvalonMM Master -> мост FPGA->HPS и дальше ->L3 Interconnect->32 bit AXI->SDRAM Controller. То есть сигналы write response со стороны AXI должны быть автоматически согласованы Qsys Interconnect с сигналами response моего AvalonMM Master. Буду пробовать!

-

На цинке нет авалона, там сложный AXI. В нём, наверное, есть спец. линии, подобные response в авалоне.