Flood

-

Постов

1 801 -

Зарегистрирован

-

Посещение

-

Победитель дней

3

Сообщения, опубликованные Flood

-

-

Слышал, что в аналогичной ситуации с ZynqMP произошел такой суровый клинч, из-за которого Xilinx пришлось вводить отдельный SCD с запретом шифрования. И только такие Цинки сюда поставлялись.

А сейчас, насколько я понимаю, их выпуск прекращен за ненадобностью (т.к. среди официальных потребителей ZynqMP не осталось тех, кому бы требовалось отключение шифрования)

-

25 minutes ago, BSACPLD said:

Китайские.

А есть данные, речь про 15 деталей одного вида, или 15 вообще чего-либо похожего? Ну, можно ли 15 одних квадратиков и 15 чуть других квадратиков? 🙂

А если у меня бобина, но одна?

Сорри за оффтоп, но вдруг пригодится.

-

2 hours ago, BSACPLD said:

До 15 шт. на человека можно провозить вполне законно - мы уточняли на китайской таможне. Только в таком случае нужно отправлять сразу много курьеров - не выгодно.

15 шт - это китайские правила?

А если вывозить в Гонконг?

-

4 hours ago, HardJoker said:

Поясните, как соотносится "реинжиниринг" и "(возобновление выпуска) ранее разработанного..."?

Строго говоря, тут же не написано, кем именно оно было ранее разработано? 🙂

А по сути - более-менее понятно, о чем идет речь. Есть исходники, нужно их дорабатывать, в частности менять элементную базу на доступную. Если я правильно все понял - вполне нормальная задача, ничего необычного.

-

On 1/23/2024 at 3:11 PM, makc said:

Это не первый такой опыт на эту тему, правда в прошлый раз подобный проект использовался для проверки устойчивости работы источников питания ядра ПЛИС при высокой нагрузке (большой %% занятости, максимальная частота). До 18А работало, а потом источник не выдерживал.

А какие ориентировочно удавалось выжать токи из Артиксов и Кинтексов?

Думаю, какой источник на ядро для чипов до 7A200T и до 7K325T поставить. По VCCAUX же большого тока не возникает? Пары ампер хватит?

-

2 hours ago, MGMT said:

Долгое время у меня не было времени вести свой блог, до недавнего времени.

Спасибо, у вас интересный блог с полезным материалом!

-

Возможно, чем-то типа лазера для очистки ржавчины удаляют слой маркировки?

-

1 hour ago, selax said:

А зачем это знать? Скорее всего из того, что на нём написано. 🙂

2. Скрыть, что чип б/у.

Да, согласен, что дело в б/у.

Но все-таки хотелось бы знать спидгрейд, который на поддельной маркировке не указан (а был бы указан - не было бы особого резона ему верить). А в оригинальной - в той или иной форме присутствовал.

-

30 minutes ago, selax said:

Да, но зачем она вам? И так всё ясно.

Ясно, что чип пиленый, но не ясно, из чего 🙂

-

4 hours ago, selax said:

Вот сюда (красным выделил).

Да, текстура значительно отличается от оригинальной и слегка заходит на края. Но ведь поверх этой текстуры выжжены лазером символы маркировки, и они совсем не такого цвета (а вполне привычного).

Это разные лазеры, или разные режимы их работы? И как они получают такую шероховатость (а не прожженные линии)?

Правильно понимаю, что оригинальная маркировка полностью потеряна?

-

2 hours ago, jcxz said:

Так что правильный обмен по PPS-профилю (или по AVS-профилю) посмотреть негде.

Посоветовал бы купить такой брелок, модели C4 или C5. Читает профили с источников и триггерит что угодно. Может вставать в разрыв.

-

25 minutes ago, Vasily_ said:

Сожгли лазарем, это четко видно на фото.

Подскажите, куда и на что смотреть, чтобы это понять?

-

Ради интереса спилил фейковую маркировку. Увы, старой маркировки под нею не было.

Похоже, верхний рыхлый слой был более черным, чем основное тело заливки микросхемы, и он довольно легко сошел при новой шлифовке. Выглядит так, будто старую маркировку сошлифовали, затем чем-то типа набрызга нанесли новый рыхлый слой, оказавшийся чуть чернее старого корпуса. И на этот слой уже нанесли новую маркировку.

Сужу в основном по центральному углублению - оно менее глубокое, чем на нормальных микросхемах.

-

8 hours ago, jcxz said:

Но даже здесь похоже напряжение выбирается из фиксированного профиля "Fixed 28V 5A". И в последовательности запросов/ответов не вижу ничего принципиально отличающегося от аналогичной последовательности при работе моей программы.

Похоже, между пакетами 57 и 523 в этом примере происходил периодический обмен сообщениями.

Возможно, один из простых вариантов - сделать вариант вашей программы сниффером PD и посмотреть, какие идут обмены между БП и "правильным" PD триггером в различных режимах.

Я когда-то хотел разобраться с PD, но изучив документацию и рынок, просто поставил CH224K 🙂

-

6 hours ago, keats sun said:

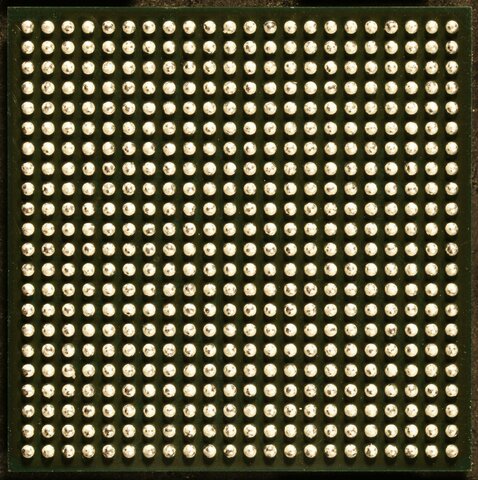

Спасибо за предоставленные фотографии. Судя по деталям на фотографиях, можно с уверенностью сказать, что эта деталь является отремонтированной,На подложке можно увидеть явные царапины, которые являются следами удаления оригинальных шариков припоя.

Да, похоже это так. Спасибо!

-

On 1/23/2024 at 4:59 PM, jcxz said:

Где бы найти дорожные карты (блок схемы алгоритмов) обмена потребитель<->источник для разных сценариев работы? Чтобы понять - что ему ещё нужно?

Понятно, что основа - в стандарте, но некоторые примеры можно найти здесь:

https://usbchargingblog.wordpress.com/

И даже сложные случаи частично описаны:

-

Да уж, интересно было бы посетить этот Huaqiangbei, посмотреть как там дела делаются 🙂

Вот только без хорошего знания языка там, скорее всего, и не увидишь ничего.

-

34 minutes ago, sazh said:

Вопрос - это семейство снято с производства?

Нет, чип актуальный. И довольно дешевый, особенно у продавцов на Али.

Если чип восстановленный, то понятно что реболл там был. Но так заморочиться с крышкой, ух. Я пока не смог даже разобраться, есть ли там шанс увидеть родную маркировку.

-

На вашем даташите довольно экзотический вариант, в котором два сдвоенных контакта разделены одиночным.

Более распространенный вариант - когда пара сдвоенных контактов идет вместе (и то, не все такие разъемы совместимы по порядку выводов).

Видимо, RUICHI также унифицировались с этим вариантом расположения выводов.

Вот только делать это под тем же партномером, что раньше был с другим пинаутом - ну, это додуматься надо...

Но вот пример похуже, пины выглядят одинаково, но их порядок отличается.

Розетка HRO PARTS TYPE-C-31-M-12 - "китайский" пинаут, такой же как у новых Ruichi. Стандарт де-факто для большинства китайских Type-C USB2.0.

Розетка JAE DX07S016JA1R1500 - с виду почти такая же, но пинаут другой, соответствующий более позднему варианту, принятому в официальной спецификации Type-C.

Найдите разницу 🙂

-

15 minutes ago, makc said:

Судя по фотографии либо радикально упало качество изготовления подложек корпусов (что маловероятно), либо это корпус после довольно аккуратного реболлинга (наиболее вероятно).

На основании царапин? Конечно, похоже на реболл.

Хотя, когда я реболлю, царапин бывает поболее 😞

-

-

lspci

Существует под Linux и Windows. Насчет DOS не знаю, но вполне возможно.

-

27 minutes ago, Evgenij said:

ЗАМЕНА в port map VCC на V не всегда помогает

ПРИМЕР: ERROR (EX4916) : Formal v is not declared("C:\Users\e.svirin\Documents\fpga_project_1V7MI850 VHDL UST\src\TOP.vhd":11083)

Какую вообще задачу вы пытаетесь решить? Переписать синтезированный нетлист с верилога на VHDL? 🙂

Вы показываете абсолютно бесполезные примеры. Не видя ваших исходников невозможно сказать, что у вас там происходит в 11083 строке. Повторюсь, к свойствам языка этот вопрос отношения не имеет. Фактически, вы спрашиваете: "что в моих исходниках не так?". Как обычно в этих случаях говорят, телепаты в отпуске и силой мысли проникнуть в ваши задачи возможности нет.

Спросите у лучше тех, кто задал вам эту задачку и находится в контексте происходящего.

-

1

1

-

-

По аналогии можно предположить, что в port map для VCC будет V без точки перед ним.

ПС. Вопрос не имеет отношения ни к VHDL, ни к ПЛИСам, ни к Verilog.1 hour ago, Evgenij said:В VERILOG порт питания обозначается V ,что приведено на примере

Это у вас в примере он так обозначен, язык Verilog этого не требует.

Твердотельный накопитель NVMe M.2 2280 для любителей музыки от UDinfo

в Объявления пользователей

Опубликовано · Пожаловаться

Одно непонятно, "электролитические конденсаторы звукового класса Audionote Kaisei", а также гнездо для внешнего питания там есть, но файлы звукозаписей на нем хранить все равно нельзя. Зачем тогда конденсаторы, внешнее питание и сверхточный тактовый генератор?