-

Постов

1 220 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные PCBtech

-

-

Зависит от стоимости, а цена зависит от количества. Хотелось бы начать со 100 комплектов. Стоимость может повлиять как на уменьшение, так и увеличение кол-ва.

Скорее всего, для 100 комплектов дешевле будет заказать готовые платы по тем адресам, которые указаны по ссылкам.

Тем не менее, если есть желание, мы можем оценить такой "комплексный" заказ.

Но Вам надо будет проделать небольшую работу самостоятельно:

а) найти подходящий PCB-файл или гербер-файлы для изготовления ПП (там по ссылкам есть несколько версий, надо выбрать нужную Вам)

б) найти подходящий BOM-файл (список компонентов) - там они тоже есть, но несколько вариантов

в) прислать нам "комплексный" заказ на оценку, на email [email protected]

Если объемы заказов планируются более высокие, то лучше было бы перетрассировать плату под планарные компоненты.

Кстати, а где вы берете механику для этих принтеров?

-

Тема известная, возможно уже избитая. Готовы заказать изготовление готовых плат, если это будет дешевле, чем закупить готовые наборы в интернете.

Возможно кто-то уже делал или делает такие заказы. На сегодняшний день самым дешевым представляется вариант - http://reprap.org/wiki/Printrboard или http://reprap.org/wiki/Sanguinololu.

Здравствуйте.

В каком количестве нужны платы?

-

Вышел релиз Cadence Allegro 16.6, содержащий довольно интересные улучшения.

Из наиболее интересных новинок редактора печатных плат можно отметить следующие.

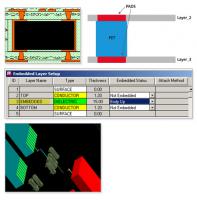

1. Встроенные компоненты:

а) Поддержка встроенных в плату компонентов с двусторонними контактами

б) Поддержка вертикальных встроенных компонентов во внутренних слоях

в) Проверки правил DRC для встроенных полостей

Пока, к слову сказать, только несколько наших заказчиков интересуются встроенными компонентами,

а вот встроенные полости уже встраивают многие, особенно для СВЧ-приложений.

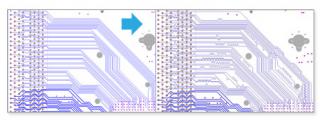

2. Более быстрое выполнение автоматического/интерактивного выравнивания задержек.

Это важно и очень полезно, т.к. процент трасс, требующих выравнивания длин на плате,

растет в проектах с каждым годом катастрофически.

3. Опция командной работы для ускорения выполнения проекта

а) Члены команды могут редактировать ограничения и перемещать компоненты

вне своей части проекта ("гибкие границы частей") без необходимости объединять части.

б) "Помощник" ECO помогает импортировать изменения в списке цепей в различные части проекта.

Это актуально для российской действительности - когда схемотехники часто меняют схему

по ходу работы над топологией, иногда чуть ли не каждый день присылая новый нетлист...

4. Авто-интерактивное свапирование выводов (pin swap) для ПЛИС прямо изнутри

подсистемы планировщика ПЛИС (Allegro FPGA System Planner).

Очень полезная функция - для тех, кто пользуется планировщиком ПЛИС.

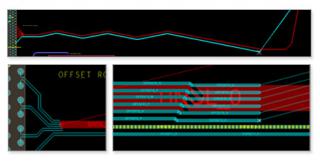

5. Режим "смещенная трассировка" позволяет пользователям трассировать под не-ортогональными углами,

чтобы предотвратить влияние направления стекловолокон в диэлектрической подложке на скоростные цепи.

Может быть актуально для сигналов частотой выше 2ГГц.

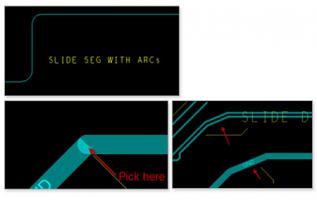

6. Новая функция Slide ("скольжение").

а) Новая опция автоподсоединения во время выполнения операции Slide упрощает процесс редактирования

топологии.

б) Возможность сдвигать сегменты со скруглениями

в) Сдвиг сегмента сохраняет углы наклона всех сегментов

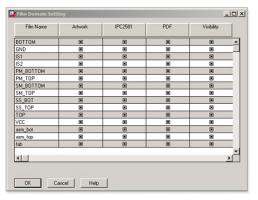

7. DFM (проектирование для производства)

а) Экспорт / импорт данных дизайна в производственные файлы в формате

открытого индустриального стандарта IPC-2581

8. Новая система управления гербер-файлами позволяет пользователю

назначить слоям фотошаблонов классы и подклассы.

9. Дополнения, упрощающие работу и повышающие эффективность разработчика

а) Режим General Edit позволяет разработчику назначать ограничения одного региона

множественным регионам.

б) Выравнивание компонентов по краю или центру с использованием правил и ограничений DFA

или правил равных расстояний (под управлением заданного пользователем правила по рассточнию

и клавиш "плюс"/"минус")

в) Поддержка копирования текстов в функции размножения фрагментов (Place/Replicate)

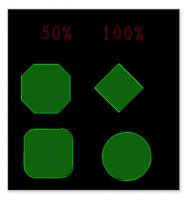

г) Функция "быстрого размещения" теперь разрешает границам компонентов перекрываться

(процент допустимого перекрытия задается пользователем), что позволяет быстрее расположить

все компоненты на площади платы.

д) Обновление символа по его Instance на схеме

е) Добавление прямоугольного полигона с различными видами углов (срезанными или скругленными)

ж) Динамические полигоны теперь позволяют задать ширину линии термального подсоединения,

равную ширине линий сетки, заполняющей сетчатый полигон.

з) Новые возможности отображения обеспечивают показ имени цепи поверх линий, площадок и полигонов.

и) Линии и тексты теперь могут быть перемещены за пределы их текущей структуры класс-подкласс.

к) Объекты на экране теперь можно выбирать с помощью "лассо" или "пересекающей линии" (удобная штука!)

л) Появилась возможность подсвечивать цепи, связанные с заданным компонентом

м) Теперь DRC можно запускать "в окне" (если глобальный он-лайн DRC выключен)

н) Можно определять любой текст для значений размерности (при образмеривании чертежей),

используя опциональное поле "Текст" во вкладке опций.

о) Теперь можно задавать разные выходные файлы для фрезеровки по контуру и для металлизированных участков контура.

п) Проверки DRC для паяльной пасты (т.е. для трафарета) проверяют очертания в Package Geometry - Pastemask_Top

и зазоры между ними, в том числе внутри компонента.

В целом редактор печатных плат действительно получил много "вкусных" улучшений,

позволяющих разработчикам многослойных плат существенно упростить и ускорить свою работу.

Также добавлено несколько полезных улучшений к опции СВЧ-проектирования (Allegro PCB RF Option),

в том числе:

1. Улучшен импорт из системы СВЧ-моделирования Agilent ADS в схемный редактор.

2. Поддержка для новой библиотеки топологических СВЧ-элементов ADS.

3. Улучшение возможностей привязки топологии (привязка к краю площадки, привязка к группе).

4. Добавить связь можно с перекрытием площадки, а можно - к краю площадки.

5. Копирование с масштабированием позволяет привязываться к краю площадки.

6. Улучшено в целом взаимодействие между средами Agilent ADS и Allegro

Источник информации:

http://www.cadence.com/products/pcb/pcb_de...s/whatsnew.aspx

----------------------------------------------------------------------------------------

Получить демо-версию:

Для ознакомления с новыми возможностями российские предприятия могут получить

бесплатные полнофункциональные демо-версии

редактора печатных плат Cadence Allegro, включая RF Option, и/или системы моделирования Agilent ADS.

Заявки на получение бесплатной демо-версии присылайте по адресу [email protected]

-

Здрасьте,

Есть вопрос: достал поставщик своей нестабильностью и хотелось бы "сколоть" несколько простых плати переразвести под номвый дизайн корпуса, может ли кто-либо с этим помочь, и на каких условиях?

Вам поможет Яндекс:

-

Коллеги, есть следующая проблема: наши контрагенты не успевают в срок закорпусировать кристаллы в нужный нам тип корпуса (FBGA400), могут сделать только FBGA256. Тестовая плата разработана под первый корпус. Реально ли где-нибудь сделать платку-переходник с FBGA256 на FBGA400? Срок 2-3 недели.

У нас где-то за 4-5 недель можно сделать, включая проектирование топологии.

Если подойдет - пишите на [email protected]

-

Какие компании с российской стороны представляют FP?

Компания PCB technology, юридическое лицо ООО "ПСБ технологии", сайт www.pcbtech.ru

является официальным дистрибьютором компании China Fastprint на территории России, Украины и Беларуси.

Компания осуществляет консолидацию грузов от Fastprint, услуги по официальному таможенному оформлению

с уплатой таможенных пошлин и НДС, русскоязычную техническую поддержку заказчиков,

а также обеспечивает решение спорных вопросов по рекламациям от заказчиков (очень редко, но бывает, если заказы очень сложные).

Имея дилерские скидки от поставщика, PCB technology может предложить заказчикам

очень выгодные цены на многослойные платы (от 2 шт. до 1000 шт.), с оплатой в рублях,

с возможностью пост-оплаты, с доставкой заказчикам по всей территории России, Украины или Беларуси.

Возможен монтаж ваших многослойных плат (от 1 шт. до 1000 шт.), включая QFN, BGA с рентген-контролем, 0402, 0201 итд.,

и поставка ЭРИ для комплексного выполнения ваших заказов.

Дизайн-центр компании выполняет скоростное проектирование топологии многослойных плат

по схеме заказчика, с обеспечением целостности сигналов, что ускоряет выполнение разработок заказчиками.

Решаем задачи "в комплексе".

Обращайтесь, будем рады помочь.

С уважением,

Александр

-

На внутренних слоях мы так делали и делаем: иногда сами "заливаем", иногда производитель плат (с нашего согласия или по нашей просьбе).

Но вот чтобы такой способ выравнивания применять на внешних слоях?.... Не встречалось в моей практике такого.

А в чем противоречие?

Внешние слои даже более критичны к дисбалансу меди, чем внутренние. Коробление платы при монтаже может быть из-за этого довольно сильным.

А с точки зрения работы схемы заливка полигоном может помешать существенно больше, чем точками. Согласны?

-

За несколько лет, что холдинг PCB technology занимается поставкой и внедрением САПР Cadence Allegro/Orcad на российских предприятиях,

у нас накопилось немало информации о возможностях и особенностях этой замечательной системы проектирования печатных плат.

Думаю, что тем, кто покупает у нас лицензии САПР, крайне важна такая методологическая поддержка - это позволяет инженерам-конструкторам

гораздо быстрее осваивать новый САПР, не "тормозить" в ситуациях, когда возникает потребность в новой "продвинутой" функции,

а предприятию в целом - существенно повысить качество и эффективность разработок.

Мы решили сделать на форуме подборку из некоторых наших статьей. Надеемся, что и тут они пригодятся.

- Тем, кто выбирает новую, более продвинутую САПР, и хочет понять,

чем САПР Cadence Allegro лучше других, будут интересна информация о мощных функциональных возможностях.

- Тем, кто уже осваивает Cadence Allegro, статьи помогут найти правильный алгоритм действий, нужную "кнопку" или "пункт меню".

- Для профессиональных пользователей Allegro могут быть интересны методические рекомендации,

изложенные в некоторых статьях.

В целом, этот цикл статей предлагает некую концепцию "удобного и правильного" использования этого мощного пакета.

Надеемся, что это будет полезно читателям форума.

Взаимодействие инженера-схемотехника и инженера-конструктора. Компоненты.

Один из основных принципов успешности бизнеса — это минимальное время,

которое затрачено от момента возникновения идеи до создания готового продукта.

То, что принято называть временем выхода на рынок, или “Timetomarket”.

Во многом оно зависит от эффективности отдела разработки, от того,

насколько полноценно загружен каждый сотрудник, насколько четко

осуществляется взаимодействие между ними.

Ввод механического чертежа в проект печатной платы

В прошлой статье было рассказано, как именовать компоненты и на что

обращать внимание при создании библиотеки посадочных мест, или символов.

В этот раз мы рассмотрим следующий этап — так называемую «механику»,

то есть механическую часть проектирования ПП.

Размещение компонентов на печатной плате как основа успешной разработки

В предыдущих главах мы рассмотрели общие положения проектирования, взаимосвязь

между инженером-схемотехником и разработчиком печатной платы. Автор рассказал

о принципах построения библиотеки компонентов и определении механических

параметров ПП при помощи САПР Allegro фирмы Cadence. В этот раз мы поговорим

о размещении компонентов на ПП (то есть о так называемой «компоновке»).

Трассировка печатной платы.

Часть 1 — Fanout

В цикле, который продолжает эта статья, мы знакомимся с основными правилами

конструирования печатных плат, а также разбираем, как можно решить те или иные

задачи при помощи одного из ведущих редакторов проектирования печатных плат — САПР

Allegro фирмы Cadence. Ранее мы познакомились с построением библиотеки компонентов,

правилами и возможностями их компоновки на плате.

В этот раз мы поговорим о трассировке.

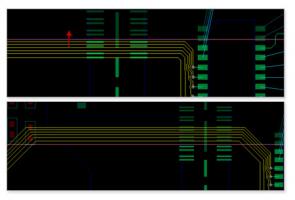

Трассировка печатной платы.

Часть 2. Задание исходных данных

Редактор печатных плат Cadence Allegro позволяет выполнять работу по трассировке печатных плат

любой сложности с максимальной эффективностью и минимальными затратами по времени.

После выполнения процесса Fanout, о котором мы говорили в предыдущей статье, начинаем

трассировку с задания исходных данных.

Подготовка рисунка маркировки

Эта глава цикла посвящена методологии формирования рисунка маркировки на печатной

плате (Silk Screen), а также построению чертежей для автоматической ее сборки.

Описание процессов относится к интерфейсу САПР Cadence Allegro, но изложенные

приемы можно с успехом применять и в других современных САПР.

Управление параметрами сигналов при проектировании высокоскоростных печатных плат.

Часть 1

Инженер-электронщик, имеющий дело с цифровыми и цифро-аналоговыми платами

с высокой частотой сигналов, вынужден одновременно решать проблемы по нескольким

направлениям: обеспечение контроля целостности сигналов; электромагнитная

совместимость; распределение питания в схеме.

Современный дизайн высокоскоростных печатных плат требует совмещения многих данных

и эффективного управления ими в процессе разработки, что, в свою очередь,

ведет к повышению качества разработки и сокращению времени выполнения проекта

(time to market). Как следствие, системы управления данными стали одним из главных

инструментов в разработке печатных плат.

Управление параметрами сигналов при проектировании высокоскоростных печатных плат.

Часть 2

В предыдущей части мы научились создавать группы сигналов и определять для них

законы по расстоянию между объектами.

Подобным образом определяются и физические параметры для группы сигналов.

Ускоренное проектирование печатных плат

за счет разделения проекта между несколькими разработчиками

В современных условиях, когда время выхода продукта на рынок (time to market) является

одним из основных факторов успеха предприятия, возможность редактора печатных плат

по увеличению скорости выполнения проектов становится очень важным свойством САПР

печатных плат, используемой на предприятии.

Разработка печатных плат –

как сократить время компоновки элементов

В процессе разработки печатной платы этап компоновки элементов

является, пожалуй, самым трудоемким и ответственным. Зачастую

процесс проектирования ведется в авральном режиме, когда сроки

выпуска готового изделия уже “поджимают”, поэтому быстрота

выполнения каждого этапа проектирования очень важна. В статье

рассматривается несколько способов повышения скорости и эффек-

тивности компоновки элементов на плате.

Организация процесса безошибочной разработки печатных плат

внутри предприятия и на аутсорсинге.

Перефразируя забытого ныне классика, можно утверждать,

что революция в умах, о которой так долго говорили сторонники

аутсорсинга в области конструирования электроники, свершилась.

Все больше частных компаний и организаций переходят на организа-

цию процесса разработки и изготовления электронных узлов

и приборов, связанную с привлечением не только сторонних

сборочных производств, но и сторонних дизайн-центров.

О достоинствах аутсорсинга было сказано немало. Но надо

понимать, что невозможно говорить об успехе процесса

разработки, не имея четкой организации в подразделениях

и между ними в процессе работы над проектом.

Оптимизация работы в редакторе печатных плат

за счет применения служебных программ («скриптов»)

Цикл статей руководителя дизайн-центра печатных плат КБ «Схематика» посвящен

повышению эффективности, скорости и качества работы инженеров‑конструкторов

многослойных печатных плат. Предлагаемый вашему вниманию материал описывает

механизмы применения «скриптов» — служебных программ, позволяющих существенно

ускорить работу инженера при выполнении типовых рутинных операций.

Принципы "проектированиядля производства"

при интерактивной компоновке элементов на печатной плате

В статьях, посвященных проектированию электронных сиcтем, неод-

нократно подчеркивается, что процесс размещения компонентов на

печатной плате – наиболее важный этап выполнения проекта. Одно

из основных условий грамотной компоновки является определение

зоны ограничений по расстоянию между компонентами на уровне

построения символа в библиотеке компонентов. Рассмотрим способ

определения таких зон при "проектировании для производства"

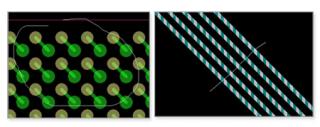

Размещение переходных отверстий в планарных площадках печатной платы

При разработке современных печатных плат часто приходится стал-

киваться с необходимостью размещения в планарных площадках

сквозных переходных отверстий (VIAs), соединяющих медные про-

водящие слои печатной платы. Одна из основных проблем при фор-

мировании VIA – утечка пасты, которая может привести, с одной

стороны, к недостаточному ее количеству на площадках, а с дру-

гой – к появлению "холмиков" припоя на обратной стороне платы.

Для предотвращения утечки пасты через переходные отверстия,

обеспечения хорошей пайки термоплощадок печатных плат и отвода

тепла от них необходимо правильно описать конструкцию отверстий

и поставить перед производителем корректную технологическую

задачу по их закупориванию. Рассмотрим техническую реализацию

этой задачи в редакторе печатных плат Cadence Allegro.

Ускорение процесса проектирования печатных плат

с помощью Cadence Allegro PCB Editor.

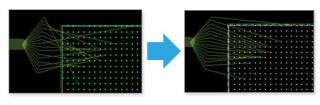

Размножение похожих фрагментов платы

При разработке МПП, содержащей много одинаковых «каналов» или «модулей памяти»,

можно ускорить процесс проектирования, если PCB-редактор позволяет автоматически

определить схемотехническую похожесть этих фрагментов и, соответственно,

«размножает» единожды сделанное на печатной плате размещение и трассировку

одного такого фрагмента. Особенно полезным может стать такое свойство,

как дальнейшее «отслеживание» изменений во фрагменте-образце.

МОДЕРНИЗАЦИЯ ПРОЦЕССА РАЗРАБОТКИ

Без модернизации процесса разработки электронных узлов нельзя ожидать

повышения качества проектов и производительности труда. В этом

убежден автор статьи – известный эксперт в области проектирования

многослойных печатных плат. Его семинары с рекомендациями по разработке

плат собирают до 150 инженеров-конструкторов различных

приборостроительных предприятий России.

-

Коллеги, с одной стороны очень приятно, что есть еще форумы с таким серьезными и одновременно чистыми людьми.

Но, простите, как-то уж наивно: "положительная статистика", "хорошая техподдежка", "маска", "годами все ОК" в ответ на тривиальный, но жирный троллинг. Уже первого поста, ИМХО, нужно было рубить по кнопке:

Да нет, почему же. По-моему, уважаемый U880, сам того не ожидая, создал тему, которая очень благотворно сказывается на имидже PS-Electro.

Посмотрите, сколько положительных откликов от заказчиков - приятно почитать.

-

На данный момент (праздники закончились) ситуация по срокам нормальная.

Среднестатистические сроки поставки ПП:

- типовой заказ 2-4 слоя - от 2.5 до 3 недель,

- 6-8 слоев - от 3 до 3.5 недель (в зависимости от количества),

- 10-24 слоя - от 3.5 до 4.5 недель.

- с микроотверстиями и скрытыми отверстиями - от 3.5 до 4.5 недель

Возможно срочное выполнение заказа с доплатой 25, 50 и 100%.

Если заказ комплексный, и плата в дальнейшем монтируется тоже у нас,

то возможна задержка запуска ПП на 1-2 дня -

дополнительная проверка топологии на корректность.

Уважаемые коллеги!Увеличиваются сроки поставки печатных плат в связи с новогодними каникулами в России (1-9 января) и в Китае (21-29 января).

Если платы нужны вам до конца января, надо запустить их в производство не позже 12 января, а лучше до 25 декабря.

Платы, ушедшие в производство после 12 января, скорее всего будут получены не ранее середины февраля.

Подробности можно получить по бесплатному телефону:

8 800 333-97-22

-

День добрый. Разрабатываю плату, размер 300х200 мм (определяется УБНК). На плате элементы (от 0603 до CQFP-208) и трассировка занимают ~20% площади (в одном углу платы).

Вопрос: Для удобства монтажа ЭРЭ пайкой оплавлением (отсутствия коробления и т.п.) оставшуюся (незанятую проводниками плату)

1) Оставить без заливки по обоим слоям,

2) Залить полигоном сплошным (меньше расход раствора травления),

3) Залить полигоном сетчатым (с какими значениями линия / зазор),

4) Ваш вариант.

САПР позволяет сделать все варианты.

Извините, что не ответил сразу - почему-то перестали приходить уведомления о сообщениях в этом подфоруме.

Можно делать полигон сетчатым, но не очень мелкой сеткой (зазоры 0.1 мм делать не надо - будет плохо,

лучше зазор и проводник 0.25 мм).

Но более удачный вариант - залить отдельно стоящими квадратиками или кружочками - так называемый "баланс меди".

Следите, пожалуйста, чтобы с обеих сторон платы и в разных участках каждой стороны платы

заполнение медью было более-менее равномерным - это хорошо и с точки зрения изготовления,

и с точки зрения монтажа. Вы монтировать собираетесь тоже у нас, или нет?

-

Всем привет! Собственно, проблема такая - есть компонент, пины стоят с шагом 2.5 мм, отформовать невозможно. Между ними 1кВ и это не моя финтазия, а реальное рабочее напряжение по даташиту. Если для внутреннего слоя требования IPC2221 (1.5мм) худо-бедно соблюсти можно, то для внешних - 2.3мм (это минимум при наличии покрытия!) - просто нереально. Что делать-то, кто подскажет? :crying:

Просто профрезеровать в плате длинные пазы шириной 1 мм или 1.5 мм.

Так обычно отделяют цепи друг от друга на высоковольтных платах.

По воздуху расстояние 1.5 мм для вашей схемы допустимо?

-

Есть сборщики в Москве, которые специализируются на небольших партиях. М-плата, АЛТ-мастер, Энфорсис, Гудвин. Это первое, что вспоминается.

С сентября 2011 г. открыт новый монтажный цех PCB technology на метро Южная

(в здании ИТМиВТ, справа от длинного здания на Варшавском ш. 125).

Специализируется на опытных образцах и мелких партиях,

производительность до 100 модулей высокой сложности в день.

Есть рентген, струйная и УЗ отмывка, ручной монтаж.

Цены не самые низкие, но для московского рынка заказов, критичных к качеству монтажа и к гарантированному сроку - вполне приемлемые.

Цена за точку пайки SMD - от 1.5 руб для прототипов до 0.2р для серий (цена зависит от сложности монтажа и объема заказа).

Типовой срок монтажа 2 недели.

Сайт http://www.pcbtech.ru/pages/view_page/18

Почта [email protected]

-

Необходимо из жести заказать двухкомпонентный экран.

Может кто нибудь заказывал экраны по Беларуси?

Необходимо пару тройку тысяч наклепать.

Подскажите плиз, куда обратиться.

Спасибо

Посмотрите здесь.

http://www.pcbtech.ru/pages/view_page/146

-

Не знаю как все описать. Это всё наверное к тем, кто делает сложные платы. Хочу получить 16 или 14-слойную МПП толщиной не более 1.6±10%. С контролируемым импедансом 50-100ом в 6 (есть вариант что в семи :crying: ) сигнальных слоях. Вариаты есть. Правда дизайн специфичный. Для моего проекта он не подходит.

Может есть у кого-нибудь приемлемый стек-ап для 16 слойки с толщиной 1.6±10%?

Пока всеёёё плохо. Можно в личку с предложениями.

ps: FAQ !!! После двух ревизий слоев не хватает.

А для каких сигналов и в каких слоях Вам понадобилось 100 ом? Речь про дифф.пару или одиночный сигнал?

В принципе можно посмотреть вот такую структуру - она Вам подошла бы?

-

...Поищите книги по современным печатным платам, это там должно быть обязательно.

Что это за книги такие? Не подскажете название и автора?

-

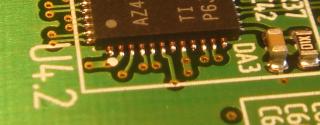

А что это за микросхема? Номинал на фото не видно.

Вы вообще уверены, что торцы выводов именно у этих микросхем подлежат залуживанию и подпайке?

Вы их под микроскопом смотрели? Какое там покрытие снизу и какое на торцах?

-

Вы можете отличить шум в полигоне питания от шума в полигоне земли? Расскажите, пожалуйста, как?

Дело вот в чем. Мы с Вами рассматриваем разную "модель" полигона.

Для Вас это, видимо, некая цельная металлическая штуковина, к которой можно прицепить "землю" осциллографа в любой точке,

и достоверно смотреть "шумы" на другом полигоне. Такой подход может работать для несложных цифровых схем

с не очень высокочастотными сигналами, или если сигналы достаточно короткие (плата маленькая).

Для меня же полигон питания - это некоторая структура, в которой протекает и перекрещивается множество токов.

И ВЧ токи в полигоне питания в общем случае отличаются от ВЧ токов в полигоне земли.

Отлично. Отвечаю: ему деваться все равно некуда. Если ему надо будет попасть в питающий пин источника, то он туда пойдет в любом случае независимо от наличия дросселя. Не так ли?Вы правы. Ток должен будет попасть в питающий пин источника, и это может привести к искажениям сигнала,

если ток нашел какой-то "далекий" или "высокоиндуктивный" путь. Именно об этом я и говорил.

Когда имеем дело с опорным планом - землей, все гораздо проще, и обеспечить низкую индуктивность подключения ИС к земле

гораздо проще, чем к питанию.

Давайте уже закончим эту дискуссию - на самом деле надо было изначально задаться некими конкретными условиями

по параметрам сигнала, частотам, длинам проводников, типам микросхем и т.д. А так это бессмысленно.

Я Вам про Фому, а Вы мне про Ерёму...

Удачи в обеспечении целостности сигнала...

-

"где-то может быть больше шумов в плане питания, чем в земляном полигоне."

Вах!!! И эти люди нам делают платы и проводят семинары? Нет, так жить нельзя...

Хотите увидеть шум - подключайте осциллограф. Только не забудьте, что у него два конца. И у любого прибора, который мерит напряжение тоже.

Читал. Вы тоже не особо стараетесь. Нарисуйте (ладно, напишите словами) полный путь. Откуда он выходит, и где заканчивает свое движение.

Ну вот что, уважаемый vitan.

Или Вы объясняете подробно, что Вам настолько не нравится в моей фразе про шумы в плане питания,

или немедленно прилюдно извиняетесь за переход на личности.

Что касается тока через микрополосок - отвечаю на Ваш вопрос.

На мой дилетантский взгляд, ток по закону Кирхгофа делает замкнутый круг между источником и приемником.

Будем рассматривать только ВЧ составляющую тока.

То, что часть тока отражается раньше на неоднородностях - исключим из рассмотрения для простоты.

Вытекающий из выхода источника и протекающий по микрополоску ток

протечет через вход приемника (видимо, имеющий на этой частоте входное сопротивление около 50 ом),

и через контакты земли и питания выйдет обратно. Тут ему надо попасть на опорный слой, и он попытается это сделать

через переходные отверстия и фильтрующие конденсаторы, если таковые есть.

Затем по опорному плану он течет обратно, стараясь протекать под микрополоском или близко к нему.

Затем он через переходные отверстия и фильтрующие конденсаторы втекает в выводы земли и питания источника.

Куда втекает (или вытекает) больше тока, в выводы земли или питания - зависит от многих факторов,

в том числе от устройства микросхемы источника или приемника, направления протекания тока,

наличия и характеристик фильтрующих конденсаторов поблизости, и так далее.

Если я ответил на Ваш вопрос, то жду ответа на мой.

-

С точки зрения сигнала разницы между полигоном питания и полигоном земли нет. В сигнале присутствуют оба уровня, и уровень питания и земли. Не будем же мы утверждать, что на одной полуволне ток в плэйне есть, а на другой нет?

И фильтровать можно как землю, так и питание, если это даст результат. И опорным может быть и плэйн земли и плэйн питания. Особенно если дроссельных развязок нет, а в цифровых схемах практически никогда не делается развязка каждого чипа по питанию. Поэтому думать можно много, но опорным может быть любой плэйн.

Да я не спорю - конечно же, в принципе обратный ток может течь по полигону питания!

Просто в этом случае может быть несколько больше геморроя с развязками,

что-то можно не учесть, что-то может хуже работать, где-то может оказаться выше

индуктивность соединений, где-то может быть больше шумов в плане питания, чем в земляном полигоне.

Это мои чисто интуитивные сомнения. Если нужны точные доказательства, или пример схемы -

тогда это не ко мне, тут, я думаю, найдутся эксперты получше.

Итак, еще раз суть моего утверждения:

Если схема простая, не очень высокочастотная - нет проблем, используйте VCC как опору.

А вот для насыщенных плат, и более высокочастотных, с чувствительными генераторами

или аналоговыми скоростными цепями - мне кажется, слишком много вещей придется учитывать,

что-то можно пропустить, поэтому безопаснее и проще использовать как опору только слои GND.

А идеально - вообще слой VCC поместить между двумя слоями GND.

А я Вам тоже повторяю: это я спросил у Вас, а не наборот.Кстати, я Вас потом попросил нарисовать без дросселей... Вы тоже не можете? :)

Верно. Именно этого я и добивался.

И очень рад, что так и вышло. Надеюсь, те, кто будут читать топик, пропустят мимо ушей Ваши мысли о разной природе токов, и о плохой идее вести провода над\под питаниями.

Uree

А все-таки, зачем в Вашем примере разработчики (кстати, кто это?) отделили адреса и данные? Что-то тоже смахивает на мракобесие... :)

Итак, уважаемый vitan, вот и выяснился истинный смысл Ваших вопросов. Вы не хотели получить на них ответы.

Вы просто боретесь с мракобесием.

Поэтому и не отвечаете на мои вопросы, и поэтому и отказываетесь, насколько я понимаю, нарисовать путь ВЧ тока на моей схеме.

"Кстати, я Вас потом попросил нарисовать без дросселей... Вы тоже не можете? :)"

Что-то я не понял, зачем это нужно. Без дросселей все, по-моему, очевидно, и я это написал в предыдущих постах.

Ток потечет под микрополоском по опорному плану, затем через переходные отверстия и выводы питания попадет в микросхему.

Хотя тут все будет зависеть от индуктивности соединений.

Или Вы мои ответы не читали?

Итак, мой ход сделан - жду от Вас ответный рисунок с током, протекающим через дроссели, в противном случае буду считать дуэль выигранной :-)

-

Я кроме направления следования никакой разницы не вижу. Я плохо смотрю?

Как может ток течь по-разному?

...

Да? Может, просто Вы этого никогда не видели? Показать Вам схему с дросселями?

Вспомните также, что делают с землей, когда есть аналоговая и цифровая части в схеме.

...

Не так сильно прошит он может быть только при применении несквозных переходных. Давайте разберемся сначала с простой структурой (со сквозными переходными), а уж файн-тюнинг на потом оставим.

...

А из отверстия куда далее? :)

...

Вы не ответили на исходный вопрос, поэтому дальше обсуждать тяжело. Я Вас просил привести схему, в которой был бы сигнальный проводник, два проводника питания, приемник и передатчик. Далее я просил стрелочкой показать, куда потечет ток (желательно полный его круг нарисовать). Вот как только нарисуете, сразу поймете куда он потечет и при установке дросселей тоже.

Уважаемый vitan,

по-моему, наш разговор зашел в тупик.

Я же Вам сказал, что не могу нарисовать, как потечет ток (полный его круг) при установке дросселей по питанию.

Может, Вы сами все-таки нарисуете? Вот Вам заготовка схемы, о которой Вы так просили,

условная, с фильтрующими дросселями и конденсаторами по питанию. Пожалуйста - нарисуйте, даже интересно...

-

Я этого не понимаю, а потому не могу ни согласиться, ни наоборот.

Что это за "природа" и почему она разная? Конструкция одинаковая - оба есть два куска металла. Разница только в том, какой куда подключен (и то - при питании постоянным током). :)

...

О, да. С этим я согласен, это я слышал много раз. Только непонятно, почему?

...

Ну уж нет! Кто первый встал, того и тапки! :) Это я Вас попросил нарисовать.

...

А если в качестве опорного будет нечто другое, то ток, я надеюсь, не потечет по-другому? И вообще, что такое "опорный"? Ну и т.п.

...

Не думаю, что Вы сможете ответить на все эти вопросы, особенно, если Вы сами себя не считаете специалистом по целостности сигналов. Я тоже себя таковым не считаю, но я и не распространяю слухи и домыслы, в которых я не разбираюсь. И Вам не советую.

Отвечаю.

1. Природа земли и питания - разная - потому что токи текут в них по-разному, и способ их применения на плате разный.

В частности, как я уже сказал, полигон земли никогда не отделяют дросселями от потребителей, а полигон питания - часто отделяют.

Кроме того, полигон питания не так сильно прошит переходными отверстиями на внешние слои, как земляной, а значит - надо всегда

задумываться о том, как потекут обратные токи и где именно они выйдут на верхний слой платы.

2. Нарисовать путь обратного тока по полигону питания я не смогу - не представляю себе, как он там потечет для данной схемы,

скорее всего, обходными кривыми путями, потому что дроссель явно мешает протеканию ВЧ токов.

Поэтому я Вас и попросил нарисовать - может, Вы лучше понимаете, где текут токи в полигоне VCC для такой схемы.

А вот по земляному полигону, если он будет опорным - запросто могу нарисовать. Тут и рисовать нечего.

Ток ВЧ потечет прямо под микрополоском,

и выйдет на верхний слой в ближайшем переходном отверстии цепи GND.

3. Если в качестве опорного будет выбрано нечто иное, то и ток потечет по-иному.

Обратный ток ВЧ течет, концентрируясь в полигоне под микрополоском.

Такова физика процесса. Чем больше частота, тем больше концентрация тока под микрополоском.

Но если этот полигон так устроен,

что не позволяет току протечь под микрополоском (например, в полигоне щели) - ток ВЧ ищет обходные пути,

и за счет этого возникают искажения сигнала в микрополоске.

Также искажения сигнала возникают, если из полигона ток не может попасть в микросхему - например,

забыли просверлить переходное отверстие цепи VCC около микросхемы.

В этом случае ток ищет обходной путь через ближайшие переходные отверстия,

или через фильтрующие конденсаторы VCC-GND,

которые могут оказаться довольно далеко от этой точки.

Но если фильтрующие конденсаторы отделены от полигона дросселем,

что часто бывает - я вообще не знаю, где потечет ток, поэтому и спросил Вас.

Так что это не слухи и домыслы, а вполне реальные сомнения,

и я надеюсь, что сумел разъяснить Вам, на чем эти сомнения основаны.

-

Отлично! Я так и думал, что будет подобный ответ.

Тогда пойдем по пунктам.

..............

Ну говорите уж, какие еще есть? А то "мужики-то не знают"... :)

Понимаете, подобные утверждения часто используются вашим братом (технологами) для напускания туману в головы разработчиков с целью сделать стек таким, как вам будет удобно. Это лишнее. Разработчики тоже неплохо знают, куда токи текут, и не надо никого сбивать с толку. Возможно, конкретно Вы ничего такого сейчас и не хотели сказать, но в целом ситуация такая, что в этой области очень много всякого мракобесия. Что меня и зацепило, собственно.

Вы знаете, я вовсе не считаю себя специалистом по обеспечению целостности сигналов. Я просто обратил внимание человека на то,

что планы VCC и GND, вообще говоря, имеют немного разную природу. Вы согласны с этим?

И поэтому в некоторых случаях план VCC использовать в качестве опорного для микрополосков не рекомендуют.

Надеюсь, с этим утверждением Вы тоже согласитесь.

Вы просили показать конкретную схему., где это может оказаться важным. Ну вот, например:

Нарисуйте мне, пожалуйста, на этой схеме - как потечет высокочастотный обратный ток

микрополосковой 50-омной выходной линии (C741 и так далее), если в качестве опорного слоя для нее

выбран полигон питания +5V0_VCO

(подключение к нему показано вверху, через индуктивный фильтр).

-

А можно в этом месте подробнее? Чем это хуже?

Ну, с опорным планом VCC больше может быть заморочек, чем с землей. Все-таки природа слоев GND и VCC немножко разная.

Например - часто выводы питания ИС отделяют от полигона VCC с помощью небольшого ферритового колечка.

Не помешает ли это протеканию высокочастотных обратных токов микрополоска через полигон VCC?

Еще одно отличие - обычно заливку свободных пространств во внешних слоях и

множественную перфорацию переходными отверстиями по всей плате

делают именно для GND. Поэтому он "солиднее", чем VCC.

Ну и еще есть ряд отличий. Но это может быть важно только для очень критических сигналов.

Так-то, конечно, ничего страшного в применении опорного VCC нет,

если сигналы не очень высокочастотные и чувствительные к помехам.

Меандры в пикаде

в Работаем с трассировкой

Опубликовано · Пожаловаться

Ну, наверное, все-таки не емкостная, а индуктивная (электромагнитная).

Altium, Orcad, Zuken, Mentor, Cadence Allegro.

От P-CAD пора отказываться, он вас тормозит.