-

Постов

1 220 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные PCBtech

-

-

Подскажите, пожалуйста, Вы возвращаете неиспользуемый запас компонентов?

Да, остатки компонентов возвращаем.

-

Здравствуйте!

Планируем изготовить в PCB technology два опытных образца печатных плат с дальнейшим монтажем на их же производством. Комплектацию уже закупили сами (она достаточно дорогостоящая), однако некоторые микросхемы не в заводской упаковке, к тому же некоторые микросхемы в BGA корпусах так же не в вакуумных упаковках. Вопрос возможен ли монтаж таких компонентов, так как перезакупка достаточно дорогое удовольствие...

Добрый день.

Плохо, что BGA не в вакуумной упаковке.

Мы их отсушим, конечно, но есть риск непропая.

Если другие компоненты не в заводских упаковках, надо смотреть, не повреждены ли ножки.

В целом, на опытные образцы это не страшно, запаяем, а на серию надо все же более требовательно относиться к закупке ЭРИ.

-

Ну вот в версию с каким-то клеем я верю больше, чем в скотч. Скотч, я так понимаю, должен быть двухсторонним. Но есть вопрос - как потом удалить остатки скотча и с платы, и с приспособы? И что будет со скотчем в печи?

Или уже есть готовые парт-намберы клея и негорючего скотча?

У нас на монтаже используют для этого обычный термоскотч.

-

Эм... Пример такой платы есть? Как такое вообще можно изготовить...

Примеры есть, но в основном в Cadence Allegro.

Вам нужен именно пример в Expedition? Можем поискать, скажите e-mail, куда отправить.

Обратите внимание - у вас разное количество слоев в двух жестких частях, так делать не рекомендуется.

В крайнем случае сделайте гибкий шлейф, на конце которого приклеен снизу упрочняющий элемент.

Т.е. жесткая часть 14 слоев будет только одна, а вторая часть будет не жесткая, а гибкая с упрочнением.

Надеюсь, понятно объяснил...

С уважением,

Александр Акулин

-

Почему бы в этом случае не открыть все площадки одним окном? Вроде ГОСТы и IPC не запрещают так делать.

Будут сложности с пайкой. Залипы.

Маска все-таки помогает тому, чтобы припой скатывался на площадку.

А голый стеклотекстолит очень липкий, припой к нему пристает.

У некоторых производителей ПП, особенно отечественных,

даже процесс лужения может быть проблемным, если нет полосок маски между зазорами 0.2мм. Будут многочисленные залипы.

-

Такие зазоры Резонит держит. Странно. Думаю, дело было как раз в глухих/скрытых отверстиях. Их они и вправду вроде бы не делают.

Так ведь это 0,2 мм между площадками, а не между проводниками.

Там еще маску надо положить, как минимум шириной 0,1 мм, получаются отступы маски от площадок

по 50 мкм. Это далеко не каждый даже зарубежный завод

может делать.

-

нам для изготовления плат рекомендуют Рязанский завод, кто-нибудь у них платы заказывал?

В Рязани 2 основных завода по печатным платам - Государственный Рязанский Приборный Завод и Красное Знамя.

ГРПЗ покруче и по оборудованию, и по возможностям. Пожалуй, на данный момент это самый высокотехнологичный в России завод по платам. Но делают долго.

-

При серийном производстве на СМД линии, платы объединяют в заготовку, обычно этим занимается на этапе подготовки к производству

Существуют ли стандарты IPC или аналог по которым должен руководствоваться изготовитель при мультиплицировании плат в панель ?

от заказчика достаточно ли указать раскладку на панели , наличие тех полей и метод разделения плат (фрезеровка или скрайб ) ? или что то им еще нужно

Это сильно зависит от особенностей оборудования для SMD-монтажа. Поэтому правильнее всего - попросить рекомендации по панели у вашего монтажного производства.

Даже размер панели и количество точек пайки может иметь значение, отражаться на стоимости монтажа.

Если что, напишите мне на [email protected] - я скину наши типовые рекомендации, их можно взять за основу.

-

Просьба ответить по пунктам:

1. Выполняете ли вы покрытие ENIPIG?

2. Если плата с BGA(скажем - 1000 выводов), разнообразными QFN, можно ли использовать ImAg – иммерсионное серебро?

3. Если плата с BGA(скажем - 1000 выводов), разнообразными QFN и разъемами PRESS-FIT, можно ли использовать ImAg – иммерсионное серебро? Как там с монтажом таких плат?

4. Что лучше - ENIPIG или ImAg и почему? Сильно будет по цене отличаться, хотя бы на каких-то примерах и примерно?

Добрый день.

1. Покрытие Золото-палладий-никель делаем.

Плюсы:

- гарантированное отсутствие дефектов типа Black pad после пайки BGA

- возможность приварки бескорпусных элементов

Минусы:

- дольше на неделю, чем имм.золото

2. Покрытие имм.серебро можно использовать, в том числе и для BGA, QFN, press-fit.

3. Платы с имм.серебром поставляем и успешно монтируем,

дефектов под BGA и QFN не наблюдается.

4. Я бы рекомендовал золото-палладий-никель.

Но имм.серебро - неплохая альтернатива.

По цене - зависит от партии, пришлите проект, оценим.

-

HFSS,

Можно ли в Роджерсе сделать металлизированное отверстие в виде параллелепипеда размером, например 1x0.1x0.813мм, где 0.813 - толщина подложки. Ну то есть узкую металлизированную щель... ?

Можно примерно 1x0.2мм. А 1х0.1, думаю, нереально.

-

Всем хороших выходных!

Возник небольшой вопрос. Была плата с диф. парами. Потребовалось её немного переработать. Добавил слоёв, как следствие - изменились параметры стека. Пересчитал толщину и зазор для диф. пар. Поменял параметры соответствующих ECS в Electrical->Differential Pair. Обновил ошибки. В итоге трассы подсвечиваются на ошибку неправильного зазора. Когда это устраняю - все ошибки уходят. А нужно, чтобы еще и неправильная ширина подсвечивалась.

Где и что я сделал не правильно? Что нужно сделать, чтобы при изменении параметров диф. пары показывался не только кривой зазор, но и кривая ширина трасс?

Может, поставить параметр Max Uncoupled Length или, скорее, Max Line Width в определении дифф.пары?

-

Аналог. Диапазон частот 1-3ГГц. как раз согласование и интересует. проводник идет от входного разъема к аттенюатору. расположить их на одном слое возможным не представляется, а согласование по входу хочется получить максимально хорошее. Еще вопрос - в чем можно промоделировать?

Давайте мы промоделируем вашу структуру, может быть, удастся найти приемлемую комбинацию параметров, минимизировать скачок импеданса.

Пришлите структуру слоев на [email protected]

я передам нашим специалистам в КБ.

-

Есть ли результат?:)

Да, все примеры, которые присылались, успешно конвертированы в формат Cadence Allegro 16.6 с возможностью дальнейшей настройки констрейнов и трассировки уже с помощью продвинутых средств Cadence.

Импортируются компоненты, цепи, проводники, переходные отверстия, полигоны - в общем, все, что нужно для плавного перехода с PCAD на Allegro.

Библиотеки посадочных мест можно в дальнейшем экспортировать прямо из полученного файла Allegro.

Были обнаружены некоторые нюансы конвертации, пришлось повозиться, чтобы найти решение.

-

Посоветуйте как уменьшить вырезы на плате, которую я развёл ? Что-то никак не дойдёт до меня. Препод говорит, что ещё можно уменьшить.

У Вас некорректный Outline - в нем должен быть контур платы, в у Вас в нем два странных прямоугольника непонятного назначения.

Также непогашены некоторые ошибки DRC.

Цепь с названием "0" - это нетипично, принято называть GND, VSS или хотя бы 0V.

Широкие проводники 16 mil при подводе к площадкам микросхемы лучше бы заузить хотя бы до 12 или 8 mil.

Слой паяльной маски Soldermask Top/Bottom у Вас вообще пустой, а там должны быть площадки, открытые от маски.

Слой Assembly Top/Bottom тоже пустой, а там должен быть чертеж размещения компонентов с REFDES.

Слой Silkscreen Top/Bottom содержит только прямоугольники вокруг компонентов. Хорошо бы там поставить REFDES,

разместить рядом с компонентами. А прямоугольникам дать ширину линии 0.2 мм, т.к. сейчас она нулевая.

Дальше - не очень понятно, почему у Вас 7я ножка контроллера, VCAP, висит в воздухе.

2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP

pin, which is used to stabilize the internal voltage regulator

output. The VCAP pin must not be connected to

VDD, and must have a CEFC capacitor, with at least a

6V rating, connected to ground. The type can be

ceramic or tantalum. Refer to Section 29.0 “Electrical

Characteristics” for additional information on CEFC

specifications.

Вообще проверьте схему, наверняка еще куча ошибок.

Короче, еще работать работать и над схемой, и над платой.

Удачи.

-

Вы хотите получить что-то типа этого?

Привет всем!Уважаемые коллеги, пытаюсь освоить Cadence Allegro 16.6 , до этого много лет работал в Альтиуме. Поставил последнее обновление 16.6-S028,

1.Как задать контур печатной платы?

2. Можно ли задать его так, чтобы это выглядело как отдельная "черная" плата на сером фоне со всеми вырезами и выфрезеровками?

(Кто работал в Альтиуме тот поймет) . То же касается 3D.

3. Пока что все примеры что есть у меня- это ограниченная контуром черная плата на черном фоне, без границ.

Покачто трудности с освоением интерфейса. Альтиум Дизайнер отличается от Cadence Allegro значительно.

Спасибо.

-

Ага. В районе того. Но "Лёд тронулся, господа присяжные заседатели!"))

Что не может не радовать! :1111493779:

Самое приятное, что отечественные пассивные компоненты наконец-то начали поставлять в лентах для автоматического монтажа.

А то военные заказчики с пакетиками рассыпухи уже замучали...

Интересно, каково качество этих лент?...

-

Маркировку выводов резисторов, конденсаторов и подобных элементов лучше учитывать при рисовании принципиальной схемы. Выводы, подключенные, например к GND, делать одинаково, а не как придется. Влияет на количество работы по приведению в порядок маркировки на плате (ориентация и положение) и подготовке документации.

В моделировании многих схем в PSpice резистор - полярный элемент, не говоря уже о конденсаторе и индуктивности, для которых задаются начальные условия напряжений и токов. Возможно, маркировка выводов у "товарищей" ведет свое начало от моделирования или из-за ручного контроля списков цепей для небольших схем.

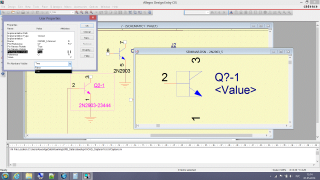

Чтобы сделать пины транзистора видимыми:

- выбрать компонент

- правой кнопкой - Edit Part

- Options - Part Properties

- Pin Numbers Visible - True

Закрыть редактор компонента

Update All? - подтверждаете либо только для этого транзистора, либо для всех на схеме.

Такой метод не спасает ситуацию?

Я думаю, что по-отдельности включать каждый пин, как вы делаете - метод менее удобный.

-

Написал, но никакого ответа не получил до сих пор :(

Должны в понедельник прислать.

Наталью отвлекли на другую работу, просьба немного потерпеть.

-

А какой нибудь материал бесплатно получить возможно?

Можно получить PDF со слайдами семинара.

Пишите запрос Наталье Ибрагимовой, она занималась организацией семинара:

-

Кто знает: как конвертировать пикадовские библиотеки в библиотеки OrCAD ?

По поводу библиотек посадочных мест:

Можете прислать мне файл PCB (pcad2006) с расставленными компонентами, я в тестовом режиме оттранслирую и пришлю Вам файл Cadence BRD, с этими же компонентами. Потом в Cadence делаете File-Export-Library.

Как раз тестируем наш новый конвертер PCB-BRD-PCB.

Единственное - возможно, потом файлы Device надо будет настраивать под ваши задачи (свапирование и эквивалентность выводов, и так далее).

А если речь про УГО - есть встроенный конвертер в OrCAD.

Впрочем, если он не годится, у нас есть другие решения - обращайтесь.

-

Всем добрый вечер!

Делаю плату питания на основе Simple Switcher от TI.

У меня три десятиамперных источника. Предполагаемая нагрузка - в районе 5А на каждый.

У платы будет четыре слоя (чтобы лучше рассеивать тепло).

Сильно ограничен в габаритах, поэтому придется ставить преобразователи очень близко друг к другу.

Из-за используемых микросхем защиты не могу сделать медь толще 35мкм.

...

Можно часть проводников в том же слое делать с более толстой медью, например, 100 мкм.

Есть такая технология. Нужен еще один гербер-слой, в котором указаны только эти проводники.

-

Уважаемые разработчики!

Последний шанс зарегистрироваться на семинар. Осталось 10 мест.

Во вторник 22 апреля 2014 г. - повторный семинар компании PCB technology - «Проектирование печатных плат с BGA и микро-BGA. Технологические нюансы. Особенности трассировки скоростных плат (DDR, PCIe, HDMI, Ethernet)».

В программе:

• Особенности подготовки проектов МПП к производству

• Посадочные места для микросхем QFN, BGA и микро-BGA

• Грамотное размещение и трассировка корпусов BGA

• Прокладка дифференциальных пар, выравнивание длин и фаз дифференциальной пары

• Трассировка микросхем памяти DDR2, DDR3, DDR4

• Via-In-Pad (технология переходных отверстий в площадке SMD-компонента)

• MicroVia (лазерные микропереходные отверстия) и платы высокой плотности (HDI PCB)

• Теплоотвод. Медные теплоотводящие слои в печатной плате. Технология "медная вставка".

• Структуры многослойных плат, комбинированные платы из разных диэлектриков, СВЧ-диэлектрики Rogers и др.

• Контроль волнового сопротивления в печатной плате. Точный расчет импеданса.

• Backdrilling (обратное высверливание) в печатной плате. Устранение лишних кусков переходных отверстий (stub).

• Новинки в сфере технологий и материалов для МПП

• Монтаж плат с BGA – нюансы и проблемы

Докладчик: Александр Акулин, технический директор PCBtechnology.

Семинар пройдет в Москве 22 апреля 2014 г в конференц-зале №7 гостиничного комплекса «Измайлово-Альфа»

по адресу: Измайловское Шоссе, д.71, корпус А (м. Партизанская, 2 мин. пешком)

Начало семинара в 10.00 (окончание 18:00)

Стоимость участия: 3 000 руб. Для 3-х и более человек – скидка 30%.

По всем вопросам вы можете обращаться по тел.: 8 (499) 558-02-54

Зарегистрироваться на семинар >

http://www.pcbtech.ru/pages/view_anounce/28

-

Мне нужно средство погасить при необходимости часть изображения, как в любом редакторе плат или хоть в фотошопе.

В Cadence Allegro (редактор схем Capture) есть такая возможность:

Setting print options for objects on the schematic page.

You can specify various options for determining how specific objects on the schematic page are printed.

To define if an object is printed or plotted

1 From the Options menu, point to Preferences, then choose the Colors/Print tab.

2 Select the check box located beside the color block for the object that you want to be able to print or plot. Clear the

check box if the object is not to be printed or plotted.

Note: Objects are always displayed on your screen, regardless of the setting of their check boxes.

Еще, как вариант, можно назначать "свойства" определенным объектам, например, цвет.

И, используя скрипты, в нужный момент гасить или зажигать требуемые объекты для печати,

-

Уважаемые заказчики

Приглашаем посетить стенд нашей дочерней компании, ПСБ СОФТ, на ЭкспоЭлектронике с 15 по 17 апреля.

Номер стенда 3F11, напротив Департамента РЭП.

Заходите, будем рады вас видеть и обсудить какие-то технические нюансы ваших новых проектов МПП.

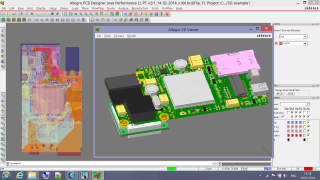

Мы будем демонстрировать на стенде новые продвинутые возможности САПР печатных плат Cadence Allegro,

а также наш конвертер проектов и библиотек из PCAD200x в Cadence Allegro.

перевод из PCAD в Allegro

в Cadence

Опубликовано · Пожаловаться

У нас есть свой конвертер PCB из PCAD в Allegro.

Пришлите пару типовых файлов, мы переведем бесплатно, посмотрите качество.