-

Постов

270 -

Зарегистрирован

-

Посещение

Весь контент AnatolySh

-

-

А чем вам родина не угодила? Закрома хороши, но содержат далеко не всё. Сам недавно просил в дружественной группе в телеге мне с родины примеры вытащить. Там же научили, как там аккаунт даже сейчас получить. Могу здесь озвучить, могу в личке. Если нужно, конечно.

-

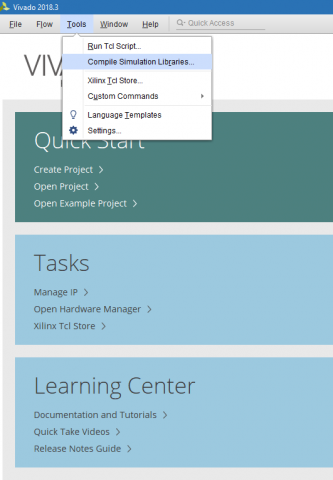

Архив недоступен, да и уверены ли вы, что ваши библиотеки подойдут к тому, что есть у других? Уж только из-за этого, как понимаете, переставлять софт под вас. Думайте в сторону универсальности. Например у меня - ISE 14.7 и Vivado 2018.3 c QuestaSim 2020.1

-

Пожалуйста! Не смог не сдержаться (по-моему, уже здесь постил, но мем очень знатный, как по мне) Это уж давайте сами попробуйте, ибо мне пока не надо. Да и чувствуется мне, что и там и там - те же яйца, вид сбоку. Понимаете, о чём я?

-

Попробуйте CompileQuartusLibraries4Mentor.zip

-

Так в upload ftp выложите и ссылку дайте Всего лишь. Кстати, а чём другие версии не устраивают? Скажем Vivado 2018.3 и QuestaSim 2020.1?

-

Как понимал *.opt и *.tcl, что создаёт по умолчанию Synplify Premier with Design Planner - суть одно и тоже. У меня вместо этого набор bat, первый из которых вызывает %Xilinx%\bin\nt64\ngdbuild.exe И вот при вызове его возникают сообщения вида Checking expanded design ... ERROR:NgdBuild:604 - logical block 'u_rgb2ycrcb_v1_0' with type 'rgb2ycrcb_v1_0' could not be resolved. A pin name misspelling can cause this, a missing edif or ngc file, case mismatch between the block name and the edif or ngc file name, or the misspelling of a type name. Symbol 'rgb2ycrcb_v1_0' is not supported in target 'spartan3'. Объявление в коде module rgb2ycrcb_v1_0 ( sclr, ce, v_sync_out, pix_en_in, h_sync_out, clk, pix_en_out, h_sync_in, v_sync_in, cb, cr, b, g, r, y )/* synthesis syn_black_box syn_noprune=1 */; input sclr; input ce; output v_sync_out; input pix_en_in; output h_sync_out; input clk; output pix_en_out; input h_sync_in; input v_sync_in; output [7 : 0] cb; output [7 : 0] cr; input [7 : 0] b; input [7 : 0] g; input [7 : 0] r; output [7 : 0] y; endmodule `endif И инстанс rgb2ycrcb_v1_0 u_rgb2ycrcb_v1_0 ( .sclr(1'b0), .ce(1'b1), .v_sync_out(v_sync_out), .pix_en_in(pix_en), .h_sync_out(h_sync_out), .clk(pix_clk_c), .pix_en_out(pix_en_out), .h_sync_in(hsync_i), .v_sync_in(vsync_i), .b(blu), .g(grn), .r(red), .y(y), .cb(cb), .cr(cr) )/* synthesis syn_noprune = 1 */; Как Sinplify указать на rgb2ycrcb_v1_0.ngc ?

-

Огромное спасибо за то, что с таким лагом удалось прийти сюда и обрести надежду на прохождение тем же путём. Вопрос: эти файлы уже есть в моей установке 2009.06SP1 -бит в бит. Это не должно смущать? Дистрибутив брал из закромов.

-

Это как? Reuse не в почёте? Про каждый тестбенч для каждого dut я понимаю, но про скрипты прошу пояснить. Вы писали про доступ к конкретному софту. Представьте, я сам в такой работаю. Однако, я, например, работаю не только дома, и все прошлые выходные проработал на ту же фирму и дома и ещё с одной дислокации. Причём эта сверхурочная работа мне никак не оплачивается. Не смог не удержаться Вы только этот способ знаете? Я имел глупость вам ещё по кр. мере на один открыть глаза, но, раз у вас всё так строго и не только с лицензионностью, то ..... Кстати, я Вам в личку, всё-таки, напишу, потому что считаю, что наш диалог сможет принести нам обоим пользу. Мне-то он уже полезен, ибо я, как Олег Янковский, улыбаюсь ))) А Вам спасибо за то, что вызвали эту, пусть и глупую, улыбку, и тем подняли настроение ))

-

И что вы в этой схеме интересного для себя нашли? Сначала все файлы в архиве изучите, что за чем, и только тогда идите дальше. Иначе занятие это будет пустой тратой времени (с) кто сказал?

-

-

Поясните то, что намешано внутри.

-

Все такими были. Выложите ваш проект.

-

Дух исследователя. Есть и к Questa. Если вам нужен - напишите мне в личку.

-

Раз такой вопрос, наверное, и ответ понятен? Именно мнение таких же товарищей я и привёл. Это мне тоже известно Давайте говорить о вкусе кофе с тем, кто его пил (с) PS. Спасибо в любом случае

-

Вы можете минимизировать Ваш проект настолько, чтобы Ваш путь можно было бы повторить, например, мне? Ибо я занимаюсь примерно тем же самым ?

-

Xilinx ISim TCL ISE -> Vivado

AnatolySh опубликовал тема в Среды разработки - обсуждаем САПРы

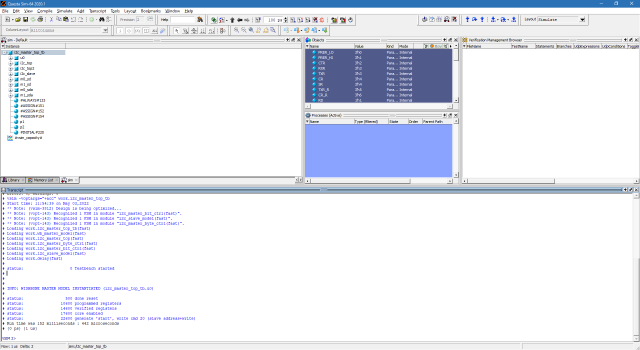

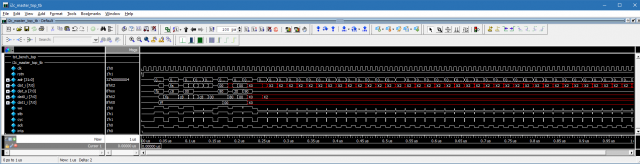

Всем добра. Всю (ну почти) свою сознательную жизнь моделирую на Mentor-е (ModelSim, Questa), т.к. и RTL кодирование было на Altera (Intel). Пришла пора пересаживаться на Xilinx (Spartan-6 ISE 14.7), где уже не один товарищ сказал, что родного ISim-а за глаза хватает. Даже если мне в глаза говорят, то имею привычку проверять, что и сделал на примере простейшего модуля (всё в скрепке). И первое, с чем столкнулся - никак не могу ISim после прорисовки временной диаграммы в GUI масштабировать её средствами TCL так, как может Mentor (ну для начала развернуть на весь экран суть покатать мне сразу всё). Мелочь, но первый звоночек для меня. Но тут закралась мысль: а, может ISim от Vivado это умеет? Просьба показать, просто ли простым переносом мне перенести TCL от ISE на оный от Vivado и получу ли я там то, что ищу (и прочие разные вкусности)? settings.zip -

-

-

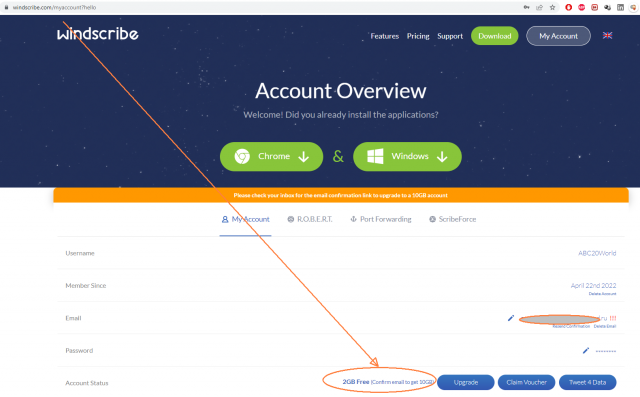

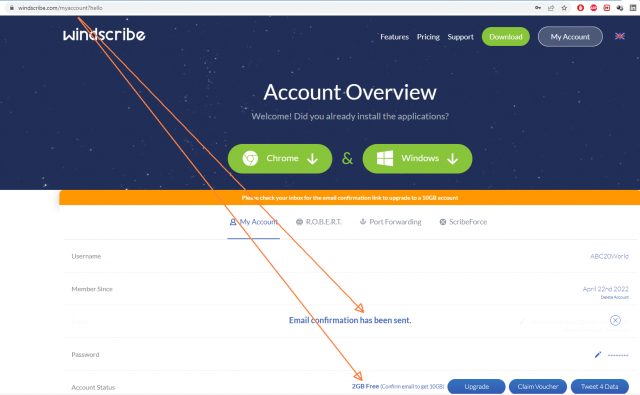

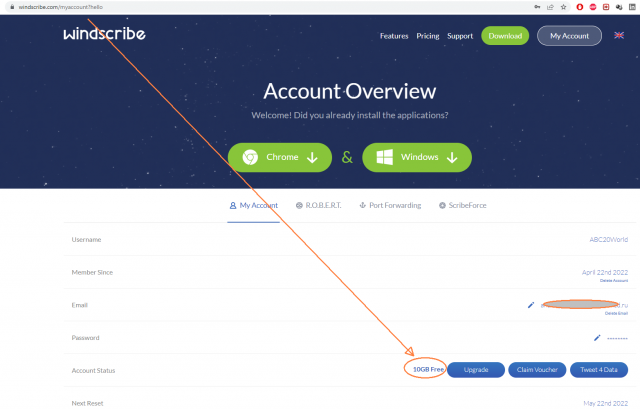

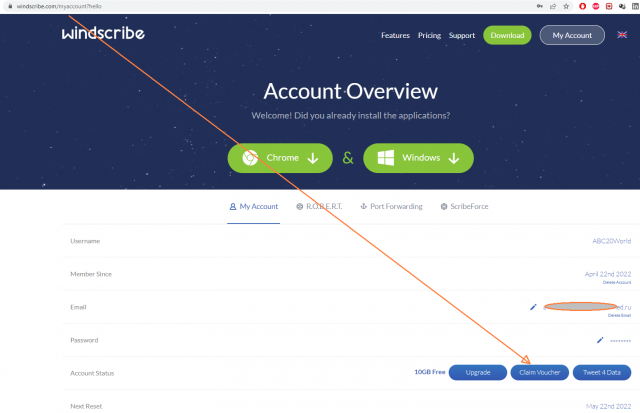

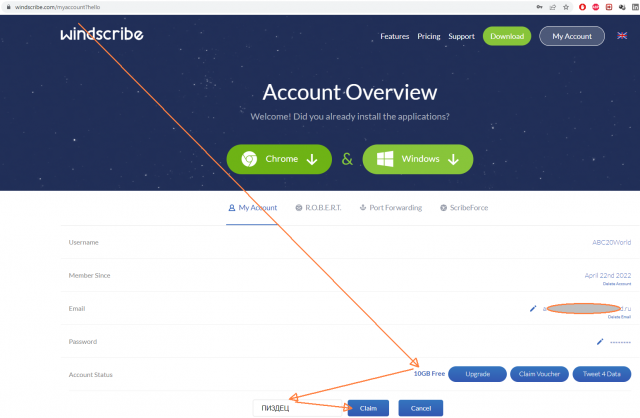

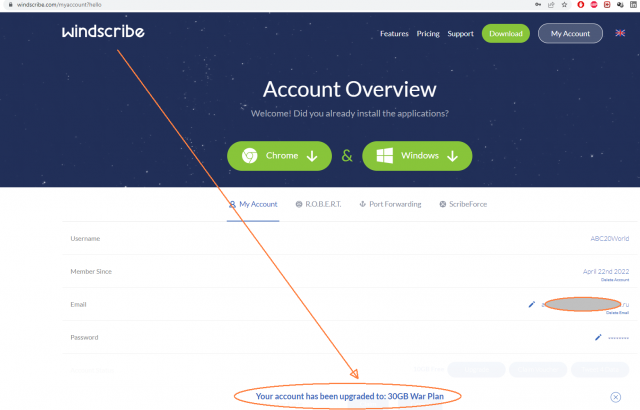

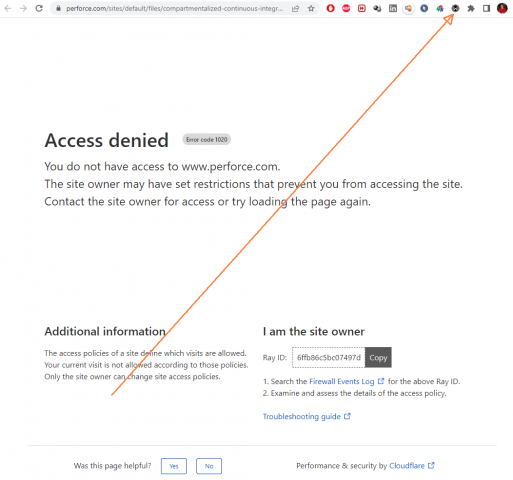

Спасибо огромное! Без включённого VPN С включённым Сам найденный Вами документ в скрепке. Спасибо! compartmentalized-continuous-integration-wp.pdf

-

Intel (Altera) Quartus - что такое SJ?

AnatolySh опубликовал тема в Среды разработки - обсуждаем САПРы

-

Понял. Спасибо.

-

Всем добра! Большую часть своей сознательной жизни проведя на Mentor Graphic's QuestaSim, захотелось сравнить оное c Xilinx's ISim, поставив и тот и другой инструмент в максимально одинаковые условия, т.е. стартуя в режиме командной строки. Если к первой части марлезонского балета вопросов никаких не было (ну, или они были сняты за многие лета изучения матчасти), то первые опыты работы с новым видом оружия ставит вопросы, на которые ответы не находятся ни с помощью штудирования интернета, включая, конечно, родной сайт и все tutorials и knowledge base с него, так и коллег по цеху, проработавших с этим ПО уже вечность (по ср. с моим опытом длительностью менее месяца). Это, как говорится, была преамбула. Амбула в следующем: ... не буду снова загружать скрипты, ибо из никто не то что не смотрит, их не скачивают, да и надобности нет, а спрошу так: каким образом, стартуя сформированный fuse ехе-шник, подставляя ему в качестве аргументов и tcl и wcfg можно отобразить временную диаграмму так, как мне нужно? Например сразу всю, либо же от одного временного интервала в пределах времени моделирования до другого? Ещё раз: Mentor это умеет легко, а, вот, ISim?

-

Откуда такие цифры? Собственноручно скачанное и залитое в закрома Quartus-pro-22.1.0.174-windows-complete.tar 82 316 554 240 05.04.2022 22:39 -660

-

Прошу почтенную публику великодушно простить за непреднамеренное введение в заблуждение: показанный на моём фото выше бластер - разработка мною глубоко уважаемого StewartLittle, о котором он пишет следующее (цитата, прямая речь): "Джамперами он может конфигурироваться или в Bytablaster II, или в Bytablaster MV. Только надо иметь в виду - любой LPT'шный Byteblaster не будет работать под Win x64, т.к. под эти оси нет соответствующих драйверов. Ну и, соответственно, с номерами версий Quartus нужно внимательнее быть."