-

Постов

270 -

Зарегистрирован

-

Посещение

Весь контент AnatolySh

-

Смотря с каким ВЗПП. Где-то отдельный сервер надо ставить, а где-то набор утилиток, который ещё и напильником облагораживать, чтобы в удобоваримый roadmap привести. Правда, это не к ВЗПП вопросы а к КТЦ Электроники, но хрен редьки...

-

Где можно достать одну (пару) штуку hs8203bn8?

AnatolySh опубликовал тема в Микросхемы

Всем добра! Вопрос в теме, собственно. -

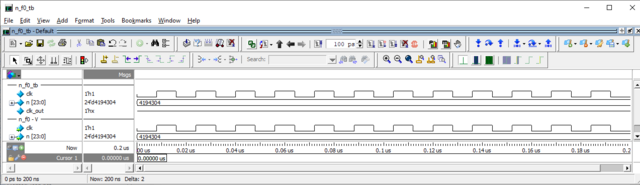

Да, спасибо: reg [23 : 0] count_v = 0; reg c_out_v = 0; привело в соответствие. Откуда тогда я мог помнить о необходимости сброса всего и вся в начале работы?

-

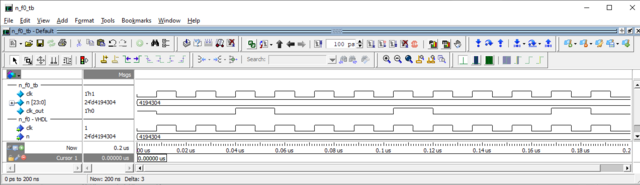

Всем добра. Уверен, что давно уже обсуждено много раз, но снова прошу меня направить в нужное русло. Вспоминаю, что при моделировании (и, возможно, не только) необходимо принудительно устанавливать все триггеры проекта в заранее определённое состояние. Берём модуль на VHDL library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity n_f0 is Port ( clk : in std_logic; n : in integer range 0 to 2 ** 24 - 1; clk_out : out std_logic ); end n_f0; architecture Behavioral of n_f0 is signal count : unsigned (23 downto 0) := (others => '0'); signal c_out : std_logic := '0'; begin report_proc: process begin report "Invoked n_f0.vhd"; wait; end process report_proc; clk_proc : process (clk) begin if rising_edge(clk) then count <= count + to_unsigned(n,24); c_out <= count(23); clk_out <= '1' when count(23) = '1' and c_out = '0' else '0'; end if; end process clk_proc; end Behavioral; и его реинкарнацию на Verilog module n_f0 ( input clk, // input clk input [23 : 0] n, // divider output reg clk_out // output ); initial $display("Invoked n_f0.v"); reg [23 : 0] count_v; reg c_out_v; wire count_v_msb; assign count_v_msb = count_v [23]; always @ ( posedge clk ) begin count_v <= count_v + n; c_out_v <= count_v_msb; clk_out <= count_v_msb && !c_out_v; end endmodule С testnbench module n_f0_tb; logic clk; logic [23 : 0] n; wire clk_out; n_f0 n_f0_inst ( .clk ( clk ), .n ( n ), .clk_out ( clk_out ) ); initial $display("Invoked n_f0_tb.sv"); initial n = 2 ** 22; initial begin clk = 1'b0; forever # 8ns clk = ~clk; // 125MHz end endmodule : n_f0_tb Моделирование VHDL варианта даёт Т.е. всё работает (clk_out), а, вот, verilog вариант молчит. Уверен на 100%, что дело в сбросе, но почему, скажите, VHDL вариант катит? Установки симулятора, стандарт или что-то иное?

-

Гляньте в скрепке - м.б. что найдёте полезное? DFFwE.zip

-

Согласен. Не моё. Согласен. Моё. Спасибо. Исправлюсь. Руки (пока) прошу не рубить.

-

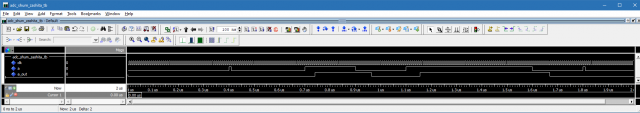

И снова здравствуйте. Пока родил вот что: package adc_shum_zashita_pkg; timeunit 100ps; timeprecision 100ps; parameter CLK_PRD = 8ns; // 125MHz parameter RST_SET_TIME = 20ns; parameter RST_DUR_TIME = 10ns; parameter CNT_PULSE_DIM = 8; typedef logic [CNT_PULSE_DIM - 1 : 0] cnt_pulse_t; parameter MAX_DELAY = 20; parameter PAUSE_DELAY = 20; endpackage : adc_shum_zashita_pkg и import adc_shum_zashita_pkg::*; module adc_shum_zashita_tb; logic clk; logic rst; logic a; logic a_out; initial $display("Started adc_shum_zashita_tb.sv"); adc_shum_zashita adc_shum_zashita_inst (.*); initial begin clk = 1'b0; forever # ( CLK_PRD / 2 ) clk = ~clk; end cnt_pulse_t i; initial begin @(posedge clk); for (i = 0; i < MAX_DELAY; i++) begin a = 1'b1; repeat(i) @(posedge clk); a = 1'b0; repeat(PAUSE_DELAY) @(posedge clk); end end initial begin rst = 0; #RST_SET_TIME rst = 1; #RST_DUR_TIME rst = 0; end endmodule : adc_shum_zashita_tb думаю в сторону рандомизации, хотя не уверен, что она здесь нужна

-

Всем спасибо, всё получилось. Sinplify оседлан!

-

Какие параметры поиска задать, чтобы получить наиболее релевантные результаты? Ну или готов прошерстить форум (этот раздел, или искать и в трёх оставшихся "дружественных"?), дабы покончить, наконец-то с наследием прошлого, не достойного звания советского офицера. Где считаю нужным, писю, и уже давно Всё, я уже обильно посыпал голову пеплом и готов быть посланным в нужном направлении ))) Это - выход SPI ADC AD7680, управляемого (CS и CLK) от ПЛИС через LVDS TX -> LVDS RX -> OptoCouple ADuM640X, данные с которого по той же цепочке улетают обратно. Кто и как решил, что эти данные надо фильтровать и почему именно такую границу заложил - предстоит либо выяснить либо забить на это дело.

-

Спасибо. Форум читаю нерегулярно, особенно сейчас, когда как и у вас работы выросло вдвое, но теперь сориентируюсь на переход к параметрам. Пакеты, как понимаю, это про VHDL?

-

Прошу сказать, что не так с макросами и пнуть, как понимаю, в сторону параметров?

-

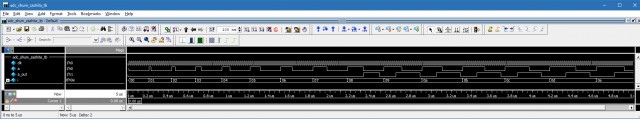

Спасибо огромное, сделал так: `timescale 1ns / 1ns `define T1ns 1 // with respect to timeunit `define T1us ( 1000 * `T1ns ) `define T1ms ( 1000 * `T1us ) `define CLK_PRD ( 20 * `T1ns ) `define CNT_PULSE_DIM 8 `define CNT_PULSE_RNG [`CNT_PULSE_DIM - 1 : 0] `define MAX_DELAY `CNT_PULSE_DIM'd20 `define PAUSE_DELAY 10 module adc_shum_zashita_tb; logic clk; logic a; logic a_out; adc_shum_zashita adc_shum_zashita_inst ( .clk ( clk ), .a ( a ), .a_out ( a_out ) ); logic `CNT_PULSE_RNG cnt_pulse; initial begin clk = 1'b0; forever # ( `CLK_PRD / 2 ) clk = ~clk; end logic `CNT_PULSE_RNG i; initial begin @(posedge clk); for (i = 0; i < `MAX_DELAY; i++) begin a = 1'b1; repeat(i) @(posedge clk); a = 1'b0; repeat(`PAUSE_DELAY) @(posedge clk); end end initial begin forever @(negedge a_out) begin cnt_pulse = 0; $display("Pulse size (decimal) = %0d", i); end end initial forever @(posedge clk) cnt_pulse = a_out ? cnt_pulse + 1'b1 : cnt_pulse; endmodule : adc_shum_zashita_tb Что выдало в консоль # Pulse size (decimal) = x # Pulse size (decimal) = 8 # Pulse size (decimal) = 9 # Pulse size (decimal) = 10 # Pulse size (decimal) = 11 # Pulse size (decimal) = 12 # Pulse size (decimal) = 13 И отобразило Более чем доволен. Прошу простить, не упомянул в ТЗ частоту. Она там была, конечно что..

-

Всем добра! Есть модуль, пропускающий через себя импульсы с длительностью больше определённой. Задача: написать testbench, подающий на вход модуля последовательно импульсы с нарастающей от единичной длительностью и проверяющий появление оных на выходе, дабы понять границу. Какие варианты существуют (SV tasks, SVA)? В общем, ткните носом, плиз.

-

Очень сжатый вопрос. Если расширите, для чего это вам, м.б. ответ будет полнее и точнее? Загрузить куда?

-

VHDL to Verilog

AnatolySh ответил AnatolySh тема в Языки проектирования на ПЛИС (FPGA)

Если звёзды зажигают ... дальше понятно? Мне - да. -

VHDL to Verilog

AnatolySh ответил AnatolySh тема в Языки проектирования на ПЛИС (FPGA)

Спасибо! А это все CONFRML_12.10.420/ CONFRML_13.10.100/ CONFRML_14.10.140_lnx86_Hotfix/ CONFRML10.10.100/ CONFRML11.10.300/ CONFRML12.10.100/ CONFRML12.10.160/ CONFRML15.20.100_Base/ CONFRML17.10.100/ CONFRML19.20.100/ чем отличаются? Брать последнюю версию, и не думать? Тот же вопрос про ../EDA/_Synopsys_/fm_****/ Formality Если старое, то какой интерес может представлять? -

VHDL to Verilog

AnatolySh ответил AnatolySh тема в Языки проектирования на ПЛИС (FPGA)

Не нашёл ни того, ни другого. Прошу ткнуть носом. -

VHDL to Verilog

AnatolySh ответил AnatolySh тема в Языки проектирования на ПЛИС (FPGA)

Спасибо, гляну. Как раз комп с Убунтой простаивает. --------------------------------- Попробовал тут утилиту vhdl2verilog из пакета SynaptiCAD (последняя на текущий момент версия выложена собственноручно в вышеупомянутые закрома), который с разной степенью настойчивости дёргаю за усы. Вот, что он выдал при преобразовании первого листинга: Вывод в консоль: // VHDL2verilog version 20.51 // Copyright (c) SynaptiCAD Inc. 1992-2014, All Rights Reserved. // UNPUBLISHED, LICENSED SOFTWARE. // CONFIDENTIAL AND PROPRIETARY INFORMATION WHICH IS THE // PROPERTY OF ALTERNATIVE SYSTEM CONCEPTS OR ITS LICENSORS. // Running.. Loading d:\FPGA\SynaptiCAD\v2v\lib\standard.vhd, Package standard Loading input file n_f0_vhdl.vhd Loading d:\FPGA\SynaptiCAD\v2v\lib\std_logic_1164_header.vhd, Package std_logic_1164 Loading d:\FPGA\SynaptiCAD\v2v\lib\numeric_std_header.vhd, Package numeric_std n_f0_vhdl.vhd(19) : WARNING: Assignment to a sensitivity signal 'count_vhdl' in a process n_f0_vhdl.vhd(19) : NOTE: This may put a Verilog simulator in an infinite loop; see $SYNCAD_HOME/v2v/doc/vhdl2v_rel for a suggested manual fix Reading function mapping files... Reading function mapping file 'd:\FPGA\SynaptiCAD/v2v/lib/standard.fm' Reading function mapping file 'd:\FPGA\SynaptiCAD/v2v/lib/std_logic_1164.fm' Reading function mapping file 'd:\FPGA\SynaptiCAD/v2v/lib/std_logic_arith.fm' Reading function mapping file 'd:\FPGA\SynaptiCAD/v2v/lib/std_logic_unsigned.fm' Finished reading function mapping files Top-level module is 'n_f0_vhdl' NOTE: Using vector range instead for VHDL type 'integer' d:\FPGA\SynaptiCAD\v2v\lib\standard.vhd(74) : NOTE: Using Verilog type 'wire' for VHDL type 'bit_vector' d:\FPGA\SynaptiCAD\v2v\lib\numeric_std_header.vhd(40) : NOTE: Using Verilog type 'reg' for VHDL type 'UNSIGNED' NOTE: Created equivalent Verilog model for 'process_1' in architecture 'behavioral' of entity 'n_f0_vhdl' NOTE: Created equivalent Verilog model for 'process_2' in architecture 'behavioral' of entity 'n_f0_vhdl' NOTE: Adding port 'clk' of mode 'IN' to module 'n_f0_vhdl' NOTE: Adding port 'n' of mode 'IN' to module 'n_f0_vhdl' NOTE: Adding port 'clk_out' of mode 'OUT' to module 'n_f0_vhdl' NOTE: Adding 'initial' statement corresponding to process 'process_4' to module NOTE: Adding 'initial' statement corresponding to process 'process_3' to module NOTE: Adding 'always' statement corresponding to process 'process_1' to module NOTE: Adding 'always' statement corresponding to process 'process_2' to module d:\FPGA\SynaptiCAD\v2v\lib\numeric_std_header.vhd(690) : WARNING: The return size of the function is not determined. d:\FPGA\SynaptiCAD\v2v\lib\standard.vhd(71) : ERROR: Cannot elaborate 'high attribute without a 'range' in 'integer' d:\FPGA\SynaptiCAD\v2v\lib\standard.vhd(71) : ERROR: Cannot elaborate 'high attribute without a 'range' in 'integer' <<<<<< Basic translation of VHDL functions/procedures used in 'n_f0_vhdl' written to "n_f0_vhdl_behavioral.v" >>>>>>>> Due to unsupported VHDL constructs, Verilog file may not compile // <<<<<< Verilog translation of VHDL file "n_f0_vhdl.vhd" written to "n_f0_vhdl_SynaptiCAD.v" >>>>>>>> Ну и выходные файлы: n_f0_vhdl_SynaptiCAD.v: /******************************************************************************* -- File Type: Verilog HDL -- Tool Version: VHDL2verilog 20.51 -- Input file was: n_f0_vhdl.vhd -- Command line was: d:\FPGA\SynaptiCAD\bin\win32\vhdl2verilog.exe n_f0_vhdl.vhd n_f0_vhdl_SynaptiCAD.v -- Date Created: Fri May 13 22:33:13 2022 *******************************************************************************/ `define false 1'b 0 `define FALSE 1'b 0 `define true 1'b 1 `define TRUE 1'b 1 `timescale 1 ns / 1 ns // timescale for following modules module n_f0_vhdl ( clk, n, clk_out); input clk; input [31:0] n; output clk_out; reg clk_out; reg [23:0] count_vhdl; reg c_out_vhdl; initial begin : process_4 c_out_vhdl = 1'b 0; end initial begin : process_3 count_vhdl = {24{1'b 0}}; end always @(posedge clk) begin : process_1 if (clk === 1'b 1) begin count_vhdl <= count_vhdl + TO_UNSIGNED(n, 24); c_out_vhdl <= count_vhdl[23]; end end always @(posedge clk) begin : process_2 if (clk === 1'b 1) begin if (count_vhdl[23] === 1'b 1 & c_out_vhdl === 1'b 0) begin clk_out <= 1'b 1; end else begin clk_out <= 1'b 0; end end end // including file with called functions and tasks `include "n_f0_vhdl_behavioral.v" endmodule // module n_f0_vhdl n_f0_vhdl_behavioral.v: function /*[add proper size here]*/ TO_UNSIGNED; input [0:integer /* ignored attribute: 'high */] ARG; input [0:integer /* ignored attribute: 'high */] SIZE; В общем даже и не знаю. -

VHDL to Verilog

AnatolySh ответил AnatolySh тема в Языки проектирования на ПЛИС (FPGA)

Так-то оно так, но как обеспечить полноту проверки? Хотя для данного конкретного модуля, похоже, это просто. Давно хотел познакомиться, но, вот, удастся ли поиграться, особенно в современных условиях? Вот чего не знаю, того не скажу. Я, можно сказать, VHDL почти впервые вижу. Отсюда и трудности перевода.. -

"А не тормоз, я только учусь" ... Пришла пора предать огласке (суть прорекламировать) с разрешения правообладателя его изделия, обладателем одного из которых (и, даже, оказывается) двух (включая тот LPT выше) я являюсь с превеликим, не побоюсь этого слова, удовольствием. Цитирую автора (АКА StewartLittle): Только надо иметь в виду - любой LPT'шный Byteblaster не будет работать под Win x64, т.к. под эти оси нет соответствующих драйверов. Ну и, соответственно, с номерами версий квартуса нужно внимательнее быть. А еще у меня есть клон USB Blaster II, но с поддержкой только режима JTAG'а (режима AS там нет). Есть вариант с изоляцией, есть и без нее. Есть изолированный клон USB Blaster - в нем поддерживаются все режимы (JTAG/ASD/PS). Отличается он только наличием изоляцией. Ну и еще защитой выходов. Есть клон USB Blaster II, и в нём сделан только JTAG. USB Blaster II поддерживает управление частотой TCK (максимальное значение 24 МГц) и, как следствие, позволяет прошивать в ПЛИС ключи для дешифровки криптованных прошивок. USB Blaster и USB Blaster II - это принципиально разные девайсы! Вот это USB Blaster II. И да, плата сделана так, что на нем можно собрать и изолированный, и неизолированный варианты. На верхнем фото - без изоляции (голубой SOIC16 - это набор перемычек). На нижнем - с изоляцией. Может возникнуть вопрос - зачем вариант без изоляции? Все просто - наличие изоляции вносит доп. задержку в JTAG-цепочку, и на частоте TCK 24 МГц эта доп. задержка уже мешает работе JTAG'а. Поэтому тот, кто хочет работать с максимальной частотой TCK, вынужден использовать вариант без изоляции. А если для работы достаточно частоты TCK 16 МГц, то можно использовать уже и изолированный вариант.

-

Вот этот файл cmul14x16.vhd обязательно было в vhdl выводить? Я, конечно, не прочь параллельно разбираться и с этим, но умножение сущностей мешает.

-

Возможно лень разбираться с проектом, где что-то возможно лишнее

-

Не сильно понял при первом взгляде glbl.v - он для чего?

-

VHDL to Verilog

AnatolySh опубликовал тема в Языки проектирования на ПЛИС (FPGA)

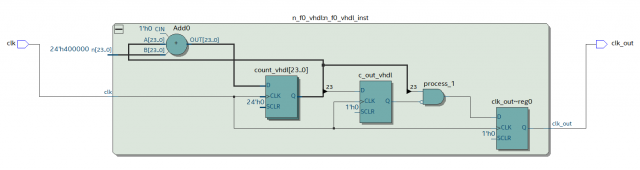

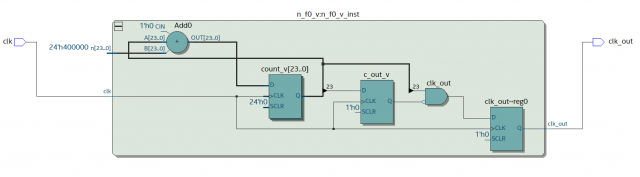

Всем добра. Имею доставшийся в наследство модуль library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity n_f0_vhdl is port ( clk : in std_logic; n : in integer range 0 to 2**24 - 1; clk_out : out std_logic ); end n_f0_vhdl; architecture behavioral of n_f0_vhdl is signal count_vhdl : unsigned (23 downto 0) := (others => '0'); signal c_out_vhdl : std_logic := '0'; begin process (clk, count_vhdl) begin if rising_edge(clk) then count_vhdl <= count_vhdl + to_unsigned(n,24); c_out_vhdl <= count_vhdl(23); end if; end process; process (clk, c_out_vhdl, count_vhdl) begin if rising_edge(clk) then if count_vhdl(23) = '1' and c_out_vhdl = '0' then clk_out <= '1'; else clk_out <= '0'; end if; end if; end process; end behavioral; который переписал на родном для меня verilog-e следующим образом `define COUNT_DIM 24 `define COUNT_RNG [ `COUNT_DIM - 1 : 0 ] module n_f0_v ( input clk, input `COUNT_RNG n, output reg clk_out ); reg `COUNT_RNG count_v; wire count_v_msb; assign count_v_msb = count_v[`COUNT_DIM - 1]; reg c_out_v; always @ ( posedge clk ) begin count_v <= count_v + n; c_out_v <= count_v_msb; clk_out <= count_v_msb && !c_out_v; end endmodule Для проверки первый и второй варианты загнал в Quartus и получил RTL модели и Можно ли утверждать, что я перевёл описание модуля с одного HDL на другой правильно? -

У некоторых вообще на работе интернета нет, так что нам с вами повезло. Скачал, дома буду курить ваши библиотеки )