Abo

Свой-

Постов

117 -

Зарегистрирован

-

Посещение

Весь контент Abo

-

ПЛИС PangoMicro Compact

Abo ответил Abo тема в Работаем с ПЛИС, области применения, выбор

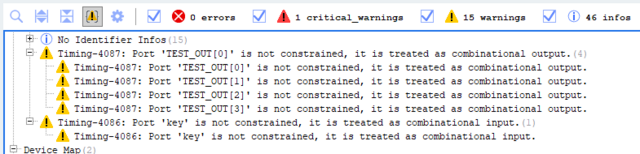

Вот еще одна удивительная штука. Похоже не работает в анализаторе PDS директива set_false_path. В приложении проект, где все входы и выходы пометил этой директивой. А анализатор все равно предупреждения пишет. Тот же проект с теми же директивами анализатора (create_clock и set_false_path) в Quartus компилируется без предупреждений. Может я неправильно задал эти констрейны? set_false_path -from [get_ports {key}] set_false_path -to [get_ports {TEST_OUT[*]}] pangotest.zip -

А там точно 5к? Такого номинала ни в ряду Е24, ни в ряду Е96 нет. Осциллограмму снимали отключив нагрузку? Землю щупа к земле ПЛИС подключили?

-

ПЛИС PangoMicro Compact

Abo ответил Abo тема в Работаем с ПЛИС, области применения, выбор

Исправили неправильно. Теперь в этом файле описание еще дальше от реальности... -

как вы писали ранее подтяжка 5кОм. а время нарастания от 0 до 3,3В судя по осциллограмме около 1мс. 1мс = 6*T = 6*RC. Ну вот и получается 1e-3s = 6 * 5e3 Ohm * С, откуда C = 3.33e-8F или 33nF.

-

или конденсатор на 33нФ параллельно подключен (если подтяжка 5кОм) - это весьма похоже.

-

Как я понял, вы логическим анализатором смотрите, а что аналоговый вход осциллографа показывает? Может там емкость какая через подтяжку заряжается?

-

ПЛИС PangoMicro Compact

Abo ответил Abo тема в Работаем с ПЛИС, области применения, выбор

Перевод оригиналу соответствует, а вот оригинал фактам нет. В китайском варианте UG030003 одно написано, в UG030008 другое. Перевода UG030008 на фтп нет. А вот вход разрешения не влияет на выход - это я сам наблюдал. -

ПЛИС PangoMicro Compact

Abo ответил Abo тема в Работаем с ПЛИС, области применения, выбор

Продолжил эксперименты с с блоком GTP_OSC_E2. У него, судя по описанию 2 выхода (CLKCRC с фиксированной частотой 2,08МГц, CLKOUT с выхода делителя, коэфф. деления задается параметром). Так вот, на выходе CLKCRC сигнала нет ни при каких условиях. У блока также есть вход EN_N,который должен разрешать выход CLKOUT. Так вот он тоже не оказывает на него никакого влияния - сигнал на выходе CLKOUT всегда есть. Хорошо хоть делитель работает как описано. Вот такая понимаешь загогулина китайская.... -

ПЛИС PangoMicro Compact

Abo ответил Abo тема в Работаем с ПЛИС, области применения, выбор

Благодарю за участие. А вот интересно, у китайцев напрямую можно об этом спросить? Письмо может им написать, переведя гуглом на иероглифы? -

ПЛИС PangoMicro Compact

Abo опубликовал тема в Работаем с ПЛИС, области применения, выбор

Приветствую, коллеги. Пришлось осваивать Панго серии компакт. Сделал простенький тестовый проект с использованием встроенного в микросхему генератора (в приложении весь проект). сделал констрейны на клоки и выходы. Однако при сборке получаю критическое предупреждение: "Place-2028: CASCADED_GLOBAL_CLOCK: the driver GTP_OSC_E2_inst/gateop fixed at OSC_11_174 is unreasonable. Sub-optimal placement for a clock source and a clock buffer." Не понятно, как от этого предупреждения избавиться. Чтение доступной документации и поиск не привели даже к догадке, где искать ответ. Может конечно не все прочитал. Прошу совета, куда рыть? Ну не могу я себе позволить оставлять в проектах даже предупреждения. pangotest.zip -

ПЛИС PangoMicro

Abo ответил Gas Wilson тема в Работаем с ПЛИС, области применения, выбор

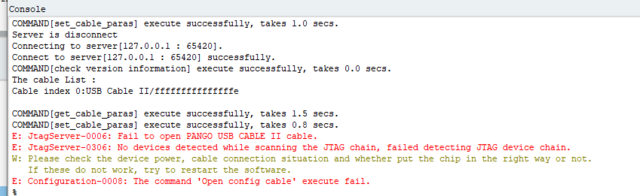

Да, родная FT2232H опознается программатором от PDS (сканировать цепочку не пробовал - нечего подключить) , а вот ее эмуляция на BL702 c платы TangNano9K c подключенной плис говин не опознается при сканировании цепочки. -

ПЛИС PangoMicro

Abo ответил Gas Wilson тема в Работаем с ПЛИС, области применения, выбор

Коллеги, подскажите пожалуйста, а какой JTAG адаптер нужно использовать с PDS и где его в наших условиях купить? И еще: LATTICE HW-USBN-2B говорят подходит. Это правда? -

Tang Nano 20K

Abo ответил ValeiyT тема в Работаем с ПЛИС, области применения, выбор

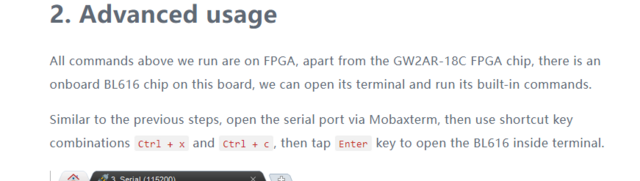

Если почитать дальше то будет видно: То есть, последовательность ^x ^c мониторится BL616 и если встречается в пользовательском вводе, то открывается командный процессор в BL616. После этого становятся доступны команды управления PLL. Отсюда вывод: нет необходимости в наличие какой либо конфигурациии в ПЛИС для управления PLL, достаточно послать в терминале указаную последовательность, что по моему весьма логично. -

Благодарю за информацию. Были предположения, что для говина критичны частота и необходимость дополнительных импульсов на TCK в RunTest состоянии. К сожалению openFPGALoader прикрутить будет сложно, в нашем случае все упирается в быстродействие МК (CY7C68013) который ногами JTAG управляет. Ну никак требуемых 2 МГц (судя по доке говина) он не надрыгает, да и прерывания нельзя запретить - а они будут лаги по длительности импульсов на JTAG давать - ногами в фоне дрыгаем. По поводу кривости SVF от говина. Я с разработчиками из туманного Альбиона прошлой весной три месяца общался и к версии 1.9.8.6 они выкатили вполне удобоваримый генератор SVF, который учитывает наличие дополнительных микросхем в цепочке - у меня в устройстве в одной цепочке сразу 4 плисины. Наш плейер его прожевал без ошибок, вот только запрограммировать не удалось. Буду неспеша придумывать варианты. Производству придется тыкать программатор. Может это и к лучшему.

-

Здравствуйте всем, После трудностей с закупкой макс10 от альтеры перетоптали изделие на плис от говина GW1N-9LQ. Изначально альтеровская плис шилась прямо в устройстве через JTAG рядом стоящим МК самописным SVF плейером. Попытка проделать этот трюк с говином не удалась, SVF файл проигрывается - плисина не шьется, вылетает с ошибкой при сравнении. FTDI программатор шьет без вопросов. Производство ворчит, отвыкли уже программатор тыкать и вот опять. Кто-нибудь может подсказать в чем особенность JTAG у говина по сравнению с альтерой. Да, кстати, наш МК выдает максимум только 1,8МГц на JTCK, насколько это критично?

-

Добрый день, тема еще актуальна?

-

Кадый такт к счетчику прибавляете M и сравниваете резльтат с N. Если значение в счетчике больше или равно N, то формируете импульс на шаг и разность счетчика и N пишете в счетчик. Обнулять счетчик при смене N и M не нужно.

-

Мне тоже потребовалось сделать кордик для расчета арктангенса. Воспользовался этим кодом. Благодарю автора. Со своей стороны прикладываю немного ускоренный вариант с хранением сдвинутого предыдущего значения в отдельном регистре. До изменения на 10M50 максимальная тактовая была не более 119МГц, после выросла до 137МГц. Мне нужно было чтобы при 120МГц работало. module cordic_core #( parameter SIG_W = 18, parameter ACC_W = 20 )( input rst, input clk, input req, input ccwr, input signed [SIG_W:0] x_i, input signed [SIG_W:0] y_i, input signed [ACC_W+1:0] a_i, output rdy, output busy, output reg signed [SIG_W:0] x_o, output reg signed [SIG_W:0] y_o, output reg signed [ACC_W+1:0] a_o ); `define ANG_SCALE(s) (ACC_W < 32) ? \ (ACC_W+2)'(unsigned'(``s`` >>> (32-ACC_W)) + unsigned'(1'(``s`` >> (32-ACC_W-1)))) : \ (ACC_W+2)'(``s``) localparam logic signed [ACC_W+1:0] ANG_TABLE[31] = '{ `ANG_SCALE(32'sd536870912), `ANG_SCALE(32'sd316933406), `ANG_SCALE(32'sd167458907), `ANG_SCALE(32'sd85004756), `ANG_SCALE(32'sd42667331), `ANG_SCALE(32'sd21354465), `ANG_SCALE(32'sd10679838), `ANG_SCALE(32'sd5340245), `ANG_SCALE(32'sd2670163), `ANG_SCALE(32'sd1335087), `ANG_SCALE(32'sd667544), `ANG_SCALE(32'sd333772), `ANG_SCALE(32'sd166886), `ANG_SCALE(32'sd83443), `ANG_SCALE(32'sd41722), `ANG_SCALE(32'sd20861), `ANG_SCALE(32'sd10430), `ANG_SCALE(32'sd5215), `ANG_SCALE(32'sd2608), `ANG_SCALE(32'sd1304), `ANG_SCALE(32'sd652), `ANG_SCALE(32'sd326), `ANG_SCALE(32'sd163), `ANG_SCALE(32'sd81), `ANG_SCALE(32'sd41), `ANG_SCALE(32'sd20), `ANG_SCALE(32'sd10), `ANG_SCALE(32'sd5), `ANG_SCALE(32'sd3), `ANG_SCALE(32'sd1), `ANG_SCALE(32'sd1) }; `undef ANG_SCALE localparam CNT_W = $clog2(ACC_W+1); localparam [CNT_W-1:0] LAST_CNT = (CNT_W)'(ACC_W) - 1'b1; logic busy_t1; logic [4:0] i; // Изначально разрядность была настраиваемой [CNT_W-1:0], изменил чтобы квартус не предупреждал. logic signed [SIG_W:0] x_s, y_s; assign busy = (i < LAST_CNT); assign rdy = (~busy & busy_t1); wire signed [SIG_W:0] next_x_o = (ccwr) ? (x_o - y_s) : (x_o + y_s); wire signed [SIG_W:0] next_y_o = (ccwr) ? (y_o + x_s) : (y_o - x_s); wire signed [SIG_W:0] next_x_s = signed'(next_x_o >>> (i+1'b1)); wire signed [SIG_W:0] next_y_s = signed'(next_y_o >>> (i+1'b1)); always_ff @(posedge clk, posedge rst) begin if(rst) begin busy_t1 <= 0; i <= '1; x_o <= 0; y_o <= 0; x_s <= 0; y_s <= 0; a_o <= 0; end else begin busy_t1 <= busy; if(req | busy) if(req) begin i <= 0; x_o <= x_i; y_o <= y_i; x_s <= x_i; y_s <= y_i; a_o <= a_i; end else begin i <= i + 1'b1; x_o <= next_x_o; //(ccwr) ? (x_o - y_s) : (x_o + y_s); y_o <= next_y_o; //(ccwr) ? (y_o + x_s) : (y_o - x_s); x_s <= next_x_s; y_s <= next_y_s; a_o <= a_o + (ccwr ? ANG_TABLE[i] : -ANG_TABLE[i]); //(ccwr) ? (a_o + ANG_TABLE[i]) : (a_o - ANG_TABLE[i]); end end end endmodule

-

К сожалению не оно. При этом запускается еще одна копия отладочной DLL и контрольной панели. В ней можно установить адрес командой exec SetRTTAddr и подключиться вьюером. Но при начале отладки будет запущена новая копия отладочной Dll, которая адрес уже не знает, загрузка и отладка будет идти через нее и после кейл упадет.

-

По прочтению статьи Дебаггинг в реальном времени через JTAG/SWJ-DP для микроконтроллеров на ядре ARM Cortex-M, решил попробовать рецепт на ядре M4 мк LPC4337. Столкнулся со следующей трудностью: сервер отладки, который запускается IDE в начале отладочного сеанса не находит автоматически адрес структуры _SEGGER_RTT в ОЗУ. Ввести адрес вручную на вкладке RTTerminal окна "Control panel" не получается - там какое-то странное поле ввода, которое само постоянно обновляется (у меня версия софта 5.00I). В мануале от сеггера предлагают заставить отладчик самостоятельно передать адрес: In some cases J-Link cannot locate the RTT buffer in the known RAM region. In this case the possible region or the exact address can be set manually via a J-Link exec command: Set ranges to be searched for RTT buffer: SetRTTSearchRanges <RangeStart [Hex]> <RangeSize >[, <Range1Start [Hex]> <Range1Size>, ...] (e.g. "SetRTTSearchRanges 0x10000000 0x1000, 0x2000000 0x1000") Set address of the RTT buffer: SetRTTAddr <RTTBufferAddress [Hex]> (e.g. "SetRTTAddr 0x20000000") Set address of the RTT buffer via J-Link Control Panel -> RTT J-Link exec commands can be executed in most applications, for example in J-Link Commander via "exec <Command>", in J-Link GDB Server via "monitor exec <Command>" or in IAR EW via "__jlinkExecCommand("<Command>");" from a macro file. вот только как это сделать в Кейле тут не указано. Кстати, Если попытаться с помощью JLinkRTTViewer открыть еще одну сессию (при запуске этой утилиты можно указать адрес структуры _SEGGER_RTT) то отладочный вывод идет, но после выхода из отладочного режима в кейле и закрытия JLinkRTTViewer, кейл падает. Если же запускать JLinkRTTViewer так, чтобы он подключалась к уже запущенному отладочному процессу и потом автоматически реконнектился к нему, то естественно вывода нет - поскольку адрес структуры не найден, и задать его во вьюере нельзя. Прошу указать способ, как в отладчике кейла послать команду JLink серверу?

-

У nxp или ad поищите не тему видеоАЦП ( ADV7xxx - что-такое), в них как правило и коммутатор не несколько источников есть. Эти АЦП имеют на выходе синхронный параллельный (а может есть и с последовательным) интерфейс для содержания и сигналов синхронизации (кадры и строки). Таким образом -для приема с АЦП синхронный интерфейс с ПДП и ОЗУ на кадр. Но четкость с обычной видеокамеры наверняка будет не очень. Я бы предпочел построить систему на IP камерах и озаботиться лишь обеспечением канала связи (камеры должны частоту кадров под канал подстраивать) и ничего не придумывать - все уже придумали за нас, надо только правильно воспользоваться.

-

Любая 32х разрядная винда (даже семерка) не требует цифровой подписи от драйвера и прекрасно его грузит. А вот 64х разрядные версии, начиная с Vista, грузят драйверы без подписи только в специальном - тестовом режиме (при этом в углах или сверу рабочего стола отображается надпись "Test Mode"). Переключиться в этот режим можно с помощью утилиты bcdedit.

-

А нельзя ли заполучить от Вас эту новую версию документа, а то на ТИ до сих пор старая еще лежит.

-

Я вот так половину тактовой частоты периферии подаю на вывод 46 // Настраиваем входные и выходные сигналы PINSEL0 = (PINSEL0 & ~(0)) | 0x0; // Вывод 46-P0.16 как MAT0.2 // Вывод 3-P0.21 как МАТ3.0 PINSEL1 = (PINSEL1 & ~((3<<0)|(3<<2)|(3<<4)|(3<<6)|(3<<8)|(3<<10))) | ((2<<0)|(2<<6)|(2<<8)|(2<<10)); // Настраиваем таймер 0 на выдачу сигнала SCK частотой 12,8 МГц - половина тактовой PCONP |= PCONP_PCTIM0; // Подаем питание на таймер T0TCR = 2; // Остановим и сбросим таймер T0CTCR = 0; // Работа в режиме таймера T0PR = 0; // Предделитель не используется - на таймер подается CCLK 25,6 МГц T0MR0 = 1; // Определяет период выходного сигнала T0MR2 = 1; // Определяет период выходного сигнала T0MCR = T0MCR_MR0R; // Сброс по совпадению с MR0 T0EMR = 0; T0CCR = 0; // Запретить режим захвата по всем входам PWM0CON = 1<<2; // Разрешим генерацию PWM на выходе MAT0.2

-

резисторы нужны не для защиты от статики, а для снижения уровня излучаемых помех за счет завала крутых фронтов сигналов. Для этого кроме резисторов еще и кондюки на 27 пик ставят на землю на каждую линию данных. Правда это работает только для Low и Full Speed. На High Speed не знаю что ставить.