-

Постов

12 216 -

Зарегистрирован

Весь контент ViKo

-

Помогите разобраться

ViKo ответил Andruxa-1 тема в Программирование

То, что вам предложили позже (union), вообще не потребует преобразований. -

SystemVerilog::struct и Questa

ViKo ответил dxp тема в Среды разработки - обсуждаем САПРы

Может быть, в данном случае помогли бы интерфейсы вместо структур? -

Я вижу в перечислении state 3-битовые значения.

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

По-началу хотел написать "для луноходов", но подумал, крутовато будет :) В-общем - туда, где нужна безотказная работа. Хотя для этого делается несколько компьютеров, работающих параллельно. ? -

Рахмат!

-

тест на IQ? я не прошел :(

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Я не знаю. Пусть ПЛИС будет неоптимальна для подобной разработки. Но все же лучше, чем ничего. Для доказательства преимуществ асинхронного процессора хватило бы, наверное. Мне кажется, что идеи (только первичные идеи, про дальнейшую реализацию молчу) могли бы пригодиться при разработке компьютеров для роботов и т.п., если нужна "безотказность" вычислений в первую очередь, а уж потом быстродействие. Т.е., если не получается вычислить быстро, пусть процессор "подумает" над командой еще, пока не "осилит". -

:bb-offtopic: Я воспринимаю сокращения des как designer, что вполне подходящий ник для известных нам участников форума. А Денис я бы сократил до Den. Может быть, они просто постеснялись ответить по-настоящему? :) А про цифры... скажете что-нибудь? :)

-

"Звиняйте, дядьку!" (С) Б.Г. Нашел черновик http://www.eda.org/vlog-synth/vlogrtl.pdf В "закрома" не заглядывал.

-

IEEE 1800-2009 SystemVerilog.

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Хочу еще добавить пару слов. Кто мешал упомянутым "академикам" запихнуть свое "изобретение" в ПЛИС, у которой перед каждым триггером с синхронным входом есть асинхронная 4-х-входовая таблица просмотра (истинности)? Ну, пусть было бы нерациональное использование, но весь их PIC уложился бы в ПЛИС (а то и оба - синхронный и асинхронный, и еще осталось бы для схем тестирования). Не все идеи, старые, как мир, проходят проверку временем. Прогресс вообще петляет, как заяц. Но неизменно продвигается вперед. Я не отвергаю асинхронные схемы. Но критерий истины - практика. Пока что практических доказательств преимуществ асинхронности я не увидел. -

Вы будете смеяться, но это - ошибка в стандарте! В IEEE 1800-2009 в разделе 23.10 написано: always @(posedge clk or posedge reset) begin casez ({read,write,reset}) // implementation of fifo endcase end

-

Кажется, по моей вине мысли участников двинулись не в том направлении. На всякий случай сообщаю - в строке always задается список чувствительности компилятора, а не самого триггера. Т.е. - по какому событию компилятор должен синтезировать схему, чтобы получить требуемый результат. Запись always @(rst) означает чувствительность к любому изменению сигнала rst, но никак не к его уровню. В Verilog вообще нет смысла рассматривать сигналы, если они находятся в неизменном состоянии. Это я так "пошутил" насчет always @(posedge clk or rst). upd. вот, кстати, собачки @ забыл, а в них - вся соль! исправляюсь.

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

У статьи 5 авторов, не считая рецензентов, помощников, и т.д. Они что, камень с Луны исследуют? Связь с изготовителем БМК потеряна навсегда? На рис. 6 при напряжении ниже 1V (кстати, почему там цифры 3,1 2,1 1,1 В - обычное разгильдяйство) рабочая частота падает до 0. Примерно так выделяются сигналы на фоне шумов - накапливаем, накапливаем, потом какой-то результат получаем... -

Вот именно! :) А на чем писать... сами знаете :)

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Вы серьезно рассматриваете данную статью как пример, доказывающий преимущества асинхронных схем? Пробежав ее по-диагонали, я в очередной раз убедился во мнении, что академики даром едят свой хлеб. Ничем иным, кроме попыток выбить "бабла", я не могу оправдать данную "тему". Вот один из "перлов": Вот как надо быстродействие повышать! :) Долой амперметры!! А по-серьезному: - Не увидел никакой разницы между рис 1,а и 1,б. А на этом основана вся дальнейшая работа. - Работа, требующая подтверждения своей завершенности, не может выполниться быстрее, если бы подтверждения не требовалось. Исключения - когда какая-то процедура (умножение, например) требует намного большего времени, чем остальные действия. Если привязывать такты к такой команде, придется терять время для остальных. Поэтому такие команды выполняются за несколько тактов. - PIC18 работают на частоте 40MHz, выполняют команду за 100ns (4 такта). Вот оно, преимущество конвейера (вспомним еще раз Pentium4). - еще примерчик - синхронные и асинхронные интерфейсы - какие быстрее? upd. извиняюсь, не быстродействие, а потребление уменьшать с помощью исключения амперметра -

Можно и так :) И, начиная с Cyclone II, иметь 4 ЛЭ для каждого такого триггера. А до этого семейства использовался бы 1 ЛЭ. Регресс? :) Нет, Verilog :) Вот и получается, если писать не глядя на внутреннее устройство ПЛИС, можно не получить желаемой красоты, быстродействия, экономии... P.S. По-прежнему уверяю Verilog в своей полной симпатии :)

-

У Keil есть чуть более "хитрый" файл ini FUNC void Setup (void) { SP = _RDWORD(0x20000000); // Setup Stack Pointer PC = _RDWORD(0x20000004); // Setup Program Counter _WDWORD(0xE000ED08, 0x20000000); // Setup Vector Table Offset Register } LOAD RAM\Blinky.axf INCREMENTAL // Download Setup(); // Setup for Running G ,main // Выполнить программу до main Blinky.axf, понятно, должен быть скомпилирован для RAM.

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

В ссылках, что Вы привели ниже, не говорится про PIC. Если имелся в виду подобный проект, на ПЛИС, то не в быстродействии ли самой ПЛИС заложена такая скорострельность ПИКа? В самом ПИКе каждая команда выполняется за 4 такта (если помните, в 51-й микроЭВМ их было 12). Если эти 4 такта слепить в один, то, наверное, можно сделать устройство слегка более быстрым. Быстродействие будет определяться длительностью самой сложной команды. Как здесь писали, ценой аппаратных затрат. Но асинхронным от этого процессор все равно не станет. Беда в другом. В соседних темах о том же говорится. Если на триггере есть асинхронный сброс, который может кончиться в момент тактового сигнала - вот вам метастабильное состояние! Вам это надо? P.S. Еще примерчик - если не ошибаюсь, в Intel Pentium4 глубина конвейера была 20 тактов. А там, надеюсь, не дураки сидят. -

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Я сомневаюсь. Можно попытаться объяснить теоретически, что предельное быстродействие будет определяться теми же временами предустановки, удержания и распространения. Но лучше попробовать на практике. Если что-то получится, я напишу позже. Возможно, Вы и правы. В синхронной схеме есть гарантированное время для каждой ступени. -

Бывали и такие, не раз. Теперь я сам себе заказчик. Стало намного легче. :)

-

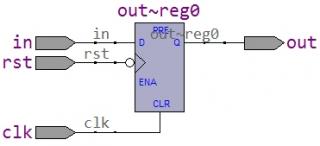

Мне об этом сам Quartus уже сказал :) И я его вполне понимаю и принимаю, осознавая логику Verilog. to all А хотите еще напрячь мыслительные способности? Опишите триггер с синхронным входом d, тактовым clk, и двумя аcинхронными rst_n, prn_n сброса и установки, которые были во всех триггерах ACEX, и в Cyclone, а в Cyclone II и III уже нет (и, кажется, я догадываюсь, почему :)).

-

С заказчиком можно и нужно договариваться. Потому что обычно он сам не знает, чего хочет. И тем более не знает, как это сделать лучшим образом.

-

2 bogaev_roman module Locker2 (input clk, rst, in, output out); always @(posedge clk, negedge rst) if (clk) out = 0; else out = in; endmodule

-

Хотите, я после этого заголовка напишу такое, что rst_ заведется на тактовый вход, а rx_outclock на сброс? Обидеть меня хотите:)?