-

Постов

12 216 -

Зарегистрирован

Весь контент ViKo

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Пока быстродействие ПЛИС позволяет делать схему тактированной, так и нужно делать. Как только потребуется что-то более быстрое, например, задержать сигнал на 0.2 ns, или выработать коротенький импульс, придется использовать асинхронные решения. Одно из известных применений Latch - фиксация адреса по мультиплексированной шине address-data во многих микропроцессорных системах по сигналу ALE. В этом случае адрес на выходе защелки появляется раньше, чем если бы использовался синхронный триггер. Получается больше времени установления для подключенных к шине адреса устройств. -

И еще один вывод получился. Если я загружаюсь из флэш, установив перемычки в (0,0), то я могу доступиться к флэш по нулевым адресам и по 0x08000000. А также я могу доступиться и в систем память (загрузчик) по адресам 0x1ffff000.

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Нет, конечно. Поэтому такие же рекомендации будет давать каждый производитель ПЛИС :) Когда сигнал изменяется по тактам, можно получить большее быстродействие, чем когда он меняется, когда захочет. Это (нерекомендация latch) вытекает из неприятия "асинхронщины". -

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

потому что у нее в каждом триггере есть нормальный тактовый вход clk -

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Во всяком случае, Quartus предлагает следующий шаблон для case: case(<constant_expr>) <constant_expr>: begin : <block_name> // Generate Items end <constant_expr>: begin : <block_name> // Generate Items end // ... default: begin : <block_name> end endcase // NOTE: Block names are optional but Altera recommends them. Кстати... Это не оплошность, а осознанное решение. Ничего плохого в нем нет. Именно - триггер-защелка, применяется часто. Пример - 74HC373 - Octal 3-State Noninverting Transparent Latch. Бывают защелки "полезные", а бывают "непредусмотренные" :) -

Выдайте свой скрипт, если не жалко. Джамперы есть, а как же. Дальнейшие размышления привели к следующим выводам. Загрузка из флэш или систем понятна - выставил джамперы, сбросился, скакнул в адрес 0x0, прочитал, куда назначить стек, скакнул в 0x4, прочитал и перешел на адрес. Можно сразу задать, что микроконтроллер имеет память по нулевым адресам. А при загрузке из ОЗУ на нулевые адреса ничего не отображается. Т.е. по нулевым адресам ничего нет. Как тогда прочитать вектор сброса? В отладчике это можно сделать предварительно, настроив VTOR 0xE000ED08 (кстати, а это где описано? с ходу не нашел).

-

Вынужден признать, что слова Aprox имеют под собой основание. Самого несколько напрягает подобного вида запись always @(posedge rx_outclock or negedge rst_) из которой не очевидно, что один вход работает по фронту, а другой по уровню. А написать так always @(posedge rx_outclock or rst_) увы, нельзя!

-

За ссылку в мануал спасибо, это я проглядел... А грузиться из RAM - в первую очередь хочу разобраться в механизме. А во вторую - жалко флэш насиловать - чуть что-то изменил в программе, заходишь в отладку - опять зашивай!

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Это - не триггер-защелка. Защелка (Latch) - это триггер, который передает входной сигнал, когда L = 1 (прозрачный), и не передает входной сигнал, когда L = 0. В момент перехода L из 1 в 0 триггер "защелкивает" сигнал, а до этого момента сигнал на выходе мог меняться вместе с входным. P.S. А для case есть слово default. -

Попробую сформулировать вопрос проще. Как получается, что флэш начинается с 0x08000000, RAM с 0x20000000, а таблица векторов с 0? Где же она физически находится?

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Ну, нехай так будет. И то, и другое легко сделать в любой ПЛИС :) Вот пример, выполняющий то же самое. Но на него Quartus ругается, как на комбинационную петлю. assign out = in & en | out & !en; -

Потому что это температура кристалла, которая обязательно будет высокой, вплоть до 135 градусов. Если вы сможете обеспечить идеальный теплоотвод, т.е. отводить все образующееся тепло, то и температура среды (верхняя графа) может быть такой же, что и указано в верхней строке.

-

Защелки в FSM

ViKo ответил Fynjisx тема в Работаем с ПЛИС, области применения, выбор

Вот пример защелки assign out = in & out; -

Пытаюсь запускать программу из RAM STM32F103. Тренируюсь на примере и плате Keil\ARM\Boards\Keil\MCBSTM32\STLIB_Blinky. Там задаются начало и размер ROM 0x20000000 и 0x4000, RAM 0x20004000 и 0x1000, при отладке загружается файл RAM.ini, в котором выполняется загрузка кода в RAM, и с помощью функции устанавливается указатель стека и сброс на 0x20000000 и 0x20000004, и задается смещение 0x20000000 в регистр таблицы векторов. Вопрос - почему перемычки BOOT0, BOOT1 не влияют на то место, куда и откуда загружается и запускается код отладчиком? Почему, когда нажимаю сброс в отладчике или непосредственно на плате, при установленных перемычках 1,1 (RAM), программа не работает. Кто-то портит содержимое RAM. А если перемычки в 0,0 (Flash), то запускается программа, записанная в Flash. Еще вопрос - есть ли способ не перемещать код в адреса RAM, а с помощью перемычек отразить область 0x00000000 на адреса RAM, и занести код сразу в RAM?

-

Просто логически неправильно подавать один и тот же сигнал rx_locked и на тактовый вход триггера, и на вход данных. В AHDL "такую глупость" тоже никто не мешает сделать :)

-

Если ваши имя и фамилия - И.П., тогда знаю. Кстати, именно Васильев научил меня AHDL, и на реальном проекте, и просто как учитель (приходил к нам, молодой и зеленый), а потом я решил, что и сам так смогу :)

-

:bb-offtopic: Точно, он. Я уже и фамилию забыл... Да и Вами, возможно, я имел дело :) И с Вашим другом, Васильевым. То ли Вы не умеете ясно выражать мысли, то ли я такой тупой... Что Вы хотели сказать? Ну хоть убей, ... :) Лучше не касаться скользкой темы "халява". upd. По-моему, в то время все программы были бесплатными :)

-

Это не про меня. Я еще помню, как к нам заходил дядечка, заманивал на Altera. Показывал PALASM и т.п. И таки сманил. И так как я сам решаю, что применять, пока обхожусь одной Altera. Вот оно, преимущество универсальных языков: захотел Xilinx - слегка подредактируй код, и пользуйся.

-

Удовлетворите мое любопытство - какой язык предлагала использовать в разработках фирма Xilinx до VHDL и Verilog? Неужели AHDL? А другие производители?

-

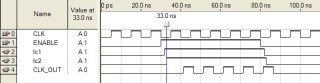

Вот так я сделал в Quartus на SystemVerilog module Clocker (input wire CLK, ENABLE, output bit CLK_OUT); bit Tmp1, Tmp2; lcell lc1 (ENABLE, Tmp1); lcell lc2 (Tmp1, Tmp2); assign CLK_OUT = CLK & Tmp2; endmodule Для частоты 100 MHz (так нагляднее). И в настройках запретил игнорировать LCELL и выбрасывать избыточные LCELL.

-

Только если на плечах нет головы. В ином случае все можно сделать идеально. 2 Muscat За это время можно было перепробовать все варианты.

-

Когда Вы пишете #ifndef RTC_H_ следующей строкой должно быть #define RTC_H_ чтобы содержимое данного файла не подключалось к проекту дважды

-

Подтверждаю свое участие. Перевожу 25 главу про Интерфейсы, в тесном сотрудничестве с Vadim

-

Проблемы с МК LPC2114

ViKo ответил galex1981 тема в ARM, 32bit

2 Алекс1981 Так у Вас неправильно включены стабилизаторы питания! На вход ничего не подано, зато подано на выход! "Ну кто так строит?!" -

А spice модель можно где-то добыть? Я так понимаю. До 20 MHz работает конденсатор. После 100 MHz сказывается индуктивность выводов, что подключаются на землю (хоть там их и нет, одни площадки). А вот между этими частотами влияет индуктивность проводника между входом и выходом. Возможно, получается из-за особых свойств используемых материалов (NFM?). Из-за этого имеется плоская область на характеристике. Если про эту область забыть, получаем характеристики обычного конденсатора. Но с особыми конструктивными свойствами. У ферритовых бусин свойства индуктивности сохраняются до 100 MHz (дальше не рисуют графики, у Murata смотрел). Надеюсь, и дальше продолжится то же. Поэтому, как минимум, в диапазоне до 20 MHz в фильтре будут работать и бусина, и проходной конденсатор (так же, как и любой другой). Подавление помех будет лучше. И после 100 MHz подавление, как минимум, не будет ухудшаться. upd. А про антирезонансный пик (из-за которого тема возникла) я понимаю так. LC-цепи образуют по отношению к ногам питания ФАПЧ параллельный резонансный контур, на котором сопротивление возрастает. Любые скачки потребления в цепи ФАПЧ будут выделяться на этом сопротивлении (они будут малы, но джиттер ФАПЧ увеличится). Чтобы уменьшить импеданс, увеличивают емкость конденсаторов.