-

Постов

12 216 -

Зарегистрирован

Весь контент ViKo

-

какова роль кристалла в радиприёмнике?

ViKo ответил tadeus999 тема в В помощь начинающему

А можно, я скажу?! Кристалл (кварцевый резонатор) может использоваться во втором гетеродине в приемниках с двойным преобразованием частоты. Сначала переносят входной сигнал на первую промежуточную, обычно высокую. Так хорошо давится зеркальный канал. Потом переносят на более низкую, которую проще усиливать. Вот для второго преобразования может использоваться стабильный кварцевый резонатор. А можно и просто в качестве фильтра ПЧ использовать керамический фильтр. Не совсем "кристалл". -

255 или 256?

ViKo ответил lun тема в В помощь начинающему

Я на 50% уверен, что разработчики АЦП сами запутались в этом вопросе, когда писали в документации, что делить нужно не на степень двойки. В принципе, ошибка небольшая. А процедура деления на 1023, например, отъест кучу ресурсов. Ну и нахера хоть кому-нибудь это нужно? -

надо думать, IEEE Std 1364.1-2002, IEEE Standard for Verilog Register Transfer Level Synthesis если этот, то он уже слегка устарел.

-

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

На самом деле все как раз наоборот. Нет языка Verilog, а есть и будет SystemVerilog. Потому и последний стандарт называется IEEE Standard for SystemVerilog. Вашему коду да еще бы комментариев - цены бы не было! :) -

255 или 256?

ViKo ответил lun тема в В помощь начинающему

Нарисуйте в тетрадке в клетку кубики с номерами 0...15, а потом сосчитайте их количество. Основы бытия вернутся на свое место. И в этом, и во всех других делите на 1024! -

Создать файл ram.ini такого вида: FUNC void Setup (void) { SP = _RDWORD(0x20000000); // Setup Stack Pointer PC = _RDWORD(0x20000004); // Setup Program Counter _WDWORD(0xE000ED08, 0x20000000); // Setup Vector Table Offset Register xPSR = 0x1000000; // Set Thumb State bit } RESET MAP 0x64000000, 0x6407ffff read write MAP 0x6c000000, 0x6c03ffff read write MAP LOAD RAM\Blinky.axf INCREMENTAL // Download to RAM Setup(); // Setup for Running G, main // Go! И задать его в установках отладчика.

-

Так вам RAM или Flash нужно? Поначалу получалось, что ОЗУ. Во Flash вы не сможете писать непрерывно. Надо ж будет когда-то и стирать. Я использую M25PE40.

-

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

Не впихнет. Вернее, впихнет, но потом ненужное отрежет. Как плохому танцору. :) А что, в VHDL, сколько битов задашь, столько и будет в проекте? Даже если переменная integer изменяется в диапазоне 1, 2, 3? Или это уже вообще не относится к сфере ответственности языка? А к синтезатору? -

Что, и временные диаграммы будут разные?

-

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

А в SV есть :) longint 2-state data type, 64-bit signed integer -

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

bit [26:0] timer; Ну, будет с запасом на 30% на уход длительности туды-сюды. -

А я сумел обмануть Quartus. module tst_edge2( output reg q=0, input a,b ); assign c = a; always@(posedge a, negedge c) q<=q^a^b; endmodule

-

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

Я думаю, лишние разряды создаваться физически не будут. -

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

Самому, почему нет? Может быть так - enum bit [26:0] {fst_addr = 100_000_000, next_addr[0:4095]} address; А int 32-разрядный, вам хватит :) -

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

Но возможно! Или делать перечислением, "по-глупому", или "забить" и делать, как получится. Если размер кратен степени 2, можно вектор приспособить. bit [9:0] i Диапазоны и есть. An enumerated type declares a set of integral named constants. И даже более того. По умолчанию - набор int, 32-битовых знаковых целых. Но можно задать тип и другой, по своему желанию. enum bit [3:0] {bronze='h3, silver, gold='h5} medal2; Вот и получили числа нужной размерности и заданного диапазона. -

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

Я думаю, если переменная выйдет за пределы перечисления, как минимум, получим предупреждение. А вообще, неявное приведение типов как в C, так, надо думать и в SV, широко распространено. На форуме есть более продвинутые "гуру", может, они скажут свое веское слово... upd. Даю слово стандарту: Enumerated types are strongly typed; thus, a variable of type enum cannot be directly assigned a value that lies outside the enumeration set unless an explicit cast is used or unless the enum variable is a member of a union. This is a powerful type-checking aid, which prevents users from accidentally assigning nonexistent values to variables of an enumerated type. The enumeration values can still be used as constants in expres- sions, and the results can be assigned to any variable of a compatible integral type. Enumerated variables are type-checked in assignments, arguments, and relational operators. Enumerated variables are auto-cast into integral values, but assignment of arbitrary expressions to an enumerated vari- able requires an explicit cast. -

Ну, значит нужно аккуратнее пользоваться асинхронными сигналами.

-

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

есть перечисления enum For example: typedef enum { add=10, sub[5], jmp[6:8] } E1; This example defines the enumerated type E1, which assigns the number 10 to the enumerated named con- stant add. It also creates the enumerated named constants sub0, sub1, sub2, sub3, and sub4 and assigns them the values 11...15, respectively. Finally, the example creates the enumerated named constants jmp6, jmp7, and jmp8 and assigns them the values 16 through 18, respectively. -

255 или 256?

ViKo ответил lun тема в В помощь начинающему

И это правильно! (с) М.С.Г. я картинку показал -

255 или 256?

ViKo ответил lun тема в В помощь начинающему

-

VHDL or Verilog

ViKo ответил D-Luxe тема в Языки проектирования на ПЛИС (FPGA)

Смотрите что есть у Quartus 9.1, по крайней мере, декларировано: The Quartus II software supports the following SystemVerilog constructs: ■ Parameterized interfaces, generic interfaces, and modport constructs ■ Packages ■ Extern module declarations ■ Built-in data types logic, bit, byte, shortint, longint, int ■ Unsized integer literals ‘0, ‘1, ‘x, ‘z, ‘X, and ‘Z ■ Structure data types using struct ■ Ports and parameters with unrestricted data types ■ User-defined types using typedef ■ Global declarations of task/functions/parameters/types (does not support global variables) ■ Coding constructs always_comb, always_latch, always_ff ■ Continuous assignments to nodes other than nets, and procedural assignments to nodes other than reg ■ Enumeration methods First, Last, Next(n), Prev(n), Num, and Name ■ Assignment operators +=, -=, *=, /=, %=, &=, |=, ^=, <<=, >>=, <<<=, and >>>= ■ Increment ++ and decrement -- ■ Jump statements return, break, and continue ■ Enhanced for loop (declare loop variables inside initial condition) ■ Do-while loop and local loop constructs ■ Assignment patterns ■ Keywords unique and priority in case statements ■ Default values for function/task arguments ■ Closing labels ■ Extensions to directives ‘define and ‘include ■ Expression size system function $bits ■ Array query system functions $dimensions, $unpacked_dimensions, $left, $right, $high, $low, $increment, and $size ■ Packed array (include multidimensional packed array) ■ Unpacked array (include single-valued range dimension) ■ Implicit port connections with .name and .* Quartus II integrated synthesis also parses, but otherwise ignores the SystemVerilog assertions. -

В модуле tst2 нарушена приоритетность операций. Сначала присвоили, что хотели, а потом, при условии, сбрасывам. А в tst1 все законно - если надо сбросили, а потом уже, когда не надо сбрасывать, присвоили. Программируя на C, выполняя операторы последовательно, такое допустимо. А в "железном" триггере реализовать загрузку и одновременно с этим сброс невозможно. И не только сброс. У триггера в ПЛИС еще есть установка, разрешение тактов, синхронные установка и сброс и т.п. Нужно использовать с учетом их приоритетов.

-

255 или 256?

ViKo ответил lun тема в В помощь начинающему

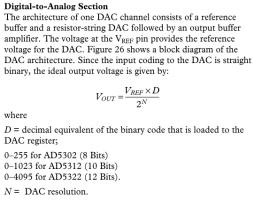

Почему это? Что мешает? На ЦАП код 11111111 можно подать? И в ЦАП обычно выходное напряжение не дотягивает до опорного на единичку младшего разряда. А всех уровней будет 2^N. -

Отладочная плата STM32VLDISCOVERY

ViKo ответил Twen тема в ARM, 32bit

В startup.s есть строчка DCD Reset_Handler ; Reset Handler Вот оттуда и стартует. В форуме это обсуждалось.