-

Постов

12 216 -

Зарегистрирован

Весь контент ViKo

-

В главе 7. Агрегатные типы данных. Там и картинки есть. Только вникать сложнее.

-

В стандарте не смотрел, но по моим представлениям должно получиться: byte0-bit7,... byte0-bit0, byte1-bit7, ... byte1-bit0, ... ... byte3-bit0 Mожно посмотреть в книжке "SystemVerilog for Design". Только вряд ли это называется "приведение типов".

-

Как здесь уже говорили, неплохо бы ввести рейтинг для модераторов, по параметрам: - оценка профессионального уровня - оценка личностных качеств - оценка занятости модераторством Даже лучше закрытый, чтобы результаты голосования не были видны участникам. А администрация и модераторы делали соответствующие выводы. Уверен, что после введения рейтинга качество работы модераторов стало бы лучше. Знаю, этого не будет. Большинство предложений уходят в небытиё. А уж такое... "Кто ж будет предоставлять возможность свидетельствовать против себя?" "Да, слава богу, демократии ... конец" (с) В гостях у генерала. Ю. Шевчук. Давайте сразу весь раздел целиком.

-

Я - инженер. Я привык докапываться до истинных причин явлений. А еще "досадно мне, когда невинных бьют". upd. Вообще-то, я говорю о наказании за жалобу, а не о том, что было в той теме. Ферштейн? Это каким же? По-моему - наоборот. Каждое наказание должно основываться на фактах, доказывающих вину. Даже если эти факты и неэтичные. Осуждение идет по определенной статье. В данном случае я не увидел, какие пунты нарушил виновный. Только это меня и останавливает от дальнейшей дискусии. P.S. если я сгину в застенках Электроникса, считайте меня правозащитником. :)

-

В дополнение к разговору о битах, выкладываю свои макрофункции конфигурирования портов STM32 - модификации конфигурации одиночного бита, и записи конфигурации младшего или старшего байта порта целиком. По-моему, простенько (и красиво)... /* Port bit configuration table */ typedef enum { IN_ANALG, GPO_PP10, GPO_PP02, GPO_PP50, // Input Analog, GP Output Push-pull 10-2-50MHz IN_FLOAT, GPO_OD10, GPO_OD02, GPO_OD50, // Input Float, GP Output Open-drain 10-2-50MHz IN_PD_PU, AFO_PP10, AFO_PP02, AFO_PP50, // Input Pull-down/Pull-up, Alt Func Push-pull CFG_None, AFO_OD10, AFO_OD02, AFO_OD50 // none(illegal), Alt Func Open-drain 10-2-50MHz } CFG_MODE; /*! ******************************************************************************* * @brief Port Low/High byte configuration * @details Конфигурация байтов порта целиком * @param PORT - имя порта (A..G) * @param CM15..CM00 - конфигурация битов 15..0 * @return нет * @note Используется перечисляемый тип CFG_MODE * @note Для IN_PD_PU нужный pull-down, pull-up задается в ODR *******************************************************************************/ #define GPIO_PORTL_CFG(PORT,CM07,CM06,CM05,CM04,CM03,CM02,CM01,CM00) \ GPIO##PORT->CRL = (CM07<<28|CM06<<24|CM05<<20|CM04<<16|CM03<<12|CM02<<8|CM01<<4|CM00) #define GPIO_PORTH_CFG(PORT,CM15,CM14,CM13,CM12,CM11,CM10,CM09,CM08) \ GPIO##PORT->CRH = (CM15<<28|CM14<<24|CM13<<20|CM12<<16|CM11<<12|CM10<<8|CM09<<4|CM08) /*! ******************************************************************************* * @brief Bit of Low/High byte Port configuration * @details Конфигурация одиночного бита порта * @param PORT - имя порта (A..G) * @param BIT - номер бита (0..15) * @param CM - конфигурация бита * @return нет * @note Используется перечисляемый тип CFG_MODE * @note Для IN_PD_PU нужный pull-down, pull-up задается в ODR *******************************************************************************/ #define GPIO_LBIT_CFG(PORT,BIT,CM) \ GPIO##PORT->CRL = GPIO##PORT->CRL & (~(0xf<<BIT*4)) | (CM<<BIT*4) #define GPIO_HBIT_CFG(PORT,BIT,CM) \ GPIO##PORT->CRH = GPIO##PORT->CRH & (~(0xf<<(BIT-8)*4)) | (CM<<(BIT-8)*4) Добавлю пример использования GPIO_LBIT_CFG(A,0,IN_FLOAT); GPIO_HBIT_CFG(A,8,AFO_PP50); GPIO_PORTL_CFG(B,IN_PD_PU,IN_PD_PU,IN_PD_PU,IN_PD_PU,IN_PD_PU,IN_PD_PU,IN_PD_PU,IN_PD_PU); GPIO_PORTH_CFG(B,GPO_PP10,GPO_PP10,GPO_PP10,GPO_PP10,GPO_PP10,GPO_PP10,GPO_PP10,GPO_PP10);

-

Но ведь и "прокурор" не привел обличительных фактов. И не желает. Мое частное мнение - Когда у меня спрашивают "Откуда вы берете такие цифры?", для меня это звучит как издевка. (Да и цифры, похоже, были близкие - проценты какие-то.) Ну, я не кричу с тремя восклицательными знаками. А ждать пришлось довольно долго, однако.

-

Считаю, что Валентиныч получил "дополнительный отпуск" ни за что! Не вижу в его жалобе ни одного повода для наказания. Что там в теме было, уже не узнаю. Да и не хочу. А что в данной теме творится, видно невооруженным взглядом. Особо умиляет "Не высказывайтесь, потому что топикстартер не может ничего сказать (потому как мы залепили ему рот скотчем, забыли добавить)".

-

Иду. ...Пока Tanya пишет черным... :)

-

Мне не понятны ваши слова. В чем вы видите флуд? Так он открыт, оффтопик? Мне показалось, здесь было сказано, что закрыли? Да и тихо там что-то... Укажите место, где ТС получил "повышение". А по поводу расплывчатости правил скажете что-нибудь? Это как раз по теме.

-

Это смотря каким осциллографом смотреть. От полосы частот осциллографа зависит.

-

Цифровая "синусойда"

ViKo ответил Djony1987 тема в Языки проектирования на ПЛИС (FPGA)

Не вижу в программе Leka синуса. Расскажите, как эта программа работает. А, что-то типа радиуса окружности вычисляете? P.S. имел в виду "в последней программе, проверочной" -

Пункт правил ТС публиковать не обязан. А модератор должен. Пожалуйста, придерживайтесь правил, господа модераторы! Или понятие "имеют право..." следует расценивать, как "могут, если захотят"? Тогда это плохие правила. Расплывчатые. Здесь, все-таки, собрались представители точных наук. Давайте быть конкретными во всем. P.S. "Шо ж вы ботик потопили!?" В смысле, "Общение". Как обычно, по-тихому... Только отсюда и узнал.

-

Возможно, были отражения в линии, звенели фронты и срезы. Т.е., на срезе был и фронт. Часто осциллографы начинают "ловить и срез, и фронт". Наверное, по этой причине.

-

Синхронизатор

ViKo ответил AlphaMil тема в Работаем с ПЛИС, области применения, выбор

Присмотрелся внимательнее к рисунку. Да, есть в нем смысл. Был неправ. 1. Короткие импульсы 1 на Data захватываются защелкой, затем триггер фиксирует это состояние. И находится в нем долго, до следующего импульса на Data. По этому импульсу защелкивается 0, и дальше триггер... Таким образом, состояние триггера по каждому импульсу на Data изменяется на противоположное. Стоящий после него синхронизатор с исключающим или на конце вылавливает каждое изменение приходящего "желтого" триггера сигнала, формируя импульс в один свой такт по фронту, и по срезу. Так "восстанавливается" удвоенная частота импульсов Data. 2. Если на Data импульс достаточно длительный, так, что в него попадает один фронт Clock1, или в короткий импульс попал фронт Clock1, "желтый" триггер сформирует импульс в один такт. Который может не словиться "синими" триггерами. А если словится, сформируются два подряд идущих импульса. Нехорошо. 3. Если на Data импулься длинный, "желтый" триггер будет генерировать то 0, то 1. Аналогичный сигнал появится на выходе синхронизатора. Тоже не хорошо. Особо нужно посмотреть, когда импульс на Data равен периоду Clock1. В этом случае выход триггера переключается одновременно со срезом Data. Вот она - потенциальная возможность для метастабильного состояния защелки-мультиплексора. Если защелкнется новое состояние триггера - сформируется одиночный импульс (вариант 2). Если сохранится старое - все нормально (вариант 1). Но, так как при "защелкивании" сигнал с триггера проходит по мультиплексору дважды, сначала по цепи для входа 1, потом по цепи для входа 0, то он гарантированно "защелкнет" старое состояние триггера. Триггер начнет формировать длинный импульс (вариант 1). Примерно так. :) -

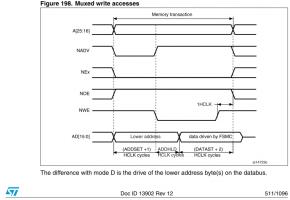

На вашей картинке работает чуть иначе: R/W выбирает, читать или писать. А по /CS происходит сам процесс. И ALE положительный, как часто встречается. Но данные с записью совпадают, это да. На моей картинке ссылаются на режим D, а там все так, как я описал. Да и в остальных режимах похоже. Есть режимы с длинным /WR, так там /WAIT задействован. Для адреса там любая защелка сгодится, адрес-то долго тянется. Только на декодирование времени меньше будет, если по фронту NADV заносить. Меня данные беспокоят. Прозрачная защелка схватит вместо данных адрес вначале. А использовать буду, что изобрету сам. Я в ПЛИС такую шину хочу завести.

-

Прикладываю картинку из мануала, для режима Muxed NOR FLASH. По-моему, сигнал NWE должен спадать одновременно с появлением data driven by FSMC. Иначе начнет свой же адрес записывать. Кому это надо? Написал в саппорт, как смог. Пока молчат.

-

Синхронизатор

ViKo ответил AlphaMil тема в Работаем с ПЛИС, области применения, выбор

Импульс может и должен быть равен такту. Но даже если он и короче, то он уже отловлен триггером. Зачем его держать? Разве что чтобы выдержать время удержания на входе D? А если не отловлен - туда ему и дорога! :) не думаю -

Синхронизатор

ViKo ответил AlphaMil тема в Работаем с ПЛИС, области применения, выбор

Хочу вернуться к рис.8 (см. сообщение №58). Возник у меня вопрос о целесообразности мультиплексора в "желтой" части схемы. И подумал я, почему его не заменить на схему И - один вход - Data, другой /Q с триггера. Что делает мультиплексор в "желтой" части. Пока на Data 0, это латч, поддерживающий свой 0. Незнамо, зачем. Пришла "длинная" 1, мультиплексор переключился на вход 1, передает 1 с инверсного выхода триггера на вход D триггера. По такту Clock1 эта 1 записалась в регистр. На инверсном выходе триггера появился 0, и этот 0 пришел через мультиплексор на D. Пришел следующий такт, в триггер записался 0, на входе мультиплексора 1. И т.д., генерация. Когда Data стала 0, мультиплексор запомнил свое последнее состояние. И триггер записал его, и выдал наружу. Аналогично ведет себя схема на И. С той разницей, что принудительно подаст 0 на вход D, когда Data станет 0. И выход триггера гарантированно переключится в 0. При "короткой" 1 на Data, однотактовой, обе схемы работают одинаково. "Развод" какой-то!? :) -

нет выхода :( Можете на 120MHz Cortex, будет быстрее, как понимаете, раза в 1.5 - 2. Еще шину замените на 16-битовую, читайте за один раз два байта.

-

Наверное, дело не в GPIO, а в архитектуре и системе команд ARM. Напрямую ни к чему во всем громадном адресном пространстве не обратиться, все посредством косвенной адресации через регистры. Сначала загрузить адрес, потом по этому адресу прочитать, потом что-нибудь сделать, потом записать обратно. И так со всеми переменными, кроме локальных, которые удастся поместить в регистры.

-

У меня был... я сгенерировал... http://electronix.ru/forum/index.php?showt...st&p=913156 можем прикинуть... раз 500000 в секунду словить можно рассчитывать. Процессор, правда, другой, но вряд ли на большее стоит надеяться.

-

Не уверен, что эта область была стерта. Но, поскольку вы этим загрузчиком не пользовались, то он вам и не нужен. Настройки проекта проверьте все.

-

Я предлагал rbf-файл подключить с помощью include в виде массива, полученного с помощью WinHex. В отдельном файле массив на 30kB выглядит вполне прилично. Точнее, совсем не "выглядит", не путается под мышкой (каламбурчик). :) Именно так я поступил с файлом шрифта на 50kB, например.

-

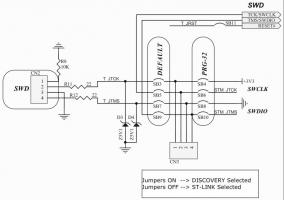

Вот часть схемы STM32VLDISCOVERY, можно найти на сайте ST, в одном из pdf. 1 - VT 2 - SWCLK 3 - GND 4 - SWDIO От первой ноги - никакого толку. Я ее не заводил. Обошелся тремя оставшимися.

-

Notepad++