Perdaculus

Участник-

Постов

45 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Perdaculus

-

Звание

Участник

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

Чтобы не плодить новых тем, напишу тут. Кто-нибудь знает почему CMU PLL в Arria 10 в Quartus 18.1 не даёт сгенерировать выходную частоту 1250 МГц? (пишет валидное значения 2450-5200). Просто странно получается, что я TSE затактировать с помощью CMU PLL не могу, поскольку он требует на порт tx_serial_clk именно 1250 МГц. FPLL и ATX использовать не хочу, поскольку их всего по две на банк.

-

Как я понял, quartus prime pro поддерживает только 10 серии ПЛИС. Выходит, что помимо ПО надо ещё и платы обновить)

- 10 ответов

-

- systemverilog

- interface

-

(и ещё 1 )

C тегом:

-

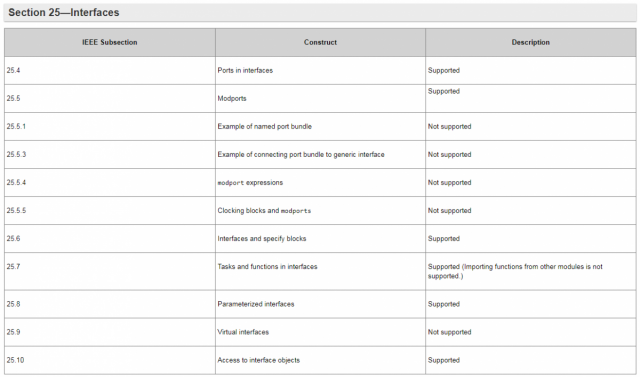

Эхх.. В очередной раз убеждаюсь, что половина инструментов systemverilog не имеет смысла, если работаешь в Quartus. Не понимаю, что они ежегодно там обновляют. На днях пытался работать с массивами интерфейсов и оказалось, что размерность массива можно задавать только явно числом. Если попытаться задать размерность массива интерфейсов с помощью функции (я так часто делаю для задания размерности портов в объявлении портов модуля), то вылезает ошибка.

- 10 ответов

-

- systemverilog

- interface

-

(и ещё 1 )

C тегом:

-

- 10 ответов

-

- systemverilog

- interface

-

(и ещё 1 )

C тегом:

-

А в чем нарушение? Я нашел в IEEE Std 1800-2017 в разделе 25.10 Access to interface objects такой способ: interface ebus_i; integer I; // reference to I not allowed through modport mp typedef enum {Y,N} choice; choice Q; localparam True = 1; modport mp(input Q); endinterface module Top (); ebus_i ebus (); sub s1 (ebus.mp); endmodule module sub ( interface.mp i ); typedef i.choice yes_no;// import type from interface yes_no P; assign P = i.Q; // refer to Q with a port reference initial Top.ebus.Q = i.True;// refer to Q with a hierarchical reference initial Top.ebus.I = 0;// referring to i.I would not be legal because is not in modport mp endmodule Тем не менее вложенный модуль понимает, что это структура, поскольку распознает её поля

- 10 ответов

-

- systemverilog

- interface

-

(и ещё 1 )

C тегом:

-

Импорт типа данных из интерфейса

Perdaculus опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем привет. Пытаюсь передать параметризированную структуру между модулями и поскольку "parameter type" в Quartus 18.1 не работает, я хочу сделать это через интерфейс. Описываю его в отдельном файле, создаю инстанс в топ модуле, а во вложенном модуле пытаюсь вытащить из него тип данных. Выглядит это так: interface intf_WITHSTRUCT #(WIDTH=8); typedef struct packed{ logic val; logic [WIDTH-1:0] cnt; } st_INSIDE_INTF; st_INSIDE_INTF struct_inst; endinterface: intf_WITHSTRUCT module top (output logic [7:0] ocnt); intf_WITHSTRUCT #(.WIDTH(8)) interface_inst(); test i_test ( .clk(clk_125MHz), .rst(prb_rst), .blabla(interface_inst), .ocnt(ocnt) ); endmodule: top module test ( input clk, input rst, intf_WITHSTRUCT blabla, output logic [7:0] ocnt ); typedef blabla.st_INSIDE_INTF st_INSIDE_INTF_import; // Вытаскивю структуру st_INSIDE_INTF_import new_struct_inst; // Создаю инстанс always_ff@(posedge clk or posedge rst) if(rst) new_struct_inst <= '0; else new_struct_inst.cnt <= new_struct_inst.cnt + 1'b1; always_ff@(posedge clk or posedge rst) if(rst) ocnt <= '0; else ocnt <= new_struct_inst.cnt; endmodule: test В результате получаю ошибку: Error (10733): Verilog HDL error at test.sv(17): cnt is not declared under this prefix В чем может быть ошибка? Что странное, если во вложенном модуле я присваиваю структуре (которая в интерфейсе) значения, то ошибки не возникает. На мой взгляд не логичное поведение- 10 ответов

-

- systemverilog

- interface

-

(и ещё 1 )

C тегом:

-

Да, клоки одинаковые. Идут с одной PLL, согласно мануалу. По поводу синхроконстант. Как я понял, их стоит подавать, когда Native или Custom PHY используешь, поскольку они там явно задаются в настройках и в мануале этот процесс описывается. Здесь же ни в настройках, ни в мануале я упоминания об этом не встретил, поэтому сделал по аналогии с обычной 10GBASE-R -- ничего не стал предварительно подавать. В ней без них все функционирует. Обычно так и происходит, у каждой PHY -- свой mif в папке появляется. И реконфигурацию нужно делать, чтобы сменить clk например. Но с этой дурацкой мегафункцией, все немного иначе. Поскольку у нее разные режимы работы AN/LT/10G PCS FEC/1G PCS, то требуются несколько разных mif файлов, которые (согласно описанию в example) надо генерировать через другие мегафункции. Какие в трансивере настройки изначально, т.е. после прошивки и до реконфигурации - я так и не понял. Поскольку я хотел изначально запустить хотя бы просто 10G PCS с FEC, я получил mif файл мегафункции Low Latency PHY с соответствующими настройками (в example берут настройки трансивера для режима 10G с FEC именно от этой IP). Затем, я опять же согласно мануалу в example поправил полученный mif файл - отредактировал строки отвечающие за реконфигурацию PMA. Добавил все это дело в ROM, и попытался с помощью Jtag2Avalon Bridge через systemconsole записать этот mif. Запись вроде прошла, но каша все равно осталась.) Хотел проверить статусы реконфигуратора, но по каким-то причинам команда master_read_32 в system console зависает и не выдает результат.. Короче, тут столько махинаций, что я по сути мог накосячить на любом этапе. Спасибо за отклик

-

А зачем его тогда цеплять? Если реконфигурация не нужна. Или вы реконфигурируете без mif? Примерно так:

-

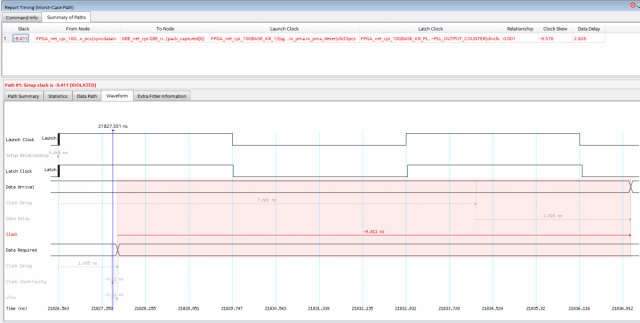

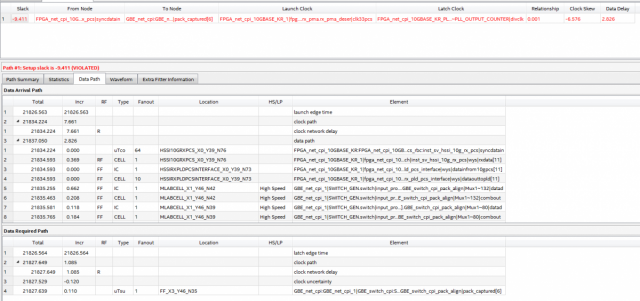

Короче, что я только не делал, чтобы избавиться от слаков. Менял типы PLL трансиверов, менял режимы работы PLL генерирующей xgmii_rx_clk, понижал референс clk, пытался вместо референсного клока использовать восстановленный, пытался задавать мультициклы, менять фазу, включать выключать AN/LT и т.д и т.п. В итоге нашел example для 10GBASE-KR (прикрепил) для древнего Quartus 13.1. И вот там в главном sdc файле, clk33pcs и клок c PLL (который питает xgmii_rx_clk) добавлены в отдельные асинхронные группы=) То есть они просто не анализируются. Это крайне странно, поскольку, если это было правильно, такой констрейн был бы прописан в .sdc самой мегафункции. Короче, сделал также, естественно все слаки ушли, но каша на приеме осталась. Начал перечитывать мануал, и у меня возникла мысль, что данная мегафункция (даже без опции AN и LT) может работать только в паре с Reconfiguration controller. То есть если у меня даже простая конфигурация 10G с FEC, нужно городить огород и загружать .mif файлы. Если я хочу еще и Link Training, то мне нужно генерировать еще один .mif файл и каким то образом между ними переключаться. Я могу понять зачем такая штука, когда есть и 10G с FEC и Link Training в проекте, но не понимаю зачем это все, если я хочу просто допустим 10G с FEC. Зачем в данном случае реконфигурация? Плюс, конечно, возникает вопрос как генерировать эти mif в свежих Quartus. В example для этого даны исходные файлы, которые в megawizard открываешь, редактируешь, компилируешь, пляшешь и получаешь mif. Но в свежих они некорректно открываются. 1G_10GbE_DE_Quartus_v13.1.zip

-

Хотелось бы иметь мегафункцию, которая дала бы чисто soft PCS. Тогда можно было бы поэкспериментировать и замутить свой FEC например. Но я не нашел как отдельно это сделать. Поэтому сижу по уши в слаках..

-

в -R аппаратный, в native и custom по-умолчанию тоже аппаратный, возможно, можно какую то галку поставить при настройке, но я такого не видел. Вообще, если открыть 10GBASE-KR, то там будет видно, что он основан на Native и окружен кучей дополнительных модулей, в том числе там есть модули с названиями типа soft pcs. Они, кстати закодированы, что неудивительно в принципе). Поэтому я думаю, что Native soft сделать не может сам по себе.

-

Если FEC включаешь, то становится софтовым, как я понял, поскольку FEC между PMA и PCS должен быть. Поэтому относительно большой объем ресурсов требует эта PHY в такой конфигурации

-

Странно на самом деле. Я не обратил на это внимание. Вероятно это связано с тем, что частоты разные источники имеют. Вопрос насколько это критично

-

Да ...|rx_pmas[0].rx_pma.rx_pma_deser|clk33pcs Generated 6.369 156.25 MHz ...|general[0].gpll~PLL_OUTPUT_COUNTER|divclk Generated 6.397 156.25 MHz Вот один из нескольких слаков: Вот его datapath: В целом, иcпользуется всего 13% логики, сам проект без слаков стабильно работал с простой 10GBASE-R PHY. Здесь либо потому что PCS переехало в soft появились слаки и нужно что то с констрейнами придумывать, либо я что то не так все таки подключаю...

-

Спасибо. Странный подход у altera, делают клевый блок с помехоустойчивым кодированием, с автоматическим обменом коэффициентами эквалайзера между PHY. А толковую схему и описание добавить не могут. Информацию приходится по крупинкам собирать. На example вообще забили