Поиск

Показаны результаты для тегов 'lvds'.

-

SoM FET113i-S разработан и спроектирован на базе промышленного процессора Allwinner T113-i с основной частотой 1,2 ГГц. Он оснащен многоядерным процессором и многоархитектурой: интегрированным двухъядерным процессором Cortex-A7, 64-разрядным процессором XuanTie C906RISC-VCPU и DSP, который не только обеспечивает эффективную вычислительную мощность, но также имеет богатые мультимедийные функции и полные ресурсы интерфейса; Конструкция штампованного отверстия делает продукт более долговечным, а макетная плата потребляет как можно больше ресурсов ядра процессора, что является экономически эффективным выбором для таких ключевых областей, как промышленность, энергетика, транспорт и так далее! В этой статье кратко описан процесс адаптации платы разработки Forlinx T113i-S к экрану LVDS. Платформа разработки: плата разработки Forlinx T113i-S. Чтобы изменить экран T113i, вам необходимо изменить ядро и uboot соответственно. В качестве примера возьмем экран LVDS 1024*600. 1. Введите следующий путь; 2. Откройте OK113I-C-Linux.dts; 3. Измените параметры разрешения, как показано на рисунке ниже (конкретные параметры см. в руководстве к экрану, который вы используете): 4. Сохраните и выйдите после изменения, а затем начните изменять uboot и введите следующий путь; 5. Откройте display-menu.c; 6. Измените параметры разрешения, как показано на рисунке ниже: 7. После модификации скомпилируйте uboot по начальному пути исходного кода; 8. Завершите компиляцию после успешной компиляции./build. Ш.; 9. После успешного выполнения. /build.sh, образ пакета записан на плату, чтобы наблюдать за этим явлением. Вышеупомянутая модификация параметров может быть успешно адаптирована к новому дисплею, конечно, конкретная работа разных плат главной платформы управления будет разной, но общая идея та же самая, конкретная может быть основана на соответствующей платформе для просмотра соответствующей информации. определить конкретные шаги.

-

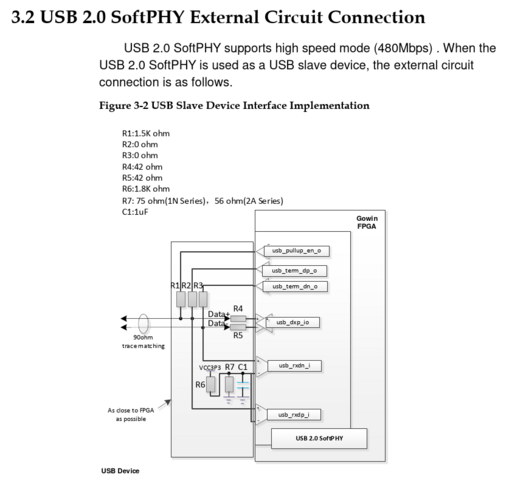

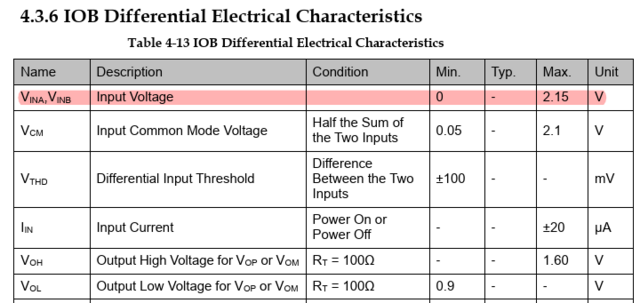

Доброго времени суток, уважаемые участники, Набрёл на IP Core Gowin USB 2.0 SoftPHY, которое позволяет (на первый взгляд) реализовать подключение шины USB 2.0 напрямую к ПЛИС Gowin (без использования специальных трансиверов): На первый взгляд ничего страшного, но далее следует указание настроек пинов ввода-вывода ПЛИС: usb_rxdn_i: IO_TYPE=LVDS25 PULL_MODE=NONE; usb_rxdp_i: IO_TYPE=LVDS25 PULL_MODE=NONE. При этом в даташите для дифференциальных входов определено максимально допустимое входное напряжение не более 2,15 В: При этом, нужно понимать, что для USB 2.0 Full-speed уровни на входе могут быть до 3,3 В включительно. Отсюда вопрос: как Gowin представляет себе надежную работу этого Soft PHY, если они выходят за заданные ими же допустимые пределы? Попутно возникает ещё один вопрос, касающийся двунаправленных пинов usb_dxp_io со стандартом "IO_TYPE= LVCMOS33D", которые внутри используют буферы типа ELVDS_IOBUF (Emulated LVDS). Является ли входной буфер Emulated LVDS дифференциальным приёмником сигнала, т.е. может ли он подавлять синфазную помеху на входах? У меня не было практики работы с подобными буферами, т.к. у Xilinx нет такого варианта настройки входных буферов. Однако у тех же Intel и Lattice вроде бы есть аналогичные входные буферы - есть ли у кого-нибудь опыт их применения и понимание, на сколько эффективно они работают с синфазными входными помехами?

-

Выравнивание длинн проводников для углового разъема DVI

mitro опубликовал тема в Схемотехника

Добрый вечер! Понадобилось сделать плату - переходник от FPGA Development board (разъем IDC-40) на DVI. Предполагается передавать данные lvds-ом, 4 дифференициальных бита данных, один дифференциальный такт. Хотел при разводке выравнять длины проводников. Но у меня вопрос - а что делать с угловым разъемом DVI? Таким, как на рисунке. У него же, наверное, разная длина проводника от пина до разъема для разных рядов? Как это учитывать? Где найти эту информацию (длины для разных рядов?). Или он так сделан, что длины одинаковые???- 13 ответов

-

Analog Devices предлагает лучшую в своем классе запатентованную технологию цифровой изоляции данных iCoupler, мощные изолированные преобразователи напряжения, протоколы связи, от RS-485 (ADM2795E), USB (ADuM4160) и CAN (ADM3050E) до гигабитного LVDS (ADN4654), изолированные драйверы для IGBT и SiC (ADuM4122), переключатели и изолированные сигма-дельта-АЦП, модуляторы и усилители. Подробнее о технологии iCoupler в цифровой изоляции Analog Devices>>

-

- analog devices

- icoupler

- (и ещё 5 )

-

Настройка LVDS на Cyclone V

Петр Юркевич опубликовал тема в Программирование

Здравствуйте! Стоит задача генерировать внутри ПЛИС Altera Cyclone V (кит Terasic DE1-SoC) при помощи PLL некоторую частоту, передавать её на выход LVDS и принимать на другой вход этой же ПЛИС (необходимо для отладки частотомера). По поводу LVDS долго пытался вчитываться в Cyclone V Handbook, но понял только то, что надо использовать функции Квартуса для приёма и передачи сигнала LVDS. Насколько я понял, при назначении в Pin Planner стандарта LVDS Квартус сам назначает пару выбранному пину. Информацию по поводу пар дифференциальных пинов нигде не смог найти. Я выбрал GPIO[12] и GPIO[14] (парные 15 и 13). Дальше создал входной и выходной буферы (ALTIOBUF), которые должны преобразовывать сигнал из моно в дифференциальный и обратно. LVDS_BUF_IN lvds_in ( .datain(GPIO[15]), .datain_b(GPIO[12]), .dataout(clk_in) ); LVDS_BUF_OUT lvds_out ( .datain(clk_0_2), .dataout_b(GPIO[13]), .dataout(GPIO[14]) ); По поводу выходной пары у Квартуса вопросов не возникло, а на входные пины вылезла ошибка: Error (169008): Can't turn on open-drain option for differential I/O pin GPIO[12]. И аналогичная на 15-й пин. Если не создавать буфер, на выходную пару вылезает такая же ошибка, я читал, что Квартус не пропускает неправильно настроенные пины LVDS. Я знаю, что в LVDS должен быть на входе резистор между линиями. Может быть, ошибка из-за его отсутствия в программе? И его как-то настроить надо в самой ПЛИС? -

busLVDS на cyclone 10 LP

OslikIA опубликовал тема в Работаем с ПЛИС, области применения, выбор

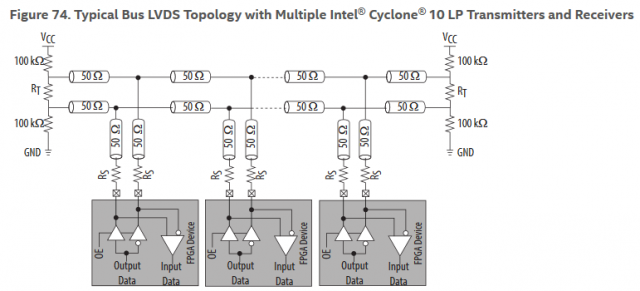

Здравствуйте, господа и товарищи. Вопрос на границе схемотехники и Quartus. Пытаюсь реализовать LVDS с переключением направления линии прием/передача между двумя Cyclone10LP. Решил сделать это как частный случай bus-LVDS. Схемотехника по рекомендации Intel на рисунке, у меня проще - около каждого Rt стоит приемопередатчик. К каждому из дифф.выводов последовательно 50 Ohm, далее Rt=100 Ohm, и в линию кабеля USB 3.1. Выводы настроены в PinPlanner на стандарт busLVDS, питание банка 2.5 V. При выводе сигнала уровень дифференциального напряжения ~0.6V (если точнее, сверху вниз: Vcc=2.5; pin1=2.1; Rt(up)=1.6; Rt(down)=1.0; pin0=0.3; gnd=0) Собственно, вопросы: 1. Не великоват ли дифф. уровень (вроде д.б. 350mV) 2. Видел ли кто описание от Intel, где было бы понятно - они в busLVDS работают с ноги источником тока или источником напряжения? и параметры. Я что-то не смог найти. 3. Если предположить, что работают источником напряжения (а пока кажется, что так), то надо ли увеличить последовательные резисторы для получения дифф. напряжения 350mV ?. 4. Возможно, я что-то не доделал в настройках или схемотехнике, и поэтому ноги передатчика ведут себя не так, как д.б. ? С уважением, Иван.- 1 ответ

-

- lvds

- cyclone 10 lp

-

(и ещё 1 )

C тегом:

-

Есть необходимость создания проекта под Artix в Vivado: АЦП -> ФНЧ -> ЦАП Цель - на простом проекте отработать навыки работы с констрейнами в Vivado. Вводные: АЦП - выходы LVDS, тактовая данных (64МГц) - тактируют плис ФНЧ - КИХ на частоте 384 МГц ЦАП - КМОП 32 МГц Пока пытаюсь сделать упрощённый вариант - генерировать синус на ЦАП по 16 точкам. Вопрос 1 У меня есть ноги CLK64_P и CLK64_N, из них я создаю клок CLK64 методом: Удивлён, что констрейн на клок приходится задавать для CLK64_P а не для CLK64, это правильно? #create_clock -add -name sys_clk_pin -period 15.625 -waveform {0 7.8125} [get_ports { CLK64_P }]; сколько цифр после точки можно вводить? Vivado понимает 7.8125 или округлит до 7.81? Вопрос 2 Мне нужны частоты 384МГц и 32МГц, 384МГц получаю так: Мне надо прописывать констрейн на клок CLK384 или Vivado сам поймёт что он и всё что от него тактируется работает на частоте 384МГц? Вопрос 3 Как лучше получить частоту 32 МГц - своим счётчиком или с PLL? Вопрос 4 Счётчики в Vivado оптимизируются? В ISE я брал 32 разрядный регистр, делел на нём 3 разрядный счётчик и при синтезе у меня старшие разряды отбрасывались и получался 3 разрядный счётчик в Vivado я что-то этого не замечаю, он что пытается развести 32 разряда? Вопрос 5 Как передавать данные между блоками работающими на частотах 64, 384, 32 МГц - напрямую или ставить регистры типа FIFO для надёжности? Вопрос 6 Хочется сделать выходные и входные триггеры и разместить их рядом с ножками - как это описать в констрейнах и как задать время запаздывания/распространения? Вопрос 7 Файл .xdc - один на проект или можно создать некую иерархию из .xdc файлов? констрейны только в .xdc? В верилоге сразу указать нельзя?

-

LVDS данные с КМОП-матрицы

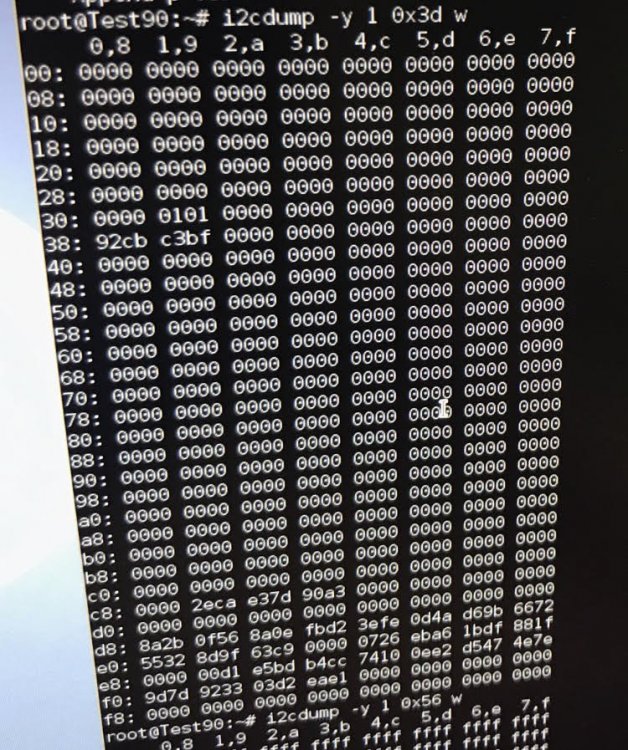

Klayton опубликовал тема в от ТТЛ до LVDS здесь

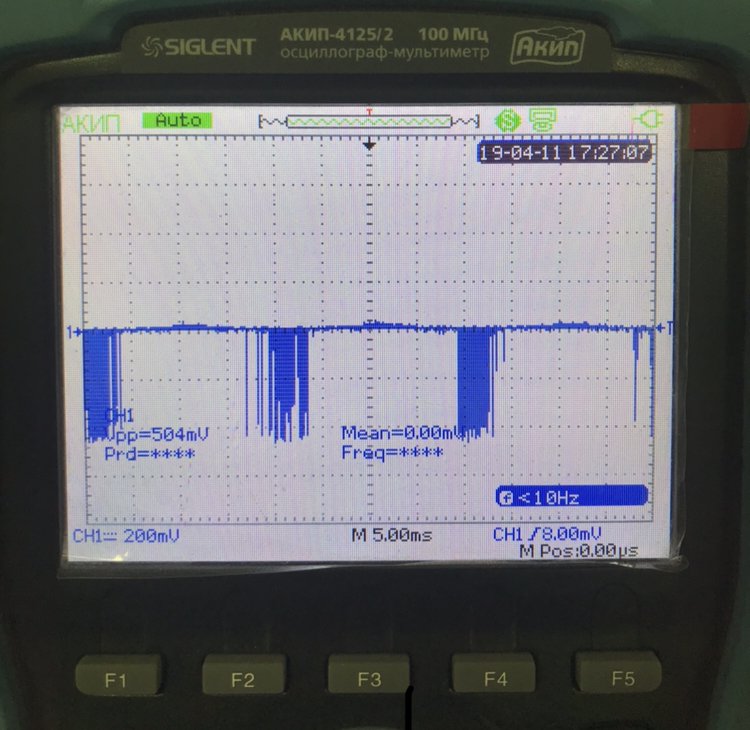

Всем привет! Имеется отладочная плата с сенсором MT9v124. При подаче питания на выходе LVDS следующий непонятный сигнал (см. Прикрепленные) . Сигнал снимался с линий LVDS относительно друг друга. Причем переключение на плате джмапера Standby mode никаких изменений не вызывает. Ток потребления 10 мА (который по всей видимости потребляет только кварц, потому что при его отключении ток падает до 0). Возможно требуется прописать в регистр матрицы какую-то команду через I2C, чтоб она "завелась"? Описание регистров (удобнее всего смотреть в браузере internet explore) и считанные данные с регистров матрицы на плате тоже прикрепляю. MT9V124-REV2.xsdat EVBUM2468-D.PDF MT9V124-D-1101616.pdf -

Video Interfaces

GenaSPB опубликовал тема в Форумы по интерфейсам

Делаю плату для подключения дисплея к процессору с RGB интерфейсом (протащить RGB сквозь последоватльный канал - и вомоэно использовать готовые дисплеи с последовательным интерфейсом). Не могу понять, что является "истинным" LVDS, на что заточены процессоры со встроенным интерфейсом и продающиеся 7" панели. Глядя на плату от стартер кит http://starterkit.ru/html/index.php?name=shop&op=view&id=64 вижу применяется SN65LVDS94 - LVDS SERDES RECEIVER Но есть с аналогичной разводкой микросхема SN75LVDS82 FlatLink™ Receiver и передатчик SN75LVDS83B FlatLink™ Transmitter. Википедия говорит что панели как раз с FlatLink интерфейсом (FlatLink by TI was the first interoperable version of FPD-Link) и есть видео... Временные диаграммы SN65LVDS94 и SN75LVDS82 отличаются фазой одного из импульсов… Еще в тему https://hackaday.com/2019/02/21/hack-a-thinkpad-display/ -

Драйвер RGB панели

Aldec опубликовал тема в Работаем с ПЛИС, области применения, выбор

Посоветуйте какие плис возможно использовать драйвером панели