Поиск

Показаны результаты для тегов 'плис'.

-

На сайте компании Xilinx размещена для скачивания версия среды разработки для ПЛИС и СнК Vivado под номером 2021.1. Подробнее

-

- vhdl

- fpga xilinx

-

(и ещё 2 )

C тегом:

-

В данном вебинаре вы познакомитесь с основными особенностями нового поколения адаптивных систем Versal, с тем, какие среди них существуют вариации и в каких сферах их применение принесёт максимальную пользу. Подробнее

-

- плис

- fpga xilinx

- (и ещё 7 )

-

Xilinx Versal AI Edge Series

МакроГрупп опубликовал тема в Объявления пользователей

Versal AI Edge Series – самая масштабируемую и адаптируемая платформа для оконечных и встроенных систем от Xilinx Подробнее -

Макро Групп – официальный дистрибьютор HiTech Global, производителя плат на ПЛИС Xilinx и Intel FPGA (Altera) Подробнее

-

- плис

- fpga xilinx

-

(и ещё 4 )

C тегом:

-

Этот курс включает в себя лекции, лабораторные занятия и демонстрации, которые помогут вам оптимизировать энергетические и тепловые решения с помощью Versal ACAP. Подробнее

-

Инженеров-разработчиков и сотрудников ИТ-отделов приглашаем принять участие в техническом семинаре, посвящённом новейшим продуктам компании Xilinx. Семинар пройдёт в городе Минск 24 мая Подробнее

-

Адаптивные SoM-модули Kria от Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

Компания Xilinx анонсировала выпуск собственных адаптивных SoM-модулей (Система-на-Модуле) серии Kria. SoM модули Kria – это новый способ быстрого развёртывания производительных решений Xilinx в сфере Искусственного интеллекта (ИИ) на конечных устройствах. Подробности-

- som

- xilinx ise

- (и ещё 5 )

-

В данном вебинаре будут рассмотрены основные достоинства и недостатки использования SoM-модулей, как они могут ускорить проектирование и производство готовых устройств и как изменится процесс разработки ПО, если вы будете использовать модули в своих проектах. Также представитель компании «Рифтек» расскажет об одном из реальных проектов, в котором использовались SoM-модули компании Trenz Electronic. Подробнее

-

вебинар Вебинар Xilinx по Artix Ultrascale+

МакроГрупп опубликовал тема в Объявления пользователей

Регистрируйтесь на бесплатный вебинар Xilinx, на котором будет рассказано о недавно анонсированном расширении линейки Ultrascale+ для бюджетного сегмента широкого спектра интеллектуальных периферийных решений. Подробности -

Всем привет. Мы проводим стримы по FPGA/ПЛИС тематике на твиче по адресу twitch.tv/fpgasystems Обычно, это среда и суббота в 20:00. Записи прошедших стримов лежат на youtube: youtube.com/c/fpgasystems Ждём Вас на стриме. Анонсы предстоящих эфиров в группе в телеграм @fpgasystems (https://t.me/fpgasystems) и VK и FB

-

Компания Xilinx объявила о существенном расширении линейки своих 16 нм устройств UltraScale+ - Artix UltraScale+. Подробнее...

-

Приглашаем на информационно практический вебинар «Решения Xilinx для интеллектуального управления электроприводом». На вебинаре будут рассмотрены решения Xilinx на базе систем на кристалле (SoC) для экосистем, в которые входят различные электроприводы. Эти решения обеспечивают не только оптимальное управление одним или несколькими моторами/электроприводами, но также осуществляют управление через Интернет, сбор и обработку аналитики в облаке, обнаружение неисправностей и даже предсказание времени их наступления. Зарегистрироваться

-

Компания Xilinx приглашает вас присоединиться к бесплатному двухдневному онлайн-тренингу, организованному совместно Xilinx Customer Training и авторизованными поставщиками обучения Xilinx. Онлайн-тренинг поможет вам быстро изучить Versal™ ACAP и приступить к проектированию устройств на его основе. Подробнее

-

Xilinx T1 — новый ускоритель для архитектуры O‑RAN

МакроГрупп опубликовал тема в Объявления пользователей

Переход к новой технологии никогда не бывает простым и связан с множеством технических и политических проблем. Одной из таких проблем, как ни странно, является то, что производители предлагают законченные, вертикально интегрированные решения. Этот подход облегчает развертывание и эксплуатацию систем, но приводит к монополизму, поскольку привязывает оператора сети к конкретному поставщику, затрудняет модернизацию сети и препятствует выходу на рынок новых производителей. Подробнее... -

Компания Xilinx приглашает присоединиться к вебинару, чтобы узнать, как применять передовые сверхбыстрые методы обработки изображений Synthetic Aperture (SA) и Plane Wave (PW) в ваших устройствах. Используемая для этого платформа Xilinx Versal™ Adaptive Compute Acceleration Platform (ACAP) с гибкой и эффективной архитектурой программируемой памяти поможет решить ваши проблемы, обеспечивая высокую производительность при низком энергопотреблении. Дата и время: 24 февраля 2021 г. | 18:00 Мск Зарегистрироваться

-

Вебинар от компании PLC2 даст вам представление об основных структурах ПЛИС компании Xilinx, основываясь на реальных задачах машинного зрения и ИИ. Зарегистрироваться

-

Компания Xilinx выпустила две серийные отладочные платы на платформе Versal – VMK180 и VCK190 (до этого были доступны только платы на инженерных образцах). По всем характеристикам, кроме характеристик чипа Versal, платы идентичны. Узнать больше...

-

Компания Xilinx добавила продукт в свой портфель модулей программирования, отладки и трассировки модуль SmartLynq+. Это высокоскоростной модуль отладки и трассировки, в первую очередь ориентированный на проекты, использующие платформу Versal, который значительно улучшает процесс конфигурации и скорость трассировки. Модуль SmartLynq+ обеспечивает до 28 раз более быстрое время загрузки Linux через высокоскоростной порт отладки (HSDP), чем через кабель передачи данных SmartLynq. Для захвата трассировки модуль SmartLynq+ поддерживает скорость до 10 Гбит/с через интерфейс HSDP. Это в 100 раз быстрее, чем стандартный JTAG. Более быстрые итерации и повторяющиеся загрузки повышают продуктивность разработки и сокращают цикл проектирования. Это означает снижение времени, затраченного на отладку, вместо которой вы можете сосредоточиться на запуске своих решений на основе Versal. Узнать больше

-

Добрый день всем. Создаю один проект на больших скоростях и мне там необходимо складывать и накапливать большие значения (разрядность вектора более 50). Естественно проседает быстродействие и необходимо ввести латентность на сумматоре (хотя бы 2). На вход сумматора подаётся значения, которые изменяют по линейному закону с каким-то произвольным коэффициентом. Например входные данные могут быть 1,2,3,4,5 и т.д. А на выходе соответственно получаем 1,3,6,10,15. Схема классическая: выход сумматора падает на вход регистра, а его выход на второй вход сумматора. Регистр может инициировать любым значением перед началом работы. Классический аккумулятор! Есть варианты по добавлению второго сумматора для параллельного счета, но пока не удается засунуть его так, чтобы все работало. У кого-нибудь есть мысли, как увеличить быстродействие??

-

Ниже описана текущая задача. Мы заинтересованы не только в решении текущей задачи, но и в последующем сотрудничестве по разработке новой платформы на базе покупной платы ZCU104/102, а также в последующем сотрудничестве по проектированию системы обработки сигналов (Verilog, Zynq). Текущая задача Есть ранее выпускавшиеся плата BemicroCV A9 (CycloneV), соединенная совместимым разъемом с платой Cypress FX3. Есть проект ПЛИС и прошивка FX3 для пересылки данных через USB в обе стороны (запись и проигрывание семплов на внешних пинах). Есть готовое приложение под Windows. Проблема Весь проект ПЛИС (CPU Nios для буферизации потока в DDR3 и интерфейс GPIF II с FX3) работает правильно на тактовой частоте 25 МГц. Начиная с 27МГц, возникает дублирование данных, начиная с 500МБ в разных местах. Хотя по оценке Квартуса этот проект может работать до 83Мгц. Задача При наличии всех исходников разобраться и локализовать при отладке, в какой точке происходит дублирование данных при передаче. Сделали ли бы сами, но не хватает времени и сил. Только Петербург, гибкий график. Если предложение и задачи вас заинтересовали, отправьте свое резюме на адрес [email protected] Бюджет не ограничен в пределах разумного, резюме с указанием пределов разумного будут рассмотрены с особым вниманием :)

-

Всем привет! Требуется разработчик FPGA со знанием ЦОС в беспилотные автомобили Яндекса. Группа занимается разработкой лидара - https://vc.ru/transport/97355-yandeks-razrabotal-sobstvennye-lidary-dlya-bespilotnyh-avtomobiley Ссылка на вакансию - https://yandex.ru/jobs/vacancies/dev/dev_fpga/ Яндекс хочет сделать перемещение людей более безопасным, доступным и удобным. Мы ставим перед собой масштабную цель: оказаться в числе первых в мире компаний, создавших технологию для беспилотного управления автомобилем. Чтобы воплотить это в жизнь, мы создаем команду увлеченных, умных и целеустремленных профессионалов. Для ускорения процесса обработки информации, поступающей с сенсоров, мы начали использовать FPGA и ищем в нашу команду опытного разработчика. Что нужно делать: строить математические модели обработки потока данных на языке Python; проверять модели и реализовывать их для работы в FPGA на языке SystemVerilog; поддерживать и развивать имеющиеся модули FPGA. Мы ждем, что у вас есть: умение писать под FPGA (Verilog/SystemVerilog); опыт реализации алгоритмов ЦОС (фильтрация, выделение особенностей сигнала, статистика); опыт построения и верификации математических моделей (Python). Будет плюсом: знание С/C++; опыт работы с SOC (Altera/Intel); знание инструментов HLS; опыт работы в Linux. Там есть тестовое - надо его хорошо решить. Это реальная возможность делать продукт в динамично развивающейся отрасли с высокой конкуренцией. С уважением, Иван.

-

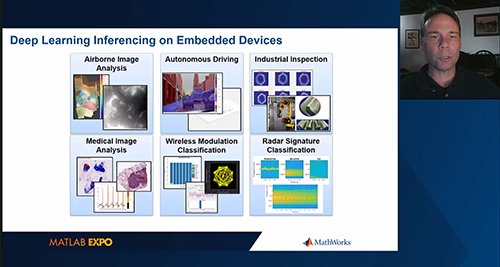

Разработка приложений для глубокого обучения, компьютерного зрения, обработки сигналов и их развертывание на ПЛИС, графических процессорах или таких платформах, как Xilinx Zynq™, NVIDIA® Jetson или ARM®, является сложной задачей из-за ограничений ресурсов, присущих встроенным устройствам. В процессе вебинара вы познакомитесь с рабочим процессом развертывания алгоритмов и приложений из MATLAB при помощи автоматической генерации кода C/C++, CUDA® или VHDL. Для разработчиков систем, стремящихся интегрировать глубокое обучение в свои приложения на базе ПЛИС, мы расскажем о проблемах и соображениях развертывания на ПЛИС, а также подробно опишем рабочий процесс в MATLAB. Мы кратко покажем, как исследовать и прототипировать обученные сети на ПЛИС с использованием предварительно собранного битового потока из MATLAB. Вы можете дополнительно настроить свою сеть в соответствии с вашими требованиями к производительности и использованию аппаратных ресурсов, создать HDL-код и интегрировать его в проект на основе FPGA. Дата проведения: 10 ноября 2020г. Время: 11:00 (МСК) РЕГИСТРАЦИЯ

-

Всем привет. Подскажите плиз, использовали ли кто-нибудь в своих проектах выделенные входы ПЛИС 5576xc4t под названием INPUT0, INPUT1, INPUT2 и INPUT4 ? И для чего они вообще? ЗЫ: если уже обсуждалось, то ткните, а то я не нашёл по форуму

-

Приглашаем специалистов, работающих с ПЛИС и системами на кристалле, на бесплатный технический вебинар «Создание кастомного контроллера в среде Vivado». При разработке систем на кристалле на платформе Xilinx не всегда удается собрать систему только из «стандартных», то есть входящих в IP-каталог модулей. В таких случаях приходится разрабатывать собственный (кастомный) контроллер. Как организовать такую разработку наиболее эффективным способом будет рассказано и показано на вебинаре на примере контроллера PWM. Программа вебинара: создание проекта с использованием стандартного шаблона структура каталогов и файлов проекта кастомизация автоматически сгенерированных файлов добавление в проект собственных исходных файлов автономная отладка контроллера с использованием эмулятора шины обеспечение совместимости для различных серий ПЛИС задание параметров для контроллера упаковка контроллера и создание кастомного IP-ядра создание собственного репозитория и размещение в нем упакованного IP-ядра кастомного контроллера подключение IP-ядра к проекту действия при модернизации контроллера демонстрация работы IP-ядра контроллера PWM Ведущий вебинара – инженер технической поддержки (FAE) по продукции Xilinx Владимир Викулин. Вебинар состоится 11 августа в 14:00 (мск). Повтор вебинара 12 августа в 10:00 (мск). Участие в вебинаре бесплатное, после предварительной регистрации. Зарегистрироваться на вебинар Компания Макро Групп является официальным партнером Xilinx в России и странах СНГ.