Поиск

Показаны результаты для тегов 'ddr3'.

-

Тополог г. Москва (high-speed PCB)

Kaola опубликовал тема в Предлагаю работу

Компания Бифорком Тек находится в поисках Инженера-тополога. Мы разрабатываем и производим телекоммуникационное оборудование, находимся в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Telegram: https://t.me/terina_ekat Также можно откликнуться на вакансию в hh.ru. Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Высшее техническое образование образование Работа в команде. Аккуратность; Нацеленность на результат, исполнительность и желание развиваться. Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики-

- топология

- маршрутизатор

- (и ещё 16 )

-

Компания Макро Групп стала официальным дистрибьютором твердотельных накопителей, модулей памяти и микросхемам памяти MMY. Подробнее

-

Компания Бифорком Тек находится в поисках тополога в свою команду RnD. Пару слов о нас. Мы существуем с 2015 года, занимаемся разработкой и производством продуктовой линейки высокотехнологичных устройств с использованием технологий SDN/IoT/4G/5G/6LoWPAN и решений в области передачи данных. Находимся в в Особой экономической зоне «Технополис «Москва» рядом с метро Текстильщики. Ссылка на наш сайт - https://b4com.tech. Если вас заинтересовала вакансия, пишите или звоните по номеру 89152033710 (Екатерина). Также можно откликнуться на вакансию в hh - https://hh.ru/vacancy/72745516. Инженер-тополог: Обязанности: Разработка ПП в Altium Designer. Формировать и оптимизировать стек МПП (стоимость — производительность) Трассировка сложных многослойных печатных плат; Подготовка GERBER (CAM) файлов для производства печатной платы; Подготовка файлов для расстановщиков (placement) и сборочных чертежей (Assembly); Взаимодействие с разработчиками и конструкторами; Участие в разработке конструкторской документации. Будет плюсом: Моделирование целостности сигналов (SI); Моделирование распределения емкостей и полигонов питания (Power); Тепловое моделирование платы; Знание цифровой, аналоговой, СВЧ схемотехники Разработка топологии сложных печатных плат, желательно с использованием «глухих» и «слепых» переходных отверстий; Требования: Опыт проектирования многослойных печатных плат для цифровых высокоскоростных устройств; Английский достаточный для чтения технической документации; Опыт работы в радиоэлектронной промышленности; Опыт трассировки печатных плат с цифровыми интерфейсами типа PCIe Gen3, DDR3/4; Понимание проблем перекрестных помех, целостности сигнала, электромагнитной совместимости; Опыт проектирования печатных плат с высокой плотностью компоновки, в том числе с применением BGA-компонентов с мелким шагом выводов; Опыт: Трассировка с выравниванием длины линий, расчетом импеданса, моделированием целостности сигнала, использованием теплоотводящих слоев; Приветствуется опыт работы с аппаратными платформами на процессорах архитектур ARM, MIPS и с высокоскоростными интерфейсами Ethernet (до 10GB, SFP), DDR3 и выше, PCIe, SATA, HDMI. Разработка посадочных мест в соответствии с IPC с учетом требований автоматической сборки ПП; Подготовка выходных файлов для производства. Согласование стеков, материалов, выбор технологии используемых в печатных платах. Условия: График 5/2; ЗП определяется по итогу собеседования; Официальное трудоустройство (белая заработная плата, оплачиваемые отпуска, больничные); После прохождения испытательного срока ДМС; 5 минут от м. Текстильщики; Компания внесена в реестр аккредитованных IT-компаний

-

Компания ARRIVAL создает современный коммерческий электрический транспорт таким, каким он должен быть: доступным, элегантным, тихим и безопасным. Одна из наших основных задач - разработать электрический автомобиль, который будет стоить не дороже аналогичного автомобиля с бензиновым двигателем как по цене покупки, так и по стоимости владения. Чтобы этого достичь, мы стараемся оптимизировать каждый этап его создания - от проектирования, разработки всех компонент, используемых материалов и до программного обеспечения. Программное обеспечение автомобиля (от контроллеров движения до систем искусственного интеллекта), а также сопутствующие сервисы мы разрабатываем в Санкт-Петербурге, автомобили собираются в Банбери (Англия). Мы ищем опытного, увлеченного Инженера-схемотехника, знакомого с "черной магией" трассировки высокоскоростных интерфейсов для разработки высокотехнологичных платформ, интегрированных в продукты ARRIVAL. Ваши будущие задачи: Разрабатывать электронные устройства: разработка схем электрических принципиальных, трассировка многослойных печатных плат. Участвовать в наладке, тестировании, испытаниях и сдаче в эксплуатацию изделий. Взаимодействовать с поставщиками компонентов. Сопровождать производство. Мы ждем от вас: Опыт разработки многослойных печатных плат с высокоскоростными интерфейсами (LVDS; DDR4; FPD-Link III (IV); CSI; GigEthernet; PCIe; SATA; GMSL). Опыт проработки высокоуровневой архитектуры устройств. Отличное понимание схемотехники, цифровых интерфейсов, целостности сигнала, помехоустойчивости, умение производить расчеты импеданса цепей, механической прочности платы, тепловыделения элементов на печатной плате. Знание аналоговой и цифровой электроники, знание современной элементной базы. Опыт разработки цифровых и аналоговых электронных устройств. Опыт работы с одним из САПР разработки и трассировки печатных плат (Altium Designer, Cadence OrCAD Capture, Mentor Graphics Expedition PCB, HyperLynx). Опыт отладки и запуска разработанных устройств. Знание измерительной аппаратуры (осциллограф, мультиметр), умение работать с ней, умение обращаться с паяльником. Хорошим дополнением будет: Опыт разработки встраиваемого ПО для микроконтроллеров ARM. Опыт тестирования аппаратной части устройства с использованием программных средств Linux, bash, python, C/C++, etc. Опыт разработки, отладки драйверов, модулей ядра для Linux. Знание SolidWorks. Знание CAN\LIN. Мы предлагаем: Участие в создании новых высокотехнологичных устройств на старте проектов. Увлеченную своим делом команду. Достойную заработную плату по результатам собеседования. Современный офис в Приморском районе Санкт-Петербурга. Условия работы: оформление по ТК РФ + доплата до 100% оклада для больничных и отпусков, полный пакет ДМС, компенсация затрат на занятия спортом и/или изучение иностранного языка, бесплатные горячие обеды в офисе. Буду рада ответить на вопросы по вакансии. Моя почта: [email protected] Спасибо за внимание! Катя HR manager Arrival

-

Ошибки при работе с DDR3

SVerilog опубликовал тема в Работаем с ПЛИС, области применения, выбор

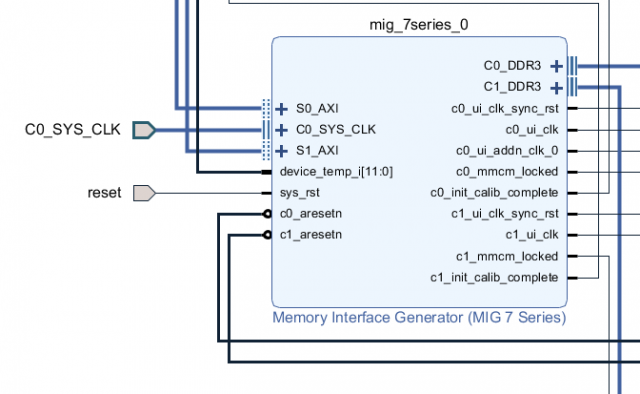

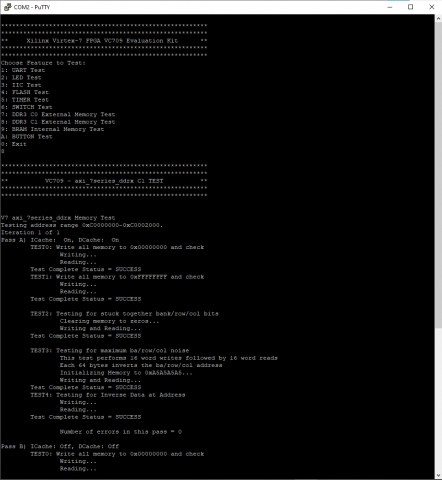

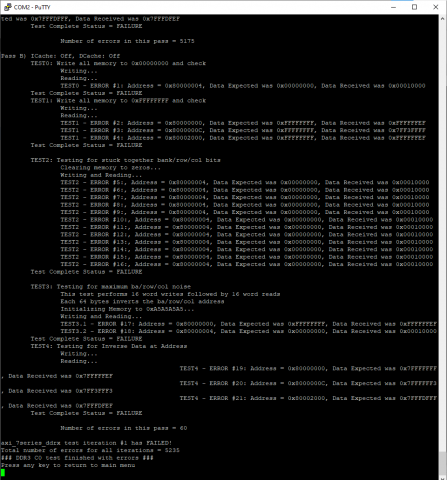

День добрый Имеется плата от Xilinx – VC709. На борту 7ой Виртекс к которому подключены две планки DD3 по 4Гб каждая. Также имеется проект самотестирования платы - так называемый BIST (XTP232) - (проверка платы – что загораются светодиодики, нажимаются кнопочки и пр) – выложен на сайте Xilinx: (https://www.xilinx.com/products/boards-and-kits/dk-v7-vc709-g.html#documentation) Так как планки памяти две, то в block design есть двухканальный mig7: Так вот при тестировании канала C1 тесты успешно проходят: , при тестировании канала C0 тесты не проходят: При этом я просто заливаю немодифицированный bitelf из архива с проектом. Если же скомпилировать проект под vivado 2018.3 то канал C1 также проходит, а канал C0 не проходит, но немного по другому (меняются адреса ошибок) Код проверки каналов для MicroBlaze идентичен для обоих каналов : выполняется вызов функций hello_mem_c0() или hello_mem_c1() Для канала C0: для канала C1: Планки памяти менял местами – результат не меняется (в канале C0 ошибки). Конечно очень подозрительно что немодифицированный bitelf тестирует с ошибками - наводит на подозрения о неисправности... Ранее с памятью DDR не работал, но возможно кто-нибудь сталкивался с чем то подобным, куда копать подскажите пожалуйста- 5 ответов

-

- memory test

- ddr3

-

(и ещё 3 )

C тегом:

-

MicroBlaze + DDR3

Drakonof опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Всем привет, подскажите пожалуйста, как правильно подключить ddr к microScale? Задача для многих простая, но боюсь что я подвис. Дело в том что проц удержеваеться в ресете при дэбаге в SDK. Использую отладку, но при создание проекта абстрагировался от нее и выбрал просто плисину. Vivado 2018.3 Artix 7 Constraint file: set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] set_property BITSTREAM.CONFIG.UNUSEDPIN Pullup [current_design] set_property CFGBVS VCCO [current_design] set_property CONFIG_VOLTAGE 3.3 [current_design] set_property PACKAGE_PIN P6 [get_ports {reset}] set_property IOSTANDARD SSTL15 [get_ports {reset}] set_property PACKAGE_PIN U19 [get_ports {tx}] set_property IOSTANDARD LVCMOS18 [get_ports {tx}] set_property PACKAGE_PIN T19 [get_ports {rx}] set_property IOSTANDARD LVCMOS18 [get_ports {rx}]- 14 ответов

-

- xilinx

- microblaze

-

(и ещё 1 )

C тегом: