petrov

Свой-

Постов

2 764 -

Зарегистрирован

-

Победитель дней

3

Весь контент petrov

-

Сдвинуть сигнал на 90 градусов

petrov ответил C2000 тема в Алгоритмы ЦОС (DSP)

Самурай Только это фильтр нечетного порядка. Нет. -

Сдвинуть сигнал на 90 градусов

petrov ответил C2000 тема в Алгоритмы ЦОС (DSP)

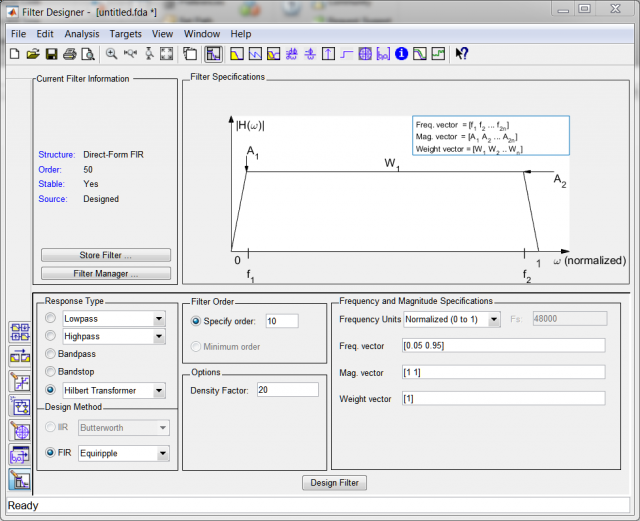

Lmx2315 да Нет. Нужна задержка порядок/2. C2000 Гильберта делают с чётным порядком и симметричной АЧХ относительно частоты дискретизации/4, тогда коэффициенты получаются антисимметричными и каждый второй равен 0, соответственно получается экономия на вычислениях. -

looser Ну не знаю. Я обычно модель на цэ горожу. Потом битэкзактную реализацию на фпга. За пару месяцев перенести получается, с учетом отладки. Хотя я и не бохвесть какой спец в хдэлях. Только модель эту писали не вы, алгоритмы из неё понять невозможно, формальную битэкзатную реализацию из неё не сделать, потому как никаких битов там нет, сделано человеком, который не делал модемы на FPGA, а абстрактной теорией на С развлекался.

-

looser Если есть готовая модель на цэ - почему нет? Тут по книжке-то или статье не сразу разберёшся, а модель на C - всё равно что на китайском языке. Она 100% не описывает рабочий модем и не готова к реализации на FPGA, иначе они бы уже всё сами сделали бы.

-

yes по-поводу оплаты - но с другой стороны, если задача окажется простой, то из-за той же некомпетентности институтского начальства в оплате труда, может получиться и выше рыночной Не является эта задача такой уж простой в принципе, просто специалист по FPGA и имеющий представление о ЦОС не сделает рабочий средненький модем за 4 месяца. По сути уже крах из-за некомпетентности, деньги проедены, время упущено, можно рассчитывать только на бутафорию и некомпетентность контролирущих гос. органов. В аналоге наверняка тоже конь не валялся.

-

измерение фазы на выходе БПФ

petrov ответил _sda тема в Алгоритмы ЦОС (DSP)

_sda https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=23652&page=13&tab=comments#comment-1755048 Посмотрите как фазовая синхронизация в модельке сделана, гармоника выделяется банком фильтров на основе скользящего ДПФ, после вычисления угла прибавляется константа в зависимости от номера максимального фильтра, при переходе от фильтра к фильтру созвездие не скачет, уберёте прибавление, будет поворачиваться скачками. -

модель 8PSK модема

petrov ответил petrov тема в Математика и Физика

https://disk.yandex.ru/d/xktdAddyNLfHrw pi4_qpsk_8_sps_ff_sync_2021_05_27.mdl pi/4 QPSK 8 sps feed-forward sync robust sliding DFT matlab simulink r2016b -

измерение фазы на выходе БПФ

petrov ответил _sda тема в Алгоритмы ЦОС (DSP)

blackfin Для вычисления по этой формуле самой фазы вам понадобится точное значение частоты несущей радиоимпульса. Эту частоту вы можете найти параболической интерполяцией максимума спектра радиоимпульса по трем точкам. Можно даже вычислить две фазы по бинам слева и справа от несущей и сделать усреднение. И это не нужно.)) На выходе максимального фильтра банка фильтров ДПФ уже имеется фаза. Нужно только фильтры взять с пекрытием АЧХ, и скачки устранить практически бесплатной операцией. -

измерение фазы на выходе БПФ

petrov ответил _sda тема в Алгоритмы ЦОС (DSP)

_sda 2). Почему происходят скачки фазы? Есть ли какая закономерность этих скачков? Вы смотрите сигналы с выходов фильтров, посмотрите ФЧХ этих фильтров и увидите скачки между ними. 3). При низком SNR входного сигнала есть вероятность ошибочного определения центрального бина сигнала, а ошибка на один бин даст ошибку фазы 180 градусов. Есть ли методы для борьбы с этим эффектом? Просто прибавляется соответствующая номеру фильтра фазовая константа после angle. Могу на модели фазовой синхронизации в симулинке показать, если будете смотреть... -

Посоветуйте помехоустойчивый код

petrov ответил uriy тема в Математика и Физика

uriy Теперь вижу что для рида-соломона в радиоканале это ничего не даст. Ведь после интерливинга поврежденные биты не соберутся в один символ. RS перемежают на уровне символов из разных кодовых блоков, в радиоканале позволяет огромные пакеты ошибок исправлять. -

Расчет петлевого фильтра ФАПЧ

petrov ответил acvarif тема в Алгоритмы ЦОС (DSP)

escmar так что встрял немного Уйти от потока сознания, описать задачу, задать вопрос на который можно ответить, отвечать на вопросы, следовать отвеченному могут не только лишь все. Так бесконечно можно во встрятом состоянии находиться. -

_sda Не, это не то. То. Не все операции являются фильтрами.

-

Z(conj(x(n)))=conj(X(conj(z)))

-

Демодулятор GMSK

petrov ответил Виталий123 тема в Вопросы системного уровня проектирования

Виталий123 но это реализация в симулинк. А меня интересует только m-реализация А какая разница? Там ничего не скрыто, всё в виде элементарных операций. Если понимание есть, переписать на чём угодно не проблема. -

Демодулятор GMSK

petrov ответил Виталий123 тема в Вопросы системного уровня проектирования

https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=23652&do=findComment&comment=818746 -

коррекция АЧХ и нелинейная фаза

petrov ответил Lmx2315 тема в Алгоритмы ЦОС (DSP)

B. Widrow - A Linear Phase Adaptive Filter c1982alinear.pdf -

atan2 на Verilog

petrov ответил Zalman_ тема в Языки проектирования на ПЛИС (FPGA)

Есть же CORDIC в симулинке. https://www.mathworks.com/help/dsp/ref/complextomagnitudeanglehdloptimized.html Вычисляет от любой входной разрядности типа fixdt(). -

ECC с "подсказкой"

petrov ответил vitaly_n тема в Математика и Физика

vitaly_n Круто, гигабит на Cat.5e. Или я чего-то не понимаю, или в IEEE со своим 1000BASE-T дурью маются. -

ECC с "подсказкой"

petrov ответил vitaly_n тема в Математика и Физика

vitaly_n Сколько должно по одной витой паре передаваться? 250 Мегабит/c? -

des00 Всё вы правильно делаете. Только для передачи сигналов между регистрами через комбинационные схемы никакие блокирующие присваивания не нужны, хотелось бы чтобы это говно мамонта померло уже.

-

des00 Ну не нравится вам RTL кодирование, не занимайтесь им. Очень даже нравится. Вот в HDL и HDL симуляторах не понимаю что может нравиться. Платность чего-либо не отменяет того, что все эти блокирующие присваивания и т. п. - мура мурой на ровном месте. Если надо, будем и Icarus Verilog с Yosys использовать, куда деваться.

-

RobFPGA Можете привести пример такого чуда - языка который сразу, из высоких абстракций синтезирует железо? Дело не в высоких абстракциях, они на самом деле те же самые, просто упор на решение самой практической задачи, а не копошение в блокирующих присваиваниях, громоздких HDL симуляторах и т. п. И без предварительно перегона в "богомерзкий" V/SV/VHDL ? Разумеется с перегоном, в синтезаторы иначе не передашь.

-

RobFPGA Причем опять же чаще всего это не проблема языка V/SV Это проблемы языка, неочевидные абстрактные конструкции не соответствующие происходящему в железе, плохо читаемый синтаксис, возможность написать одно и то же кучей разных способов и т. п., 99,99% кода плохо написано, язык быстро приводит к потере обозримости, провоцирует на лепилово, отнимает впустую много ресурсов от решаемой задачи. Причём сейчас есть возможность получить довольно сложные цифровые схемы вобще не притрагиваясь к HDL и HDL симуляции, вот и думай после этого, а в чём же смысл блокирующего присваивания, а ни в чём, мусорные знания, которые следовало убить на этапе создания.

-

RobFPGA Можно и объектом, а можно и чисто конструкциями языка которые присваивают два (2) значения в одну (1) переменную. Поэтому мне и непонятны такие "непринципиальные принципы". Нам зачем эти конструкции, ради конструкций? Это же чистая бутафория, ведущая к неправильному пониманию, небольшие изменения такой конструкции будут правильно симулироваться, но будут приводить к ошибке в описании реального железа, или ещё хуже к синтезу монстроидальной логики. Это очень плохие свойства языка, совершенно ненужные и вредные.