-

Постов

383 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные nice_vladi

-

-

On 2/3/2023 at 3:45 PM, alexPec said:

Всем доброго дня!

Заметил такую штуку на Ultrascale+. У меня 2 ядра CORTEX A используют для stdout один и тот же уарт - толкаю туда всякую отладочную информацию. Когда получается так, что одно ядро выводит в уарт, и в это время туда же начинает другое ядро выводить - одно из ядер вылетает, видимо в исключение, SystemAbortHandler. Это я что-то криво сделал или так и должно быть?

PS уарт внешний, не из PS. Расположен в PL.

По-идее, если ядра заходят в УАРТ через AXI interconnect, он должен буфферизировать или разрешать такие ситуации.

-

18 hours ago, Maverick_ said:

Добрый день

Начал работать с коркой fft ver 9.1

Создал к корке обвязку - в виде генератора синуса и косинуса из памяти со стриминг интерфейсом для выдачи данных на корку fft

Данные для корки fft :

Младшие 16 бит - значения синуса

Старшие 16 бит - значения косинуса

Выход корки соеденил со входом второй коркой fft сконфигурипрванную на обратное преобразование.

С матлабом ничего не сошлось.

Конфигурацию по стриминг интерфкйсу делаю.

Где подводные камни/нюансы могут быть при работе с коркой fft ver 9.1?

Неправильно подали размер ПФ

Неправильно подали размер ЦП (если используется). Он привязан к максимальному размеру ПФ, а не текущему

В матлабе используется бит-ту-бит модель?

В ядрах есть дополнительные флаги, которые подсказывают, что не так с преобразованием. Смотрите их

-

Добавлю, если надо просто взять и посчитать, не погружаясь, то MATLAB может сделать вот так:

bin2dec(num2str(shift2mask('x3+1', 100)));Где 'x3+1' - полином ПСП (очевидно), а 100 - количество сдвигов. Результат выполнения - та самая искомая маска. -

18 minutes ago, StewartLittle said:

Это корпуса с цоколевками, совместимыми (частично или полностью) с ПЛИС других производителей:

....

А такая штука для QFP корпусов планируется? Ну и, в целом, реализуема? Или там сложнее из-за того, что ноги только по краям?

-

3 hours ago, RobFPGA said:

А что тут удивительного? 2 канала по 16 бит 250 Msps. рядовые ADC/DAC на текущий момент.

Да я, почему-то, подумал про один канал 32 бита 250 MSPS

-

Offtop, но

18 hours ago, Caruso said:... DAC с полосой 250MГц/32бит, ADC с полосой 250МГц/32бит ...

Нифига себе!

-

20 hours ago, khach said:

Скорее всего там между железом и софтом собственно секвенсирования имеется HAL. Т.к у Oxford было несколько реализаций харда. Вот на уровне HAL и надо "привить" свое железо. Тем более что Xilinx тоже теперь малодоступен, не говоря уж о древних burn-brown-вских преобразователях.

Именно. И есть шанс, что в ближайшем будущем все будем делать на Gowin/Pango/ВЗПП. Так что, если известен протокол обмена между "железом" и софтом - то имеет смысл и в этом направлении покопать.

Хотя, конечно, хозяин барин

Offtop

Понравилась цитата из файлика: со временем опустится ниже $100 (< ₽6000) -

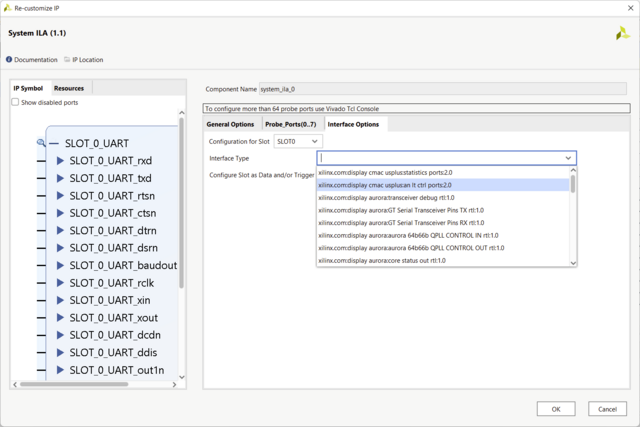

RTFM, я думаю: https://docs.xilinx.com/v/u/en-US/pg261-system-ila

Ну и само ядро можно потыкать. Например, у меня выбор вот такой:

Достаточно богатый выбор, я бы сказал) Жаль, что только для BD работает. Хотя, думаю, можно извратиться и сгенерированное ядро подключить куда-то в RTL.

-

Я думаю, @vov4ick имеет в виду, что проще будет разработать плату с нуля, чем тратить время на реверс-инжиниринг и копирование. В целом, идея имеет право на жизнь. Если вы понимаете, что плата должна делать: передать/принять какие-то ВЧ сигналы, упаковать их в определенный формат и отдать на ПК. И это займет времени меньше, чем реверс-инжиниринг и повторение, скорее всего.

Поэтому и странно видеть упорство "хотим точно такое же!". Но, возможно, этому упорству есть рациональное объяснение, судить не возьмусь.

-

К сожалению, чтобы начать работу и загрузить необходимые дополнительные программные средства, необходим доступ к закрытому разделу сайта Xilinx vitisnetp4 Lounge, который для разработчиков из РФ не предоставляется. Тем не менее, надеемся, что это не помешает российским разработчикам использовать новые возможности Vivado и Vitis в своей работе.

Как же хорошо

-

Именно для генерации можно попробовать что-то из этого скомпилить:

https://github.com/AndreRenaud/PDFGen

https://github.com/libharu/libharuНу а в целом, отказаться от .pdf в пользу голого html тоже неплохая идея. Это тоже универсальный формат. Даже если нет браузера - можно любым текстовым редактором открыть.

ЗЫ. И, как сказали выше, обязательно проверять, есть ли килирица в шрифтах, которые планируете использовать.

-

On 8/13/2022 at 1:01 PM, new123 said:

в моделсиме я уже только подсматриваю ) а всю симуляцию я перевожу на тестовые окружения на других языках.

пока вывернулся, что по струткурам накатал некий конвертер, который создает add wave c -label и векторами

Ну так, за убеждения надо страдать xDD

-

On 8/13/2022 at 1:21 PM, makc said:

В операционках квант времёни порядка 10 мс, названное вами время (мои наблюдения совпадают с вашими) на 2 порядка больше. Плюс ещё есть затраты времени на запуск PLL и т.п. стартап PL. Т.е. использовать PL в таком ключе мне видится крайне неэффективным.

Ну так опять же: смотря, что делать. Допустим, если у вас релейка или какая-нибудь коммутационная вещь, то перепрошивка == разрыв связи/потеря маршрутизации. Тогда уже не важно: что 100 мс, что 1-2 секунды.

-

14 hours ago, new123 said:

2) потом конвертирую его в wlf

vcd2wlf dump.vcd dump.wlf.vcd файлы УЖЕ не хранят информацию о enum и т.д. Если уж смотрите в модельсиме, почему бы сразу не отлаживаться в модельсим?

-

15 hours ago, makc said:

В Zynq PL грузится только из PS, но это не очень быстро...

Ну смотря какие требования. Все-таки, PL из PS грузится <1секунды. Если уж перешиваешь PL, то 1 сек может быть вполне удовлетворительным результатом.

-

On 8/2/2022 at 11:40 PM, Dobermann said:

ofdm хорошо проходит, но кодек иногда коробит фазу. Я, лично, не нашел решения иного, что бы вообще без искажений.

А как кодек вообще влияет на фазу сигнала? Можно, пожалуйста, ткнуть носом?

Всегда думал, что это независимые вещи. Ведь после кодека мы оперируем битами, которые затем модулируются (маппер) и потом уже раскладываются на поднесущие OFDM.

-

> Не понятно что там с SPI могло не получиться.

Ну это со слов коллег. Сам, как говорил, не пробовал. Так что, могли и обмануть.

-

On 7/27/2022 at 10:06 AM, Dmitry_B said:

В доках никак найти не можем, отсюда и вопрос

А вторую часть предложения?)

Вообще, быстрогугл показал вот это:

А вообще, конечно, зависит от семейства и условий. Вы что сделать-то хотите? От ПЛИС что-то затактировать?

-

Спустя определенное количество времени пришло понимание наивности вопроса в первом топике.

Перенос производства с фаб на фаб == почти полная переработка дизайна.

В РФ не нашлось стабильного 90/180нм. Эти техпроцессы отлажены только для простых (и аналоговых) устройств. С цифрой хуже, коллегам SPI не смогли прикрутить для управления усилителем.

Насколько стало известно - ведутся работы по пробным запускам ваферов на мощностях Микрона. Но к чему это приведет - пока не ясно.

-

On 7/27/2022 at 1:23 AM, Dmitry_B said:

Хотелось бы до того, а не после того, как будет все изготовлено.

Еще можно посмотреть доки и увидеть заявленные величины. Или купить (найти) отладочную плату и на ней потестить.

-

On 7/26/2022 at 11:34 PM, Dmitry_B said:

Как определить джиттер сигналов, которые выдает ПЛИС Xilinx?

Осцилографом..?

-

On 7/25/2022 at 3:04 PM, Zversky said:

Просьба высказаться или направить по нужному адресу, ежели тема сия уже где-то поднималась

Как-то упражнялся с синтезом. С симуляцией примерно тоже самое.

-

-

5 minutes ago, VoltageCurrent said:

...но только, чтобы не как $bits, который в подобном случае выдаёт "32", а что-нибудь, что бы выдавало именно "3" в случае TEST_PARAM=5, "4" в случае TEST_PARAM=10 и "5" в случае TEST_PARAM=22 ?

$clog2($size(signal))

Получить значение generic в Top с помощью TCL (Vivado)

в Среды разработки - обсуждаем САПРы

Опубликовано · Пожаловаться

Вот это: https://github.com/hukenovs/tcl_for_fpga/blob/master/src/modify_top_info.tcl можно

Можно использовать за референс, там как раз перебор параметров идет.