-

Постов

383 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные nice_vladi

-

-

Прочитал тему, тоже очень хочу посмотреть на этот проект. С удовольствием приму экземпляр в лс.

-

2 hours ago, turnip said:

Во-первых по цене кусается. Во-вторых не хочу привязываться к конкретной плате\производителю чтобы можно было собирать из доступных на рынке продуктов.

Цена вполне гуманна для готовой платы с СнК на борту.

Вы в любом случае будете привязаны к железу. К stm32, к разъемам HDMI/VGA, производителю ПЛИС и т.д.... Можно попробовать отвзятаться от железа и производителя в каких-то пределах, но это точно не про ПЛИС. Везде и всегда вы обязаны будете пользоваться софтом производителя для компиляции, прошивки и отладки. Разве что для симуляции есть open-source решения, да и то, они пока оставляют желать лучшего.

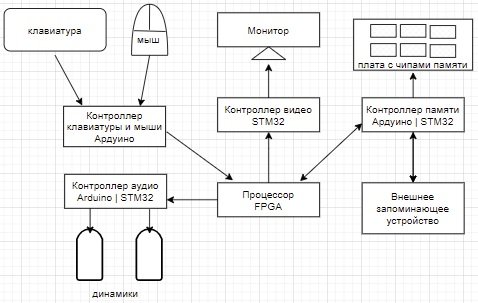

При использовании СнК у вас есть ПЛИС на которой вы вольны творить всё, что угодно, в т.ч. процессор и есть настоящий процессор, который может взять на себя роль всех остальных устройств на вашей картинке.

Ну, либо берет кучу stm32 и упражняетесь. Результат не гарантируется) Тем более, если вы хотите +- скоростные интерфейсы между всеми устройствами системы.

ЗЫ. В таких темах регулярно появлялся @iosifkи доступно разъяснял разницу между нацеленностью на результат и нацеленностью на процесс.

-

6 hours ago, turnip said:

Всё украдено до нас:

https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=1046 -

Вообще, т.н. hardware in the loop имеет место быть. Например:

https://inspirehep.net/files/06c877a9ec568472aac84923dd0056a3

Правда затраты времени на организацию всего этого и написания тестов... Разве что для проектов с очень длительным сроком жизни. Что бы время, потраченное на организацию тестов и стенда равномерно размазалось на много лет

-

55 minutes ago, Александр77 said:

Прошу помочь с пониманием сути проблемы и главное с ее решением.

Мне кажется RTFM:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cfg/cfg_cf51001.pdf

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cfg/cfg_ch11_vol2.pdf

Ну и с осциллом смотреть, что там на конфигурационных ногах творится. Тем более, они у вас заведены на резисторы - можно удобно ткнуться щупами. Или даже распаять проводки и на многоканальном осцилле смотреть прям как в мануале - параллельно) Ну и JTAG тоже посмотреть, форму импульсов особенно.

-

UPD:

Есть обновление. Итак:

1. В настройках IP core снял чекпоинт SGMII PHY mode. Т.е. физика включается в режиме MAC.

После этого IP core начало корректно показывать status_vector.

2. Процессор начал правильно определять скорость, состояние линка.

Но при включении линукса с отключенным кабелем всё равно надо перезагружать интерфейс. Однако, при перепрошивке всё работает нормально. В общем, всё заработало почти так, как требуется.

-

Всем здравствуйте,

Поднимаем ZynqMP. Плата ZCU102 rev 1.1. Нужно подключить один из трансиверов SFP коробки к процессору через EMIO. С этим особых проблем не возникло, использовали мануалы от Xilinx. Поднялся трансивер, поднялся интерфейс в процессоре.Есть следующие ограничения:

1. Интерфейс работает только в режиме 1G, поэтому процессору нужно каждый раз это указывать. Команда из мануала от Xilinx:

ethtool -s eth0 speed 1000 duplex full autoneg off

Т.о. автосогласование не работает. В том числе после переподключения кабеля, нужно заново пинать процессор делая вкл/выкл автосогласование.

2. Следует из (1) при перепрошивке ПЛИС нужно опять пинать процессор.

Всё это очень неудобно для разработки. Может быть, кто-то сталкивался и знает, как научить linux понимать автосогласование через EMIO?

Что сделано:

IP ядро PCS/PMA 1G/2.5G в режиме SGMII, Autonegotiation включено. Режим физики SGMII PHY mode. На процессор заведены MDIO и an_interrupt.

status_vector IP ядра почему-то всегда показывает скорость 00 (10 Мб), вне зависимости от состояния подключенного линка. an_interrupt поднят в 1, процессор, почему-то, его не сбрасывает. Это то, что увидел chipscope.

Процессор видит физику по MDIO и может читать/писать регистры IP core.

ЗЫ. Добавленные патчи:

0001-net-xilinx_phy-Add-flag-to-reset-after-clock-enable.patch

-

-

Всем здравствуйте,

Дошли руки причесать и выложить в репозиторий. Возможно кому-то будет полезным.

-

8 hours ago, AlexRayne said:

Если ктото ведает достойный UI для гита - подскажите?

Мне нравится Sublime Merge. Использую вместе с редактором Sublime Text. У них друг в друга интеграция есть - оч удобно

-

4 minutes ago, blackfin said:

Тогда, наверное, нужно оставить и файлы *.xcix

У меня их вообще нет.

-

Итак, закончил упраженения с новой вивадой. Была установлена 2020.2. В ней создан проект с block design, ip. Всё это помещено в git. Опытным путем выяснил, что для корректной сборки проекта достаточно оставить в нём .xci файлы. В реузльтате получил вот такой gitignore:

netlist/*.cache netlist/*.hw netlist/*.gen netlist/*.runs netlist/*.sim netlist/.Xil netlist/*.ip_user_files netlist/*.srcs/sources*/bd/** !netlist/*.srcs/sources*/bd/**/*.xci netlist/*.srcs/sources*/ip/** !netlist/*.srcs/sources*/ip/**/*.xci .ioplanning *.jou *.log sim/**/work sim/**/*.ini

Единственное, что стало хуже - после выгрузки чистого проекта из git, Vivado оооочень долго его открывает. Последующие запуски - нормально.

-

12 minutes ago, fguy said:

В 2021.1 оставил папку srcs, файл с проектом xpr и сое файл от фира - проект открылся без ошибок

...

В 2021.1 в отличии от 2020.2 в новый формат проект можно перевести при конвертации из предыдущих версий вивад

Что за праздник такой?) Поставлю качаться!

-

21 minutes ago, fguy said:

Начиная с вивады 2020.2 она хранит весь проект в папке <имя проекта>.srcs без мусора, образующегося при синтезе и далее (он вынесен наконец то в отдельную папку). Так что хранить можно ее в гит полностью + сам файл проекта. Такой вариант позволяет сразу открыть проект в первозданном виде без затрат времени на восстановлении из скриптов - у него только один недостаток - это новые версии вивады с кучей других косяков

Как в 2020.2 пробовал. Без папок .gen и .ip_user_file проект не разворачивается - сыпет ошибки. Возможно, я где-то ошибся... Не подскажете полный алгоритм, даже если звучит очень просто?

43 minutes ago, RobFPGA said:Но тут проблема может быть в том что это не может гарантировать целостность проекта и результат сильно зависит от стиля и организации в работе с проектом.

Да, проблема. Хочется однозначно и железно всегда складывать в гит определенный набор файлов, который обеспечит развертывание проекта "с чистого листа". Пока, как писал выше, приходится складывать огромное количество файлов. Особенно при наличии нескольких крупных IP cores.

Лирика: в Quartus я точно знал, что сложу .qsys, .qsf, .sdc файлы, и при разворачивании проектов получу полностью готовое окружение. В vivado могу только мечтать и придумывать костыли.

-

7 minutes ago, dxp said:

А IP ядра вы как храните?

Складываем в гит .gen и .ip_user_files.

-

34 minutes ago, dxp said:

А bd разве не представляет собой ординарный tcl скрипт (простите мою серость, как-то до сих пор удавалось обходиться без bd, но есть желание и эту технологию подтянуть)? У нас и IP тоже хранятся под гитом как tcl, который и является исходником. Ну, это как вариант. Сейчас перешли на более продвинутый путь, когда и tcl для корки генерируется из параметров для оной, хранимых в более удобном (YAML) формате (вот этот файл и идёт под контроль, а тот же tcl для корки - это продукт генерации).

БД можно сохранить в .tcl. Но потом это нужно как-то развернуть и добавить в проект сам .bd и еще кучу файлов, которые будут сгенерированы после его синтеза. Я пока на этом месте застрял)

-

Апну тему. Пытаюсь изменить привычки и начать работать со скриптами, вместо складывания в гит кучи файлов вивады. Столкнулся с несколькими непонятностями:

1. Как правильно добавлять и описывать block design в проекте? С учетом того, что всё хочется делать в скриптах, раз уж взялся. Кстати, ни один внешний фреймворк или мануал не учитывает bd файлы, насколько я вижу.

2. Что с автоматизацией? Имею в виду, нет никакого желания перед коммитом делать write_*_tcl, потом разбираться, куда сложились эти файлы и т.д. В общем, как минимизировать ручной труд при использовании вивады со скриптами?

-

1 minute ago, Maverick_ said:

Это я сделал в первую очередь...

Тогда не знаю, гадать можно долго. Я бы просто пересоздал проект с самого начала, если уж совсем затычная ситуация.

-

26 minutes ago, Maverick_ said:

может подскажете в чем проблема?

PS Ошибки не понимаю - не знаю как их исправить...

Попробуйте зайти в настройки проекта и ручками удалите ненужны .ip/.qsys и остальные файлы.

ЗЫ. Project -> Add/Remove files in project -> выделяете ненужные -> Remove -> (!важно)OK

-

18 minutes ago, RobFPGA said:

При такой "каше" первым делом надо пересматривать структуру дизайна, а не латать "тришкин кафтан" заплатками.

+++

Пока дизайн не очень большой и сложный, я бы перетряхнул всё с чистого листа. Изначально задавшись ограничениями:

- на передельную частоту: скажем, 200 МГц, хотя и это для циклона5 не сильно комфортно

- на концепцию использования тактовой частоты: только положительный фронт, одна тактовая в проекте, в случае необходимости понижения - использовать clock enable

Ну и как следует отсимулять всё это.

7 hours ago, Мур said:Имею право разделять RAM на две независимые(200 и 100) парадигмы, где одна обслуживает скоростную шину, другая в сервисе SPI

Тогда соблюдайте парадигму: для 200 все сигналы формируйте на 200, для 100 - все сигналы на 100.

7 hours ago, Мур said:Отрицательный фронт(раньше в IP его можно было выбирать) взят опытным путем, поскольку с прямым он тормозит в TQ в два раза!

Нужно понимать, как он соотносится с остальными сигналами в дизайне. Да и слепо верить TQ не стоит. Он показывает только то, о чем вы просите. Где-то у @des00 были годные статьи на эту тему.

7 hours ago, Мур said:Комбинаторика перед регистром - это нормально, тем более она есть быстрый мультиплексор(и регистр на выходе!)

Зацепился взглядом за то, что вы входной сигнал (с пина) протащили через логику и только потом щелкнули в регистр. С учетом того, что у вас 100+ МГц в дизайне, я бы не стал так делать.

7 hours ago, Мур said:С wt_s не смотрел, поскольку в TQ его нет. Но за это спасибо! Буду внимательнее... (Порт В там как раз 200МГц!) Так что все тут верно..

Он есть, просто был очень глубоко в списке слаков. По умолчанию TQ показывает только первые 200 худших путей.

ЗЫ. Либо, если "и так сойдёт" и не нужно будет всё это развивать и поддерживать, просто забить на все предупреждения TQ. Мб и не имеет смысл тратить время на перетряхивание проекта о котором больше вы никогда не вспомните...

-

13 hours ago, Мур said:

Тоже решил заглянуть, проходя мимо. Развернул проект - не нашел слаков, связанных со счетчиками. Только куча addr_mem_b[...], связанных с разными тактовыми доменами и т.д.

А зачем на 200МГц по отрицательному фронту какие-то данные перекладывать? Там такая анархия творится... Мне кажется, дело не столько в счетчиках, сколько в этом. Перейдите в единый тактовый домен, уберите работу по заднему фронту тактовой.

ЗЫ.

Во всех RAM на порт А подана тактовая 100 МГц, а addr_mem_b защёлкивается на 200 МГц.

mem0: RAM2P PORT map ( address_a => addr_mem_b, address_b => adr_b, --BUS clock_a => clk100_s, clock_b => nlk200_s,--clk200_s, --clk200_s, --BUS data_a => DATAspi_b, data_b => dat_b, --BUS wren_a => wsw0_s, wren_b => ww0_s, --BUS q_a => rim0_b, q_b => bus0_bus --BUS ); ... ... aaa: process (clk200_s) begin if clk200_s'event and clk200_s = '0' then addr_mem20t_b <= addr_mem200_b;--тут конвейер по адресу addr_mem2tt_b <= addr_mem20t_b; addr_mem_b <= addr_mem2tt_b; end if; end process aaa;

Тоже самое с "address_b => adr_b, --BUS". Входной сигнал через комбинаторику засовывается в порты RAM на 200 МГц.

Тоже самое с сигналом wt_s - формируется на 200 МГц, используется для записи в порт RAM, работающий на 100 МГц

-

15 hours ago, TheMad said:

Сие мне неизвестно, но не может быть больше 5 МГц. А ещё судя по длительности импульса и потреблению, а также по тому что во встроенных АЦП в процах признаком хорошего тона является выкидывание парочки первых результатов можно предположить что тактовая АЦП находится в пределах 0.5-1.5 МГц.

А на картинке импульса с конденсатора какая цена деления по оси Х?

Объясню: тоже видел спектрометр на детекторе мощности. Примерно такая же схема, немного больше рассыпухи. Так вот, в нём импульс приходил на АЦП с частотой 1 МГц. И из-за маленькой длины импульса АЦП не всегда "попадало" на импульс. Период тактовой АЦП 1/1е6 = 1 мкс. Если пик импульса, приходящего на АЦП короче периода тактовой АЦП, то АЦП просто физически не может его всегда правильно оцифровывать, оно не видит пик.

В вашем случае, для тактовой АЦП 500 кГц (худший случай) длина импульса должна быть не менее 2 мкс.

-

Здравствуйте,

Если аналоговый тракт в порядке - надо грешить на цифру.

Осциллограмы импульса - это входной импульс? Или тот, который уже на входе АЦП?

Какая тактовая у АЦП?

-

Уже не первую вакансию вижу, где одновременно с требованием опыта работы 3+ лет предъявляют требования к оценкам в дипломе. Всегда думал, что при наличии релевантного опыта работы по специальности в диплом универа вообще никто никогда не смотрит. Это прям требование работодателя? Либо какая-то формальность от вашей фирмы?

Передача значения из TCL в HDL

в Среды разработки - обсуждаем САПРы

Опубликовано · Пожаловаться

У vsim есть ключик -G для переопределения всех параметров с таким именем в исходника, либо ключик -g, который перреопределяет параметр с таким именем в модуле верхнего уровня