Jackov

Участник-

Постов

436 -

Зарегистрирован

-

Посещение

-

Если правильно понял нужно wire [0:0]se1[0:5]; передать в модуль Mych mych1(,,,,,,,,,,se1,,,); Во-первых, wire [0:0]se1[0:5]; это неупакованный массив, а неупакованный массив в модуль не передаётся. Во-вторых, непонятен смысл [0:0]. Если [0:0] не нужен, тогда wire [0:0]se1[0:5]; можно переписать на wire [0:5]se1;, а лучше на wire [5:0]se1;. И вот тогда передать его в модуль обычным способом. И не рекомендую использовать позиционное соединение, луче соединять по имени: MyC myc(.StartTact(StartTact), ...); И когда много портов записывать их в столбик.

-

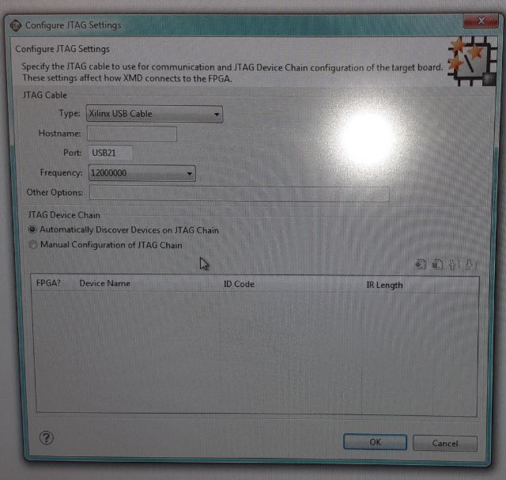

USER3, USER4 тоже не помогли. Обнаружил что в конфигураторе корки MicroBlaze есть аналогичная опция, там тоже по умолчанию USER1 стоит. После смены этого значения SDK выдал сообщение что аппаратная часть изменилась и надо пересобрать проект ПО. Однако после пересборки перестал работать отладчик. Предполагаю, что если пересборку я бы не делал он всё равно бы не работал. Как я понимаю конфигурация процессора хранится в xml-файле. Так вот он что до смены USER1 на USER2 что после одинаковый. Я даже для убедительности заново проект ПО создал - не помогло. Скорее всего надо ещё ответную настройку где-то в SDK поменять, но я не нашёл и вернул обратно на USER1. Но пока лазил, искал наткнулся на одно окошко Xilinx Tools -> Configure JTAG Settings В поле Type сменил значение с автоматического на указанное, остальное не трогал и, о чудо, теперь отладчик с ЧипСкопом не конфликтуют и отлично вместе работают. Но всё же ЧипСкоп стал работать помедленнее, т.е. иногда пишет что jtag занят и соответственно у него простой в работе. Но всё же это намного лучше чем ничего, уже можно нормально отлаживаться.

-

Аналог VirtalPin в ISE

Jackov ответил Jackov тема в Среды разработки - обсуждаем САПРы

Мда, в UG625 есть противоречие, сначала пишут потом Перебрал все варианты, но ни (* S = "YES" *) CT #(4) CTBits(.Q(), .R(1'd0), .L(1'd0), .INC(1'd0), .D(4'dx), .C(1'd0), .aR(1'd0)); ни (* S = "YES" *) wire [3:0]Q; (* S = "YES" *) wire R, L, INC, C, аR; CT #(4) CTBits(.Q(Q), .R(R), .L(L), .INC(INC), .D(4'dx), .C(C), .aR(aR)); ни запись в UCF-файле ... NET Q S; ... результатов не дали. -

Выбрал USER2, но, увы, не сработало...

-

Аналог VirtalPin в ISE

Jackov ответил Jackov тема в Среды разработки - обсуждаем САПРы

Странно, конечно, не должно быть такого. Он же не знает какая информация будет загружаться в сдвиговый регистр, а значит каждый разряд является уникальным источником. Сделал так: (* S = YES *) CT #(4) CTBits(.Q(), .R(1'd0), .L(1'd0), .INC(1'd0), .D(4'dx), .C(1'd0), .aR(1'd0)); В ответ он ругается: Догадался написать в кавычках: (* S = "YES" *) ... Ошибки уже нет, но получаю ворнинг: Короче что-то не сработало. -

Аналог VirtalPin в ISE

Jackov ответил Jackov тема в Среды разработки - обсуждаем САПРы

Сейчас использую сдвиговый регистр. Есть две незадействованные ноги, одну подключаю к клоку регистра, другую к последовательному входу данных, разряды регистра подключаю к неиспользуемым портам модулей. Но это, что и VIO, тоже костыли. Здоровый документ, на какой странице смотреть? Да и поможет ли? UCF-файл на этапе синтеза не используется же. Может какой-нибудь (*атрибут*) существует? -

Jackov подписался на Аналог VirtalPin в ISE

-

Аналог VirtalPin в ISE

Jackov опубликовал тема в Среды разработки - обсуждаем САПРы

У меня в проекте есть модуль (несколько), некоторые его порты пока подключить некуда. Если их оставить неподключёнными компилятор этот модуль оптимизирует, многое оттуда выкидывает с выводом целой кучи ворнингов. Во-первых, эти ворненги очень сильно мешаются, во-вторых мне хотелось бы иметь в проекте полные, неоптимизированные, модули. В Квартусе есть очень удобная для этого штука - VirtalPin. Их можно подключить к пустым портам модуля и будет так как будто порты подключены к выводам ПЛИС и сминимизированы модули не будут, но по факту порты ни на какие выводы подключены не будут. Нужно что-то подобное и в ISE. -

Разобрался, и года не прошло. Есть два bmm-файла, один в проекте плисины в каталоге где файлы корки памяти лежат, другой в проекте SDK. Называются по разному, но оба .bmm. Надо следить чтобы в обоих этих файлах пути до блоков памяти были актуальны, а это почему-то не всегда так. А вот отладчик и чипскоп очень плохо работают одновременно. Если поставить чипскоп на ожидание и ходить в отладчике по шагам, то либо чипскоп фигню будет показывать, либо отладчик повиснет. Иногда бывает и нормально, но это скорее исключение, всё равно работать так невозможно. Подозреваю, что всё же я что-то делаю не так, ибо ситуация то типичная, не могли же они такую халтуру наделать и оставить не исправляя на протяжении многих версий?

-

Это тоже скрипт МоделСима, назначает вывод нужных сигналов на временную диаграмму и указывает в каком виде они будут показаны. Посмотрите серии 11 и 12 из этого плейлиста, поможет разобраться что есть что https://www.youtube.com/playlist?list=PL4UMfOeGYsvblwrP3VYKHq11xgkxVqoUj

-

Как попало, но трансформаторы расположены близко к разъёмам, почти вплотную. Что значит правильные контакты? В смысле распиновка? Имеется pcb-шник, там всё хорошо видно что куда подведено.

-

И как? Симулятор исполняет тестбенч, что в тестбенче написано так и будут переключатся сигналы входных воздействий. Сам симулятор ничего не переключает.

-

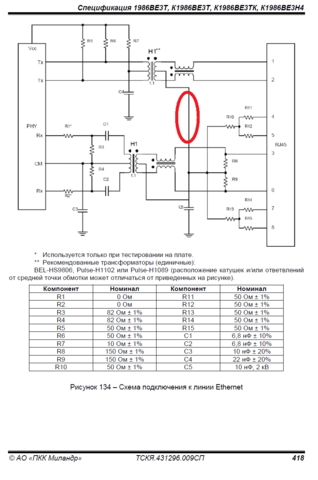

Поставил R8, R9 и C3. Положительного эффекта нет. Общую связь, обведённую красным, пока разъединить не удалось, ноги соединяются под трансформатором, это надо его выпаивать чтобы перетереть дорожку. Пытался так делать - там вообще какая-то бесовщина начались и я это направление развивать не стал. Интересно вот что. Исключил коммутатор, соединил два устройства напрямую, запаяв короткую витую пару, около 30см, непосредственно на ноги трансформаторов и всё заработало. До этого тоже соединял без коммутатора, но кабелем метра 3-4, и он был составной. На устройствах разъём СНЦ160, а на коммутаторах обычный rj45, а кабеля СНЦ-СНЦ такого нет, потому соединял СНЦ-rj45 -- rj45-rj45 -- rj45-СНЦ. rj45 соединял между собой через переходничок мама-мама. Кабель rj45-rj45 был, естественно, с переворотом, чтобы rx шёл в tx. И вот с такой конструкцией были сбои. А вот как его найти то? А то говорят "интернет помнит всё". Только как что-нибудь действительно понадобится фиг это найдёшь.

-

Jackov подписался на Программирование ПЛИС для маленьких спутников

-

Попробуйте для начала посмотреть этот плейлист https://www.youtube.com/playlist?list=PL4UMfOeGYsvbPDapirH9GOJ93CBSOe49Y

-

Да хрен знает, может и в описании регистров ошибка. Ага, ясн, спс. Оставлю это напоследок. Тут обнаружилось, что в схеме подключения трансформатора не хватает резисторов R8, R9 и конденсатора C3: Критично ли их отсутствие? И ещё. Вот смотрю я на схему и меня смущает связь обведённая красным. Не будет ли из-за неё взаимных влияний сигналов друг на друга (и соответственно искажений) идущих одновременно по линиям Rx и Tx? Зачем вообще так сделано?

-

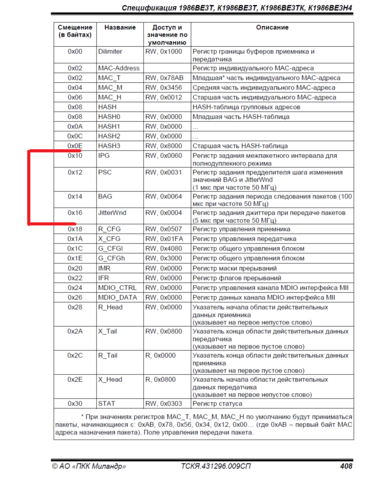

Факт есть факт. На своём устройстве я ничего не трогаю, на ПК меняю ful/half. В обоих случаях на ПК есть приём. Если не трудно повторите тезисно, может действительно что-то пропустил. Да проверял уже... Ну оно, собственно, и логично. Если скорости совпадают, то почему должен отсутствовать приём. Это делалось исключительно ради эксперимента. У меня была задача проверить мой передатчик, передаёт ли он все кадры. В ответ с ПК я ничего не посылал. Я только подсчитывал кадры. То есть виндовозными средствами никак? У меня нет уверенности что установка режима в 1986BE3T отрабатывает правильно. К тому же есть подтверждение И если BE1 глючат то почему BE3 не могут? Вот я и хотел через ПК посмотреть какой режим стоит по факту. И ещё вопрос, кто-нибудь может объяснить мне смысл этих полей: