Kapsik

Свой-

Постов

107 -

Зарегистрирован

-

Посещение

Весь контент Kapsik

-

Да, сокрытием исходников. Возможно я что-то упускаю, но про криптование исходников для Altera/Intel мне не известно. На сайте у них вот так: https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/solutions/rd10172006_472.html . Пишут хотите исходники, делайте нетлист.

-

Это план Z. Очень не хочется ворошить код, получится отдельная ветка и потенциальные грабли, на которые рано или поздно наступишь... В Xilinx есть возможность слить два нетлиста - "link_design". В Quartus даже отдельный пункт сборки Merge Netlist, казалось бы как раз для этого слить два qxp в один, но пока не выходит.

-

Необходимо создать нетлист, где один из исходников будет открыт. Разработка в Quartus 18 Standart, не Pro. Дерево проекта, например такое: -top_module --submodule l1 ---submodule l2 ----submodule l3 -----submodule l4 ---submodule l2 ---submodule l2 --submodule l1 ---submodule l2 Задача упаковать все в нетлист, кроме модуля “l4”. Пользователь, которому будет передан нетлист «top», должен иметь возможность менять исходник модуля «l4» и видеть эти изменения в своем проекте, где нетлист «top» это один из сабмодулей. Задал вопрос на форуме intel, но ответа пока нет, возможно кто-то сталкивался с подобной задачей. Пробовал два подхода. 1. Создал Partition для модуля “l4” и пометил ее как Empty. Далее экспортировал root partition для всего top (включая пустую “l4”). Пытаюсь импортировать в другой проект подключив для l4 нужный исходник (или qxp) и получаю ошибку "Error (35013): Found unexpected partition in previously generated netlist with no corresponding partition definition in the current project". 2. Вместо модуля “l4” вставил blackbox, но partition не создавал. Экспортировал root partition. Далее успешно без ошибок импортировал в новый проект. Но модуль l4 не реагирует на подсунутый исходник, утилизация по нулям фактически его нет. Netlist type для импортированных partition – Post-Synthesis. Для сабмодуля l1 подход с Empty Partition работал как надо. Весь нетлист закрыт, но l1 на изменения исходника реагирует, я неделю ходил довольный, а потом попробовал провернуть тоже для более глубокой вложенности, но не вышло. Буду благодарен за идеи, что еще можно попробовать. Влад.

-

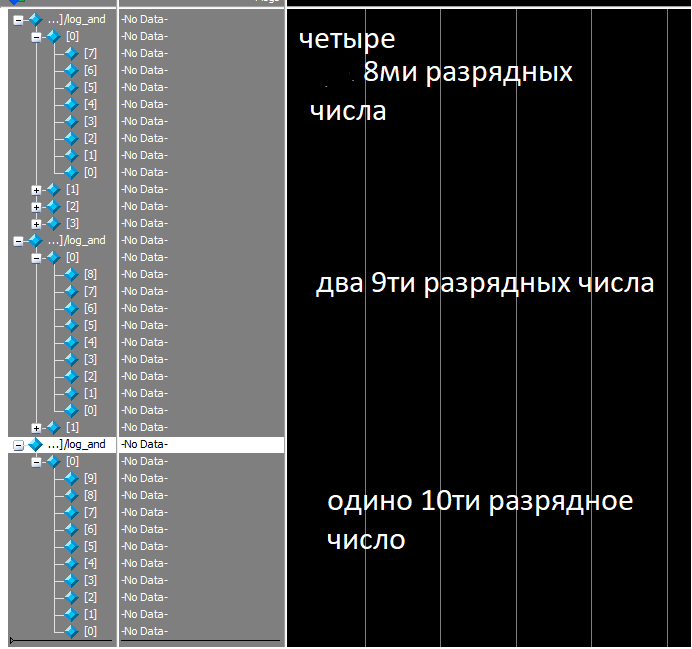

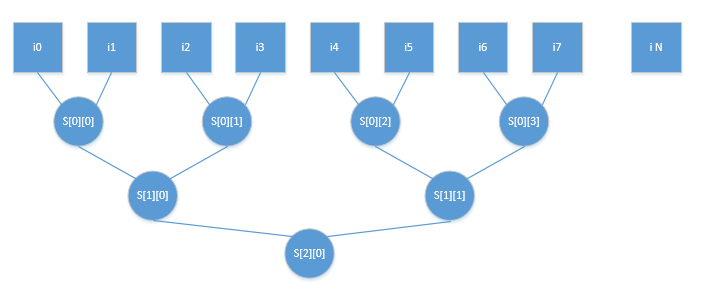

Опечатался когда переносил код на форум =( ошибка будет и при совпадении имен. Тоже об этом думал, но никак не мог сообразить как мне хитрые вычисления засунуть в range регистра. Ведь это получается как минимум цикл с делением и аккумулятором, в параметр таки вычисления уже не засунуть. А сейчас вернулся к этой идее, написал функцию расчета общего количества необходимых регистра и вызываю ее при декларировании параметра, такой способ работает. Но у него есть и минусы. Сейчас я хочу делать логическую операцию которая не влияет на разрядность числа. Но если строить такой конвейер с умножением или сложением, разрядность каждого следующего "слоя" растет. Если использовать метод объявления длинного вектора под все вычисления все их надо делать одной, максимальной разрядности. При способе с использованием generate у меня получилось создавать векторы разной длины с разными разрядностями, но к сожалению только в симуляторе... То есть если говорить в самом широком смысле, то идея была нагенерить вот таких регистров у которых варьируется как длина так и разрядность.

-

Хочу написать максимально параметризорованный синтезируемый модуль. Вход модуля это вектор произвольной длины: input wire [DATA_WIDTH-1:0] data[VECT_WIDTH]; Необходимо производить операции с парами входных wire, например логическое &. Пары "нулевой с первым", "второй с третьим" и тд. Результат также представляют собой вектор, с ним проделываем ту же операцию. Так продолжается пока вектор не выродится в одно число. Результат каждой логической операции записывается в регистр. Я хочу создать "reg S" зависящий от входной длины вектора, дальше в циклах записать что надо в этот регистр уже будет не сложно. Я общем виде S может любой. S[][][][][]... Написал следующий код: //генерируем массив регистров genvar gen_result; generate begin for ( gen_result = 1; gen_result < VECT_WIDTH/2; gen_result++ ) begin:gen_result_var reg [DATA_WIDTH-1:0] result[(VECT_WIDTH/2)]; //для примера просто (VECT_WIDTH/2), вообще надо при каждом проходе делить еще на 2 end end endgenerate //записываем один пробный регистр always @( posedge clk ) gen_summ_var[0].result[0] <= 1; В ModelSim все выглядит как надо. Но Quartus ругается. Во всей видимости мои хотелки не синтезируемы. Подскажите, как лучше решить такую задачу? Вдохновение черпал отсюда: https://www.hdlworks.com/hdl_corner/verilog_ref/items/Genvar.htm

-

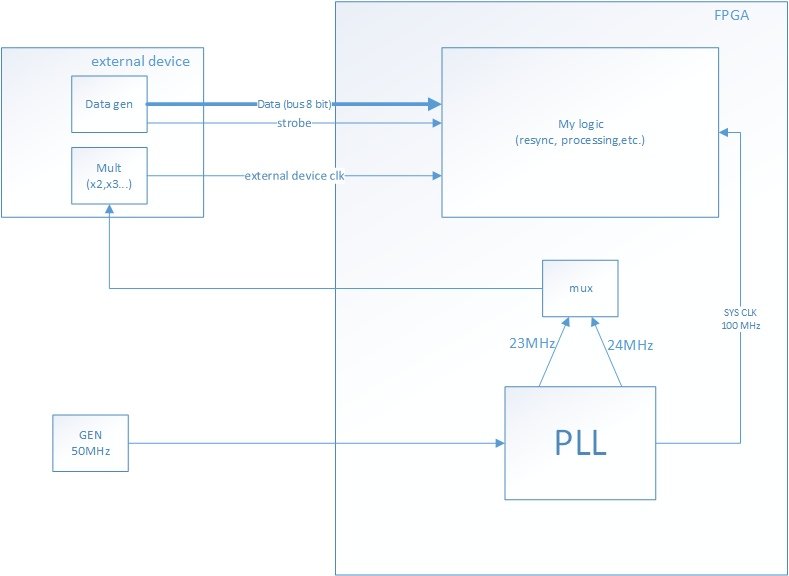

То есть моя первая мысль была правильная? Получается 4 асинхронных клока, на внешних устройствах виртуальные и в плис с ножек? //verilog input wire clk_dev_0_i , //клок с первого устройства input wire clk_dev_1_i , //клок с второго устройства input wire [7:0] dev_0_data , //данные с первого устройства input wire strb_0_data , //строб с первого устройства input wire [7:0] dev_1_data , //данные с второго устройства input wire strb_1_data , //строб с второго устройства #SDC #клоки на пинах create_clock -name {clk_dev_0_i} [get_ports {clk_dev_0_i}] -period 48MHz create_clock -name {clk_dev_1_i} [get_ports {clk_dev_1_i}] -period 48MHz #клоки на внешних устройствах create_clock -name virt_clk_dev_0_i -period 48MHz create_clock -name virt_clk_dev_1_i -period 48MHz #первое устройство set_input_delay -clock { virt_clk_dev_0_i } -max 2 [get_ports {dev_0_data[*]}] set_input_delay -clock { virt_clk_dev_0_i } -min -2 [get_ports {dev_0_data[*]}] set_input_delay -clock { virt_clk_dev_0_i } -max 2 [get_ports {strb_0_data}] set_input_delay -clock { virt_clk_dev_0_i } -min -2 [get_ports {strb_0_data}] #второе устройство set_input_delay -clock { virt_clk_dev_1_i } -max 2 [get_ports {dev_1_data[*]}] set_input_delay -clock { virt_clk_dev_1_i } -min -2 [get_ports {dev_1_data[*]}] set_input_delay -clock { virt_clk_dev_0_i } -max 2 [get_ports {strb_1_data}] set_input_delay -clock { virt_clk_dev_0_i } -min -2 [get_ports {strb_1_data}]

-

Добрый день Много думал и стал сомневаться Суть в следующем. Имеется отладочная плата с FPGA, к ней подключены два внешних устройства. На вход устройств необходимо подавать 24МГц, внутри каждого устройства эта частота умножается (коэффициент можно задать) и устройства начинают отправлять в FPGA данные. Данные передаются пачками по 8-битной шине и сопровождаются стробом. В FPGA пачки данных необходимо обрабатывать одновременно. Для этого заведены 2 FIFO, запись в них производится на частотах внешних устройств, вычитываем одновременно на системной частоте когда приняты обе пачки. Видимо из-за разницы в умножении частот, стробы постепенно начинают расползаться во времени и в итоге одно из FIFO переполняется, вся система рушится. Для борьбы с этим, на системной частоте отслеживаем начала стробов и когда они расползлись слишком сильно, переключаем частоту с 24МГц на 23.5 МГц для убегающего устройства, когда стробы выровнялись возвращаем обратно 24 МГц. Переключения производятся в момент, когда данных нет. Этот концепт работает, но при задании констрейнов я стал сомневаться. Суть сомнений в следующем. Сначала я просто задал виртуальный клок, для каждого из внешних устройств, задал клоки на входных пинах и прописал set_input_delay для сигналов в шине и для строба. То есть сделал как будто нет никакой связи внешнего клока и любых клоков в ПЛИС. Но это не совсем честно, связь то все-таки есть и отсюда началась путаница. Я попробовал задать клок для внешнего устройства как create_generated_clock. Умножив на 2 клок выхода с мультиплексора клоков. А точнее сделал два отдельных create_generated_clock для каждого выхода PLL с ключем –add, дальше так же прописал set_input_delay. Но теперь мне не нравятся оба варианта… Хотелось бы понять какой подход правильнее? И вообще, как лучше задать констрейны, для такого клока и входных данных с внешних устройств.

-

Еще добавлю, что можно почитать про "кольцевой буфер"

-

https://marsohod.org/projects/66-makeavr

-

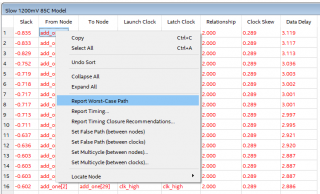

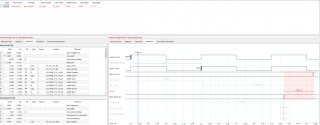

Добрый день! Подскажите есть ли в Vivado (использую 2017.2) возможность для просмотра временных ограничений на временной диаграмме? В Quartus щелкал "Report Worst-Case Path" и бед не знал, сейчас пересел на Vivado и жутко не привычны цифры слаков анализировать без визуализации. В Quartus это выглядело вот так:

-

Vivado 2016.4

Kapsik ответил Koluchiy тема в Среды разработки - обсуждаем САПРы

Добрый день! Что бы не плодить темы задам вопрос здесь. Есть возможность в Vivado из IP Catalog генерировать файлы Verilog? У меня все время получается vhd. В settings Target language выбран Verilog. -

Доброе утро! Тему прочитал, но не совсем понял в каком месте необходим НИОС? Там у вас какая-то обработка? Или задача стоит просто как Если так, то попробуйте взглянуть тут https://habrahabr.ru/post/283488/ . Тут чисто "аппаратно" реализовано Камера ->SDRAM(два буфера один пишем, другой читаем)->VGA.

-

Завести ТОП уровень в него поместить файл .v .vhd сгенерированный QSYS, а рядом ваши модули, соединяются HPS и рукописные модули по одному из мостов, для FPGA мосты видятся, как Avalon. Пины соответсвенно назначаете для вашей рукописной части. Получается такая штука: ваша программа в HPS по мосту например лайтвейт записывает в рукописный модуль по шине Avalon значение по адресу, ваш рукописный модуль это дело анализирует и зажигает светодиод.

-

Попробуйте "add wave *" заменить на do wave.do

-

Можно сделать так: достали все нужные сигналы, привели к нужному формату и сохраните wave.do. Потом при запуске симуляции вызывайте ваш wave, там все настройки должны остаться, как в момент сохранения.

-

Quartus шутник конечно. Сам сгенерировал .sdc для HPS, сам 1100 штук Warning "Ignored" выдал. Это нормально? Или что-то пошло не так?

-

Так, с этим вроде действительно все в порядке, обратить внимание на порядок скриптов это отличная идея. Вчера проводил опыт, все тело sdc оставил в одном файле, а последний констрейн перенес в другой. Во втором файле ставил нереальные значения ожидая слаков, но их не увидел, очень удивился и решил задать вопрос. Сейчас посмотрел в каком порядке файлы прикреплены. Квартус последний прикрепленный файл ставит на самый верх, на что я внимания не обратил, в итоге в TQ если делаем Read SDC File, он первым прочитает файл добавленный в проект последним, видимо из-за этого у меня и была проблема. Выход прикреплять SDC в проекту в нужном порядке или делать Read SDC File не для всех разом, а по одному в нужном порядке. Первый вопрос решен, andrew_b огромное спасибо :beer:

-

Несколько SDC файлов в проекте в Quartus

Kapsik опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день! Возникло два вопроса. 1. Как Quartus относится к нескольким SDC файлам подключенным к проектам? Если я часть констрейнов опишу в файле _1.sdc, а другую часть _2.sdc, прикрепляю их к проекту, как поведет себя Quartus? Один файл перезатрет другой, констрейны будут применяться последовательно из одного файла, а потом из другого или выберется какой-то один? 2. Констрейны для SOC. Есть проект в SOC Altera, QSYS автоматом генерит несколько SDC и прикрепляет их к проекту. Это исчерпывающие констрейны для HPS, с нас только описание FPGA части? Как мне добавить констрейны для своего дизайна FPGA, просто еще один файл .sdc прикрепить к проекту и Quartus все поймет? -

Вот тут можно посмотреть, глава "Асинхронные интерфейсы" в ней "Истинно асинхронные интерфейсы".

-

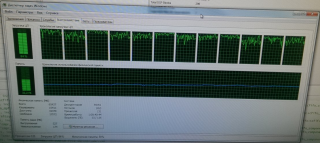

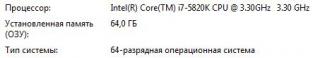

Смотрел и пришел к тем же выводам, единственное, что все таки 32Гб оперативы мне кажется предпочтительнее. У меня сейчас на локальном помпе 16 и на фиттере Quartus выгребает почти все, так что даже .doc параллельно править сложно. А так изредка запускаю несколько проектов параллельно, тогда конечно смысл есть. Да у меня такие же мысли были, что если только увеличить частоту. Но видимо игра свеч не стоит, лучше грамотно организовать инкрементальную компиляцию.

-

Добрый день! Задали мне тут вопрос, не хочу ли я отдать имеющийся ПК на другие нужды, а сам выберу другой. И вот я задался вопросом, а нужен ли мне другой и если да то какой? Я сказать по правде особых альтернатив нашему не вижу. Сейчас у нас Intel Core i7 с 64Гб оперативной памяти. Если кому-то необходимо собрать увесистый проект, то по удаленке исходники закидываются на этот комп с локального и там собираются. Среда - Quartus Prime 15.1. Надеюсь и дальше будем обновляться. Чипы - Arria V, Cyclone V. Тут все может меняться в зависимости от задач. Сейчас сборка занимает от часа до двух, в зависимости от настройки Quartus. Какое железо можете порекомендовать для ускорения работы? Имеет ли смысл искать или особого прогресса ждать не стоит?

-

Вот такой диалог с альтера саппорт из которого я делаю вывод, что ничего лишнего крепить не надо. Если есть логик локи, партишны то все это экспортируется в .qxp(прикрепляется в системе контроля версий или передается вручную), а потом импортируется обратно. Мой вопрос Dear, your answers really help me! I think it is last question to you. My colleague wants to get the folder "incremental_db" from me (for use my IP CORE with Design Partition and LogicLock Region). I think, I can give him only the .qxp without "incremental_db" folder and he will be happy. Am I right? He doesn't belive me. I would like to show him your (Altera support) answer about this situation. Их ответ Perhaps you can ask your friend why he need the incremental_db folder. And you can refer him to Quartus handbook as well. Let me give you some references. As per my understanding your friend need to integrate your IP in the top level project. As per Quartus handbook Topic “Exporting Design Partitions from Separate Quartus Prime Projects” Partitions that are developed by other designers or team members in the same company or third-party IP providers can be exported as design partitions to a Quartus Prime Exported Partition File (.qxp), and then integrated into a top-level design. A .qxp is a binary file that contains compilation results describing the exported design partition and includes a post-synthesis netlist, a post-fit netlist, or both, and a set of assignments, sometimes including LogicLock placement constraints. The .qxp does not contain the source design files from the original Quartus Prime project I hope this clarifies the .qxp includes information of your Logic lock regions and Design partitions. Now on your friend side since he want to integrate your IP in his design. There are few things you need to take care. For example Logic lock region he reserved for your IP must be same as what you used. To see more details on this, refer to Quartus handbook topic “Preparing the Top-Level Design” Please let me know if this helps. Thanks, Regards

-

У нас сейчас с коллегой горячий спор, надо ли таскать за собой (совать в git) и передавать от разработчика к разработчику эту несчастную incremental_db. Я против, но на все 100 к сожалению не уверен. Перечитал уже довольна много инфы но однозначный ответ не нашел. Но во многих источниках, при всякого рода глюках первым делам рекомендуют чистить incremental_db и db.

-

А их надо подсасывать? Или если incrememntal_db удалена то они на основании других файлов сгенерятся снова и лягут в новую incrememntal_db?

-

Еще вопрос. Папки db и incremental_db могут вялятся неотъемлемой частью проекта без которой Quartus не сможет собрать проект или это всегда результат работы Quartus? Могу ли я удалить папки db и incremental_db и после этого всегда успешно собрать проект или если в проекте были заданы LogicLock и/или Partition или что-то еще, то без этой папки уже не обойтись?