popeye

Свой-

Постов

91 -

Зарегистрирован

-

Посещение

Весь контент popeye

-

А Вы уверены, что второй колбэк есть в HAL для STM32F1xx?

-

Имеется процессор STM32F407, работающий тулчейн из GCC ARM, OpenOCD, gdb и Eclipse на linux-машине, отладчик Segger J-Trace. Интересует трассировка инструкций в реальном времени (instruction trace). В IAR ARM EW работает, думаю, что в Atollic TrueSTUDIO и Keil MDK тоже будет работать, но это всё под windows. А можно ли сделать тo же под linux?

-

Ребята, ну если не удаётся исправить кракозябры в заголовке письма, то, может, хотя бы поправить ELECTONIX.ru?

-

Для функциональной симуляции я один раз (для каждой новой версии квартуса или моделсима) компилирую файлы 220model.v и altera_mf.v в отдельную библиотеку и подцепляю её к vsim ключом -L. Если требуется инициализация памяти, то использую hex-файлы, - моделсим их понимает напрямую.

-

Возьмите любое видео (только не wmv) и VirtualDub и делайте себе клипы на любой вкус, а также формат, кодек и фреймрейт.

-

Возможно, у Вас есть слой логики перед регистром для IOE, в этом случае Quartus не может поместить этот регистр в IOE.

-

А что Вас удивляет в пункте 1? Вы берете 2-ой, 4-ый и 8-ой элементы вектора b (нули) и складываете с вектором a, результатом чего является вектор [1 2 3 4], а потом делаете присваивание выбранным элементам. 4-ый элемент получает значение дважды, поэтому значение 2 перезаписывается тройкой. Всё правильно.

-

Может это глупый вопрос, а Вы код для своей alt_timestamp_start создали?

-

Волощенко Если Вы хотите использовать timestamp таймер, то нужно написать строчку: #include "sys/alt_timestamp.h" Никаких си файлов инклюдить не надо.

-

Констрейны в Quartus

popeye ответил BSV тема в Среды разработки - обсуждаем САПРы

Насколько я помню, в ACEX можно использовать либо Fast Input Register, либо Fast Output Register, но не одновременно. Вот фраза из мануала: An IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time or as an output register for data that requires fast clock-to-output performance. -

-env <path> Specifies a hierarchical context for the signal names in <expressionString> so they don't all have to be full paths. Optional. -install <path> Causes the newly-created signal to become a child of the specified region.

-

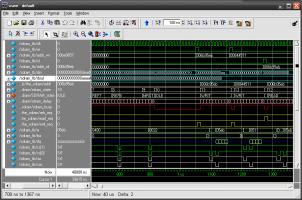

Вот мой пример с верилогом, SDRAM контроллер. Файл wave.do: onerror {resume} quietly WaveActivateNextPane {} 0 virtual type { PALL REF1 REF2 REF3 REF4 REF5 REF6 REF7 REF8 MRST IDLE REFR READ WRIT} sdram_state_type quietly virtual function -install /sdram_tb/the_sdram -env /sdram_tb { (sdram_state_type) /sdram_tb/the_sdram/sdram_state} SDRAM_state add wave -noupdate -format Logic /sdram_tb/clk add wave -noupdate -format Logic /sdram_tb/wr ... add wave -noupdate -color Pink -format Literal -radix unsigned /sdram_tb/the_sdram/sdram_state add wave -noupdate -format Literal /sdram_tb/the_sdram/SDRAM_state ... Отратите внимание на сигналы sdram_state и SDRAM_state. Кусок из верилога: // SDRAM state machine names parameter PALL = 0; parameter REF1 = 1; parameter REF2 = 2; parameter REF3 = 3; parameter REF4 = 4; parameter REF5 = 5; parameter REF6 = 6; parameter REF7 = 7; parameter REF8 = 8; parameter MRST = 9; parameter IDLE = 10; parameter REFR = 11; parameter READ = 12; parameter WRIT = 13; Вот скрин из моделсима.

-

NIOS и Modelsim

popeye ответил ChinasFanat тема в Среды разработки - обсуждаем САПРы

Система с Ниосом замечательно моделируется в МоделСиме целиком при условии, что SOPC Builder генерит незашифрованный HDL. Ну или зашифрованный, но у Вас есть декриптор). -

Девайс "электронная бумага"

popeye ответил PsM тема в В помощь начинающему

Заиметь отладочный кит стоит $3000, собственно девайс с таким экраном (джинку) ~10000 руб. в Москве. -

Сделайте падстак для нужного переходного, у которого площадки определены только в нужных слоях, например TOP и INNER1, а в ненужных поставьте undefined.

-

Увидев тему по Layout, созданную Vinnetu, не поверил своим глазам: разве есть что-то, чего не знает Vinnetu? Ведь сколько раз я уже читал толковые советы и ответы Vinnetu касательно Layout на этом форуме. Открыл тему и убедился, что все в порядке. :a14:

-

Вам надо нажать кнопочку N, ввести туда, например, DAC[7..0], нажать OK, щелкнуть по Вашей безымянной шине (которую Capture обозвал как N2927739) и будет Вам счастье. :tongue: А лучше всего, как уже посоветовали, стереть эту некрасивую жирную линию нафиг :) вместе с ответвлениями и оставить только wires.

-

Назначьте Вашему регистру параметр Multicycle = 3 в Quartus или назначьте Clock Enable Mylticycle регистру, который формирует enable.

-

КАК загрузить EPC1

popeye ответил mobius тема в Работаем с ПЛИС, области применения, выбор

Это решение работает. -

Спасибо за ответы. prototype Специально не хотел лезть в Router, искал в Layout. Nixon & Vadim Vadim прав: переливка полигонов не помогла. Fellow Я понял, что надо было поиграться с настройками Miter Ratio в опциях, тогда бы получилось, а поскольку стороны прямых углов были небольшими, то Add Miter ничего не делал. Это опыт OrCad Layout. А для чего нужна статистика тогда? Если она есть, то можно посмотреть и сделать выводы. Я сделал и выводы меня удивили, в связи с чем и возник вопрос. Кстати я делал отключение цвета всего, кроме соединений, и видел только одно соединение между медным планом и переходным, которое явно было в трассировке, а статистика сообщала о нескольких десятках неразведенных цепей. Про то, что делает Tools/Verify Design/Connectivity, я не знал, т.к. это мой первый опыт работы с PADS Layout, а посмотреть мануал поленился, увидев окошко No errors found.

-

"Чистка" разводки в PADS Layout

popeye опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Есть ли возможность в PADS Layout автоматически сгладить прямые углы проводников на всей плате, появившиеся в результате динамической трассировки (аналог cleanup design из OrCad)? И еще вопрос: после разводки платы делаю Reports->Statistics и вижу, что есть много неразведенных цепей (unrouted + partials), хотя все разведено, как это понимать/бороться? -

Модули ОЗУ, а также отдельные микросхемы стандартизованы JEDEC. На их сайте есть вся информация о цоколевках, логике работы и SPD. Производители SDRAM в свои даташиты перепечатывают по сути стандарт. С модулем работать точно так же, как и с отдельной микросхемой, с учетом ширины шины. Рефреш определяется комбинацией сигналов на линиях управления, так что ничего кроме контроллера не понадобится. Если будете работать с модулем, то есть одна проблемка: Вам потребуется читать SPD-память и соответствующим образом настраивать Ваш контроллер SDRAM. Еще момент, DIMM модули, конечно, достаются легко, а вот разъемы для них не очень легко. Производителей SDRAM просто море, скачаете даташит с упомянутого ранее Samsung'а, и у Вас будет вся нужная информация.

-

Если так нужен схемный ввод, то воспользуйтесь средствами ввода третьих фирм и сконвертируйте в HDL для Warp'а. Лично я этим не пользовался, поскольку пишу на HDL, но тот же Quartus позволяет это сделать. Если не ошибаюсь, подойдет ActiveHDL. У меня был опыт работы с Delta 39K и Warp 6.3, а теперь я забыл про сайпресс и очень этому рад. :) А насчет дороговизны альтеры, Вы, по-моему, погорячились. $1,5 за CPLD с 32 макроячейками или $15 за FPGA с 5000 логических элементов, PLL, аппаратными умножителями и кучей памяти - это дорого?

-

Warp - это софт для синтеза и фиттинга. Последняя версия, если не ошибаюсь, 6.3, а дальше Cypress отказался от поддержки. ISR - это софт для работы с JTAG, конфигурация, прошивка и пр. Этого софта достаточно для проектирования, да и без него, по-моему, все равно не обойтись.

-

Я столкнулся с этим впервые в Quartus II 5.x. Насколько я понял, дело в том, что когда проходит процесс конфигурации ПЛИС через SignalTap, то конфигурация на самом деле не происходит, хотя Quartus говорит, что все ОК. У меня еще это выражается в том, что вместо надписи "Ready to acquire" после конфигурации снова появляется "Program Device To Continue". Победить это я не смог, увы. От саппорта Альтеры добиться вразумительного ответа не получилось, а помогают "танцы с бубном" и перезагрузка компа. Попробуйте конфигурить через EPCS, чтобы убедиться, что сама ПЛИС в порядке, SignalTap можно и отключить, а можно и нет. Если будет все нормально, то придется бодаться с глюками SignalTap'а.