Faton_11

Участник-

Постов

156 -

Зарегистрирован

-

Посещение

Весь контент Faton_11

-

да, теперь понятно. получилось, спасибо!

-

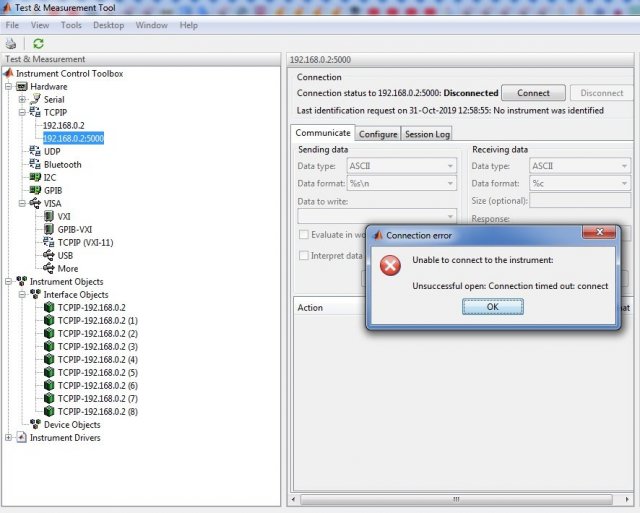

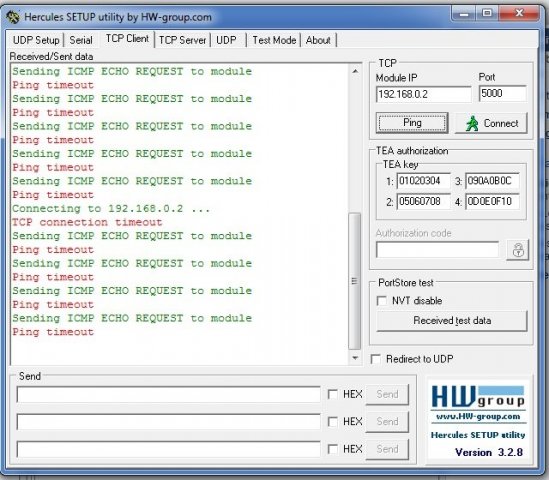

Теперь IP-адрес модуля 192.168.1.2 ,Порт 5000. IP-адрес ПК 192.168.1.100 После нажатия кнопки "Connect" в Hercules: После нажатия кнопки "Connect" в Matlab:

-

все отключено, антивирус тоже

-

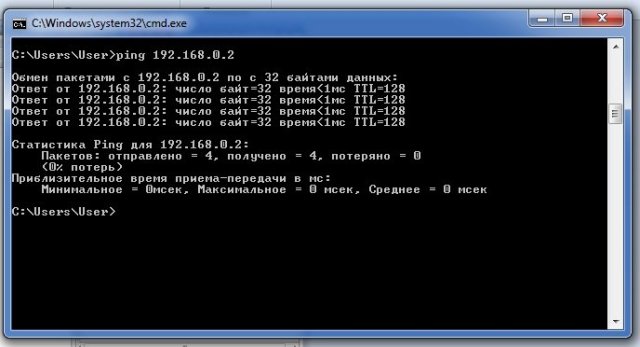

спасибо за ответы!) для наглядности прикрепляю картинки. Модуль пингуется через командную строку , но команда Ping не проходит через другой терминал Ну и в матлабе соединение не устанавливается тоже

-

спасибо за ответ! тогда немного предыстории: подключаю модуль wiznet 5500 на этапе "сервер слушает клиента", т.е. регистр Sn_SR (Socket n Status Register) находится в состоянии "SOCK_LISTEN". Теперь сокет ждет SYN-пакет от TCP-клиента. Если пакет будет успешно принят, регистр Sn_SR сменит состояние на "SOCK_ESTALBLISHED". Так вот, получается, модуль ждет SYN-пакет, а я не знаю каким образом его отправить, посредством чего, и можно ли будет проследить это в снифере?

-

matlab не отправляет arp-запрос

Faton_11 опубликовал тема в Вопросы системного уровня проектирования

Добрый день!Пытаюсь передавать данные через matlab между ПК (клиентом) и Ethernet -модулем(сервером), соответственно по Ethernet кабелю. Клиент должен отправлять arp-запрос модулю, но в сниффере видно, что никакие запросы со стороны Matlab не отправляются.Клиент в матлабе выглядит так: t = tcpip( 'localhost',50502, 'NetworkRole', 'client'); set(t, 'TimeOut',600); fopen(t); data = fread(t, 10); Видимо, этого кода не достаточно и должно быть что-то ещё. Подскажите, пожалуйста, что я делаю не так, и как сделать чтобы matlab все же отправлял arp-запросы? -

Wiznet 5500 не отвечает

Faton_11 ответил Faton_11 тема в Интерфейсы

Вам ведь ответ был самому первому) а знание того, что фирменный драйвер делает, для меня ясности не очень добавило( в общем, Вы были правы. Это все кривой сброс, теперь, кажется, отвечает. Спасибо! =) и спасибо всем за ответы!=) -

Wiznet 5500 не отвечает

Faton_11 ответил Faton_11 тема в Интерфейсы

-

Wiznet 5500 не отвечает

Faton_11 ответил Faton_11 тема в Интерфейсы

с задним фронтом же меняется. извиняюсь за качество фото: камера не очень. но если и по спаду защелкивать, то снова ничего( -

Wiznet 5500 не отвечает

Faton_11 ответил Faton_11 тема в Интерфейсы

Прикрепляю фото с нулевыми данными. Передаю значение 00000000_00011010_00000001_00000000, где биты [31:16] - это адрес считываемого регистра, [15:8] - контрольный байт: - нули в [15:11] означают, что обращаемся к общему регистру (есть ещё регистры для настройки каждого сокета) - "0" в бите [10] означает, что режим "чтение" - "01" в [9:8] означает что в кадре только 1 байт данных ("Fixed Data Length Mode , 1 Byte Data Length (N = 1)") [7:0] - байт данных в режиме записи. -

Wiznet 5500 не отвечает

Faton_11 опубликовал тема в Интерфейсы

Добрый день! Имеется модуль Ethernet W5500, управляю им с ПЛИС. Хочу считать состояния регистров по SPI, но модуль молчит( Например, пытаюсь считать RTR-регистр по адресу 0x001A, где по умолчанию должно быть значение D0. Перед тем как отправлять, делаю сброс через ногу, выведенную на разъем. Ниже прикрепляю диаграмму (синий - МOSI, желтый - SCLK, розовый - SCS, зеленый - MISO). Подскажите, что я делаю не так? -

проблемы с SignalTap

Faton_11 ответил Faton_11 тема в Среды разработки - обсуждаем САПРы

хорошо, спасибо за советы и простите за долгий ответ. А бег с криками про мистику разве что помогает окончательно не впасть в отчаяние=) -

проблемы с SignalTap

Faton_11 ответил Faton_11 тема в Среды разработки - обсуждаем САПРы

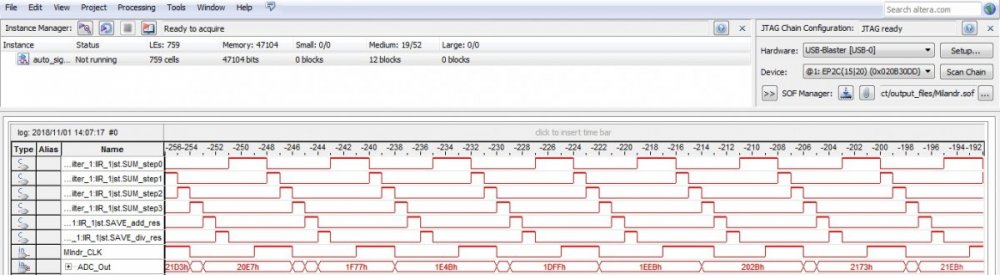

Понимаю, что там асинхронщина, но не понимаю как в данном случае она влияет? Смотрю на анализаторе: данные ADC_Out, поступающие в ПЛИС, защелкиваются по фронту сигнала Mlndr_CLK. В состоянии SUM_step0, предположим, первый дребезг фронта клока отлавливается и происходит переход в следующее состояние. Автомат успевает проходить все состояния до нового фронта Mlndr_CLK. Что в моих рассуждениях неверно?) -

проблемы с SignalTap

Faton_11 ответил Faton_11 тема в Среды разработки - обсуждаем САПРы

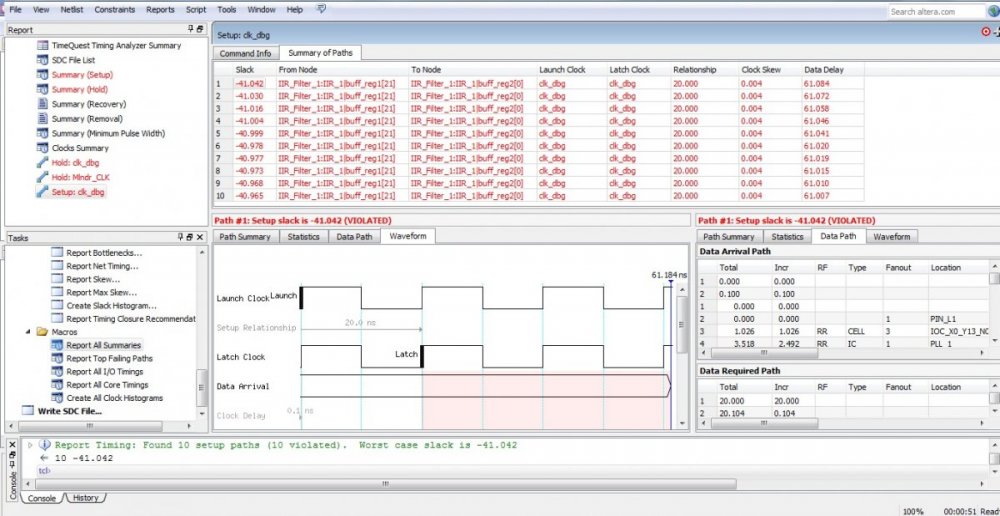

я не против грамотного заполнения SDC, только вот с этим совсем все плохо, и вот тому пример: В проекте есть следующие клоки : - Mlndr_CLK - клок, идущий с внешнего генератора на порт общего назначения ПЛИС и равный 12.5 МHz; - clk_dbg - клок с генератора, установленного на отладочной плате (Сyclone II FPGA Starter Board) и равный 50 МHz; - PLLclk – клок с выхода мегафункции PLL равный 100 MHZ (на входе PLL - clk_dbg) Данные поступают на вход модуля цифрового фильтра по клоку Mlndr_CLK, арифметика вычисляется на более "быстром" клоке - PLLclk always@(posedge PLLclk) case(st) SUM_step0: begin begin if (Mlndr_CLK) st=SUM_step1; else st=SUM_step0; end begin //арифметика.. end end ....... //арифметика.... SUM_step3: begin gnrt2[4].add_dataa=gnrt2[1].add_res; gnrt2[4].add_datab=gnrt_mult[8].mult_res; st=SAVE_add_res; end SAVE_add_res: st=SAVE_div_res; SAVE_div_res: st=SUM_step0; default: st=SUM_step0; endcase //_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ always @ (posedge PLLclk) if (st==SAVE_add_res) buff_reg1=gnrt2[4].add_res; //_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ always @ (posedge PLLclk) if (st==SAVE_div_res) buff_reg2=quotient_bx[ADC_WIDTH-1:0]; //_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ always @ (posedge Mlndr_CLK) dataout=buff_reg2; // выходные данные, идущие наружу модуля , где gnrt2[4].add_res - результат вычислений с выхода мегафункции сумматора (находится в блоке generate): Adder_bx addr_bx (add_dataa,add_datab,add_res); этот результат сохраняется в регистре buff_reg1 и затем поступает на мегафункцию делителя: Div div_rounding_bx(denom, buff_reg1,quotient_bx,remain_bx); результат сохраняется в регистре buff_reg2, затем по фронту "медленного" клока Mlndr_CLK, подается на выход модуля TimeQuest выдает сплошные "слэки" (см. прикрепленный файл). Констрейны, собственно, такие: create_clock -name Mlndr_CLK -period 12.5MHz [get_ports {Mlndr_CLK}] create_clock -name clk_dbg -period 50MHz [get_ports {clk_dbg}] create_generated_clock -name PLLclk -source [get_ports {clk_dbg}] -multiply_by 2 -duty_cycle 50 (видимо, для PLL ещё нужно указать параметр "[get_pins{.....]}]", но в выпадающем списке пинов ничего подходящего не было( Чем можно эти слэки исправить и почему в отчете Timequest-a в качестве launch и latch клоков стоит clk_dbg, а не PLLclk? -

проблемы с SignalTap

Faton_11 ответил Faton_11 тема в Среды разработки - обсуждаем САПРы

andrew_b, вот как раз с констрейнтами вожусь, спасибо! iosifk, а как научились?) Тоже в основном удавалось решать проблему констрейнтами? -

проблемы с SignalTap

Faton_11 опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день, дорогие форумчане! Пришлось столкнуться со следующей проблемой: проект работает только если после прошивки ПЛИС в окне SignalTap нажать "Program Device" (если не нажать, то и сам анализатор не запустится, и проект корректно работать не будет. Точнее будет, но такое ощущение, что как при другом варианте прошивки=/). Если в настройках отключить галочку "enable SignalTap II logic analyzer", то проект тоже корректно работать не будет. Может кто-то сталкивался, в чем тут может быть дело? -

generate внутри case

Faton_11 ответил Faton_11 тема в Языки проектирования на ПЛИС (FPGA)

Спасибо, Rob! :rolleyes: -

generate внутри case

Faton_11 ответил Faton_11 тема в Языки проектирования на ПЛИС (FPGA)

Прошу прощения за долгий ответ. В итоге пришлось сделать в лоб, т.к. в цикле for к экземплярам модулей, созданных в generate, нельзя обращаться через переменную, объявленную как integer. genvar j; generate for( j=0; j<(ORDER/2+1); j=j+1) begin:gnrt2 reg [39:0] add_dataa; reg [39:0] add_datab; wire [39:0] add_res; Adder addr (add_dataa,add_datab,add_res); end endgenerate //________________________________________________________________________________ genvar j; generate for( j=0; j<(ORDER+1); j=j+1) begin:gnrt2 reg [10:0] mult_dataa; reg [10:0] mult_datab; wire [39:0] mult_res; Mult mlt ( mult_dataa, mult_datab, mult_res); end endgenerate //________________________________________________________________________________ integer k; always@(posedge clk) case(st) SUM_step0: begin for(k=0; k<26; k=k+1) begin gnrt2[k].add_dataa=gnrt[2*k].mult_res; gnrt2[k].add_datab=gnrt[2*k+1].mult_res; end st=SUM_step0; end default: st=SUM_step0; endcase Но было бы очень интересно знать на будущее, как это обойти -

generate внутри case

Faton_11 ответил Faton_11 тема в Языки проектирования на ПЛИС (FPGA)

RobFPGA и alexadmin, спасибо большое за ответы! Тогда подскажите, пожалуйста, какую штуку надо использовать, чтобы не прописывать "в лоб", как показано ниже always@(posedge clk) if (rst) st=SUM_step0; else case(st) SUM_step0: begin gnrt2[0].add_dataa=gnrt[0].mult_res; gnrt2[0].add_datab=gnrt[1].mult_res; gnrt2[1].add_dataa=gnrt[2].mult_res; gnrt2[1].add_datab=gnrt[3].mult_res; gnrt2[2].add_dataa=gnrt[4].mult_res; gnrt2[2].add_datab=gnrt[5].mult_res; default: st=SUM_step0; end endcase , а через некую k, что-то типа такого: gnrt2[k].add_dataa=gnrt[2*k].mult_res; gnrt2[k].add_datab=gnrt[2*k+1].mult_res; Если использовать цикл for, то это не будет выполнять в одном такте -

generate внутри case

Faton_11 опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! Скажите, пожалуйста, можно ли использовать generate внутри конструкции case? Квартус ругается, говорит, что end-а нет, но если закомментировать код от "generate" до "endgenerate" включительно, все нормально. Ниже приведен пример куска подобного кода. gnrt2[k].add_dataa, gnrt2[k].add_datab - входы сумматоров (использовалась мегафункция сумматора); gnrt[k].mult_res- выходы умножителей (использовалась мегафункция умножителя) parameter SUM_step0=0; genvar k; reg [2:0]st; always@(posedge clk) if (rst) st=SUM_step0; else case(st) SUM_step0: begin generate for(k=0; k<(ORDER/2); k=k+1) begin:gnrt3 gnrt2[k].add_dataa=gnrt[2*k].mult_res; gnrt2[k].add_datab=gnrt[2*k+1].mult_res; end endgenerate st=SUM_step0; end default: st=SUM_step0; endcase Заранее спасибо за ответ! -

Вопросы по Agilent ADS

Faton_11 ответил Halo_Gen тема в RF & Microwave Design

Добрый день! При создании фильтра на микрополосках график на схеме и график после переноса на Layout имеют разный вид. При этом подложку импортирую на layout со схемы. Почему график меняется, и как получить один и тот же вид? -

Вопросы по Agilent ADS

Faton_11 ответил Halo_Gen тема в RF & Microwave Design

Добрый день! Была импортирована спайс модель, но при запуске симуляции возникает ошибка: Error detected by hpeesofsim during netlist parsing. ADS-syntax parser error in '<ADS netlist>', line 43: syntax error подскажите, пожалуйста, как можно исправить эту проблему -

Вопросы по Agilent ADS

Faton_11 ответил Halo_Gen тема в RF & Microwave Design

Добрый вечер! Вопрос такой: при симуляции в EM Model возникает следующая ошибка: "..ERROR: The EM model is inconsistent with the layout: Partitioning: top level libcellview changed from v4_lib:cell_2:layout to v4_lib:cell_3:layout Edit and save the EM state file to correct this. Error detected by hpeesofsim during TRAN analysis 'Tran1'. Fatal error occurred while evaluating model `MomCmpt', instance `I__0.em_data'. " Кто-нибудь знает как с ней бороться? =( -

Вопросы по Agilent ADS

Faton_11 ответил Halo_Gen тема в RF & Microwave Design

Добрый вечер! Симуляция запускается на одном компьютере и не запускается на другом. Было ли у кого-нибудь так и как это вообще возможно? -

netlist

Faton_11 ответил Faton_11 тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Экспортирую схему > изменяю схему > импортирую старую схему > появляется схема в разделе blocks > не вижу изменений на схеме даже после перезапуска дизайнера. Каким должен быть результат?

.thumb.jpg.61d383d3ca223a6ee0373ce2e41422e9.jpg)

.thumb.jpg.7a05c64adf1802e1feea3e1dcb7d0505.jpg)