Faton_11

Участник-

Постов

156 -

Зарегистрирован

-

Посещение

Весь контент Faton_11

-

В регистр Sn_IR нужно записать в соответствующий бит единицу: ENABLE_INTERRUPT_Sn_IR = 32'b00000000_00000010_00101100_00000100; // ENABLE INTERRUPT Sn_IR

-

проблема решилась, спасибо

-

Добрый вечер! Кто с wiznet5500 работал, скажите, пожалуйста, как сигнал прерывания INT после первого срабатывания вернуть снова в состояние высокого уровня: а то он как лег, так и лежит, на последующие прерывания не реагирует (использую прерывание RECV, оно возникает при каждом получении данных от участника сети). После прерывания в соответствующий бит регистра SIR устанавливается "1", попытка насильно записать туда "0" не оканчивается успехом. В документации сказано "Каждый разряд SIR будет равен ‘1’ до тех пор, пока хост не очистит Sn_IR", а он его и не собирается очищать. Как быть?🤷🏻♂️

-

прием на wiznet5500

Faton_11 опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый вечер! -

4. да, точно. Теперь с этим понятно, большое спасибо! ошибки памяти больше нет! правда, на пк все равно ничего не приходит, а лампочка передачи разъема ethernet не радует своим миганием. __________________________________________________ это для случая "просто поморгать", да: text data bss dec hex filename 2720 288 3128 6136 17f8 application.elf а это после добавления ethlite : text data bss dec hex filename 90440 1436 750956 842832 cdc50 a_appli.elf

-

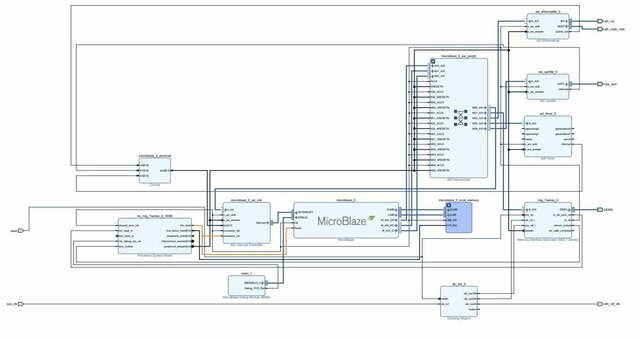

тогда конечно ладно.. 4. все еще не понимаю почему ddr не используется, и на что вы намекаете гарвардской архитектурой. Чем моя схема принципиально отличается от этой -> arty_top.pdf (она собрана по этому туториалу: Microblaze & Ethernet on ARTY A7 - YouTube, только у меня плис xc7a35tcsg324, а не xc7a100tcsg324). При этом блок ddr на ней, судя по всему, рабочий. Это что касается ddr. И вопрос про bram. Хотя в моей ПЛИС меньше логических ячеек, параметр local memory микроблейза в вышеупомянутом туториале выставляют так же на 32 KB и им всего хватает. При этом когда запускаю схему в vitis, там тоже ошибка с памятью: Error while launching program: Memory write error at 0x80000200. MicroBlaze instruction insert overrun Не понимаю в чем дело. Можете, пожалуйста, ответить на эти очевидные (но не мне) вопросы? ___________________________________ Р.S. ) Перекрестившись, заглядываю в файл. там это: text data bss dec hex filename 2720 288 3128 6136 17f8 application.elf

-

.. видимо этот форум предназначен для того, чтобы разного рода умники пыжались друг перед другом, какие они крутые

-

этот тул отдельно нужно скачивать? И куда вбить команду arm-none-eabi-size, консоль в vitis только на вывод сообщений, так же, как и debug console.. Если посмотреть размер файлов в папке debug: application.elf = 99 968 байт, application.elf.size = 111 байт это не то?

-

в vitis, мое приложение -> src -> main.c -> properties ..

-

наверно то, что код не лезет. Для BRAM нельзя каким-то образом сделать значение больше того максимального, что указано в настройках микроблэйза (local memory)?

-

программа "моргания лампочкой = 1 668 bytes, память БРАМ = 128 KB, 128 KB / 1 668 ~ 77

-

Память микроблэйз

Faton_11 опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день! Собираю блок-схему на микроблэйз: top.pdf Отдельно микроблэйз работает (проверено светодиодом). дальше добавляю блоки ethernetlite и тут он ругается, что недостаточно памяти. Меняю в настройках процессора local memory = 128 kb. Снова не хватает. Добавляю DDR3, опять ругается: region `microblaze_0_local_memory_ilmb_bram_if_cntlr_Mem_microblaze_0_local_memory_dlmb_bram_if_cntlr_Mem' overflowed by 711848 bytes collect2.exe: error: ld returned 1 exit status make: *** [makefile:38: apply2.elf] Error 1 При этом, я так понимаю, на DDR ему все равно, её он не использует. Если в vivado запустить Ila, строб init_calib_complite все время в единичке. Что не так с DDR? И можно ли сделать без нее, если увеличить BRAM ? -

всем спасибо!

-

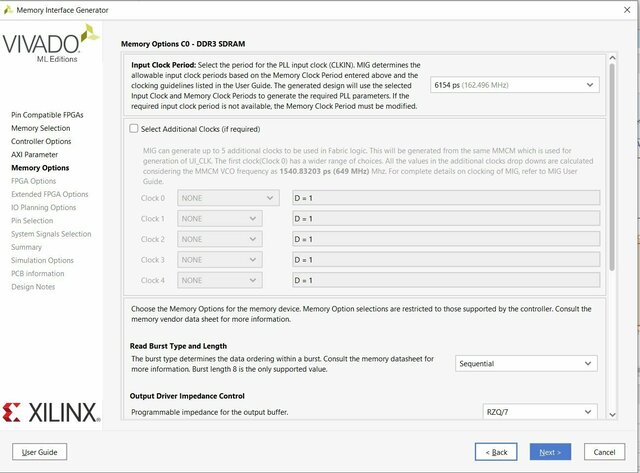

Теперь sys_clock на mig 7 = 200 МГц, в настройках ref_clock стоит "use sys clock": появляется ошибка "Error while launching program: fpga configuration failed. DONE PIN is not HIGH fpga configuration failed. DONE PIN is not HIGH". Добавляю ILA ничего больше не меняя - опять сообщение, что микроблэйз в ресете. top2.pdf А как сигналы с ILA в Vitis посмотреть? Если вывести init_calib_complete на светодиод, не горит (либо быстро моргнул. что вряд ли)

-

Добрый день! В vitis запускаю проект и получаю ошибку "MicroBlaze is under RESET". reset выведен на переключатель. Блок схема приведена ниже top1.pdf Если вывести reset микроблейза на переключатель напрямую, результат тот же: top2.pdf Возможно, что дело в неправильно настроенной частоте? Сейчас входной клок 162, 496 Mhz Спросить больше не у кого, спасибо

-

Конечно смутили. Но создание аналогичного пути без оных не помогло. Нужно эту важную папку переименовать? Надеюсь, обойдется без катастрофических последствий😦

-

Добрый вечер! Проблема в следующем. Когда хочу открыть настройки ядра MIG 7 Series в блочном дизайне, получаю сообщение: Вивадо установлен не в директорию по умолчанию, а на диск D. Копирование папки D:\.... \Vivado\2022.1\data\ip в папку с файлом проекта .xpr не помогло. Так же при запуске проекта получаю следующее сообщение: Тут видимо, из-за того, что Вивадо установлен не в директорию по умолчанию, репозиторий считается пользовательским. Вопрос в том, как открыть настройки ядра MIG 7 Series в блочном дизайне?

-

Анализатор ILA

Faton_11 ответил Faton_11 тема в Работаем с ПЛИС, области применения, выбор

Вроде что-то стало понятным, даже сигналы появились, спасибо! Надеюсь на это, хотя пока мне так вообще не кажется 🙂 -

Анализатор ILA

Faton_11 ответил Faton_11 тема в Работаем с ПЛИС, области применения, выбор

спасибо за ответ! Хочу mdio, mdc выдернуть из закрытого ядра и посмотреть анализатором. Эти сигналы внутри нередактируемого модуля проходят через OBUF. Насколько понимаю, после этого буфера они должны идти наружу плис. Если направить их в top-модуле в другой модуль дебаггера, выдает error: [DRC REQP-127] obuf_loaded: OBUF trimac_fifo_block/trimac_sup_block/tri_mode_ethernet_mac_i/inst/mii_interface/mdc_obuf_i pin O drives one or more invalid loads. The loads are: dbg/mdc_reg_reg такие дела -

Анализатор ILA

Faton_11 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Пытаюсь подключить ILA (внутренний логический анализатор) для xilinx. В интернетах пишут, что ILA не может получить доступ к выводам, торчащим из ПЛИС (порты "is not vivado-debuggable"), тогда как быть, есть ли обходные пути? Многого ли можно добиться от этого ILA? К примеру, SignalTap того же квартуса был простым и понятным. Такое ощущение, что проще забить и тыкать осциллом? -

Спасибо за объяснения! Документации благо полно, буду читать)

-

Если клоку присвоить тип LVDS25, а всем остальным ножкам проекта LVCMOS25, то ошибки не будет) Но вот вопрос: если в этом банке оставить 2.5-вольтовые ножки, а ножкам других банков присвоить тип LVDS33, то снова ругается. Это потому что в других банках нет своего отдельного тактирования, а используется все тот же клок, я правильно понимаю? спасибо за помощь!

-

Сейчас не у компа нахожусь. Когда доберусь до него, посмотрю и отпишусь, спасибо

-

используется или нет? думаю да, а как это посмотреть?

-

Все ноги в этом банке (как пока и во всем проекте) стандарта LVCMOS18