Inanity

Свой-

Постов

269 -

Зарегистрирован

-

Посещение

Весь контент Inanity

-

-

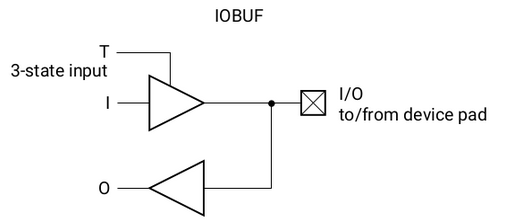

По идее метод должен работать. По идее ещё можно вставить tristate buffer и отключить его навсегда. Тогда клок не будет покидать пределов ПЛИС, что может быть удобно, если не хочется светить этим клоком наружу или если по какой-то причине неиспользованный Clock-Capable пин прижат к земле или питанию банка.

-

Импортозамещение

Inanity ответил vitaly_n тема в Компоненты

Смело. Осталось только понять какой процент вклада российских разработчиков в opensource. Причём, без учёта проектов, которые уже свалили, т.е. без nginx, telegram и иже с ними. -

Импортозамещение

Inanity ответил vitaly_n тема в Компоненты

Люди, вы всерьёз рассчитываете выживать в подобных условиях? -

Up Майнерские платы, типа TUL BTU9P, Bittware CVP-13, SQRL BCU-1525 тоже подойдут.

-

Добрый день. Интересуют платы Xilinx c жирными ПЛИС-ами, от 1 млн LUT6, например такими: Virtex Ultrascale+ XCVU9P, XCVU11P, XCVU13P, VU19P Virtex Ultrascale VU440 Virtex-7 XC7V2000T Не фатально повреждённые платы тоже рассмотрю.

-

Да, как видите, tready не зарегистрирован, хотя всё остальное на AXIS выходит с триггеров. Я очень хотел зарегистрировать все выходы, но красиво сделать это не получалось. С другой стороны, всегда можно поставить AXIS register slice и не усложнять этот модуль, т.к. так или иначе в попытке зарегистрировать всё и вся придётся в этом модуле в том или ином виде сделать всё тот же AXIS register slice.

-

Есть решение по-лучше, чем каждый раз проектировать конвейер на AXI4 Stream с большим риском ошибиться, т.к. все мы - люди. Проектируете конвейер как обычно, без какого-либо хэндшейка вообще, просто input, output и cen. А потом оборачиваете его в обёртку, которая превращает его в AXI4 Stream. Работает обёртка без "пузырей", т.е. без потери пропускной способности шины. Есть четыре правила для конвейера, которые нужно соблюдать, они очень простые: 1. Должна быть возможность остановить конвейер в любой момент без каких-либо поломок и потерь данных. Делается это легко, с помощью clock enable: always @(posedge clk) begin if (cen) begin ... end end 2. Конвейер должен иметь константную задержку (глубину), которая заранее известна. Параметр PIPE_STAGES. 3. Ширина входа и выхода может быть разной, но постоянной. Это параметры PIPE_DATA_IN_WIDTH и PIPE_DATA_OUT_WIDTH. 4. Если нужно пропускать через конвейер без обработки какие-то квалификаторы данных, то используйте tuser, ширина задаётся через PIPE_QUAL_WIDTH. Если все правила соблюдаются, то конвейер легко превращается в AXI4 stream с этой обёрткой: `default_nettype none `timescale 1ps / 1ps module axis_pipeliner # ( parameter integer PIPE_DATA_IN_WIDTH = 32, parameter integer PIPE_DATA_OUT_WIDTH = 32, parameter integer PIPE_QUAL_WIDTH = 4, parameter integer PIPE_STAGES = 8 ) ( input wire axis_aclk, input wire axis_aresetn, input wire [PIPE_DATA_IN_WIDTH - 1:0] s_axis_tdata, input wire [PIPE_QUAL_WIDTH - 1:0] s_axis_tuser, input wire s_axis_tvalid, output wire s_axis_tready, input wire s_axis_tlast, output wire [PIPE_DATA_OUT_WIDTH - 1:0] m_axis_tdata, output wire [PIPE_QUAL_WIDTH - 1:0] m_axis_tuser, output wire m_axis_tvalid, input wire m_axis_tready, output wire m_axis_tlast, output wire pipe_cen, output wire [PIPE_DATA_IN_WIDTH - 1:0] pipe_in_data, input wire [PIPE_DATA_OUT_WIDTH - 1:0] pipe_out_data ); /*-------------------------------------------------------------------------------------------------------------------------------------*/ reg [PIPE_STAGES - 1:0] tvalid_pipe = {PIPE_STAGES{1'b0}}; reg [PIPE_STAGES - 1:0] tlast_pipe = {PIPE_STAGES{1'b0}}; always @(posedge axis_aclk) begin if (~axis_aresetn) begin tvalid_pipe <= {PIPE_STAGES{1'b0}}; tlast_pipe <= {PIPE_STAGES{1'b0}}; end else begin if (pipe_cen) begin tvalid_pipe <= (PIPE_STAGES > 1)? {tvalid_pipe[PIPE_STAGES - 2:0], s_axis_tvalid} : s_axis_tvalid; tlast_pipe <= (PIPE_STAGES > 1)? {tlast_pipe[PIPE_STAGES - 2:0], s_axis_tlast} : s_axis_tlast; end end end assign s_axis_tready = s_axis_tvalid & (~tvalid_pipe[PIPE_STAGES - 1] | m_axis_tready); assign pipe_cen = s_axis_tready | ~tvalid_pipe[PIPE_STAGES - 1] | m_axis_tready; assign pipe_in_data = s_axis_tdata; assign m_axis_tdata = pipe_out_data; assign m_axis_tvalid = tvalid_pipe[PIPE_STAGES - 1]; assign m_axis_tlast = tlast_pipe[PIPE_STAGES - 1]; /*-------------------------------------------------------------------------------------------------------------------------------------*/ genvar i; generate for (i = 0; i < PIPE_QUAL_WIDTH; i = i + 1) begin: loop reg [PIPE_STAGES - 1:0] pipe_gen = {PIPE_STAGES{1'b0}}; always @(posedge axis_aclk) begin if (pipe_cen) begin pipe_gen <= (PIPE_STAGES > 1)? {pipe_gen[PIPE_STAGES - 2:0], s_axis_tuser[i]} : s_axis_tuser[i]; end end assign m_axis_tuser[i] = pipe_gen[PIPE_STAGES - 1]; end endgenerate endmodule /*-------------------------------------------------------------------------------------------------------------------------------------*/ `default_nettype wire

-

Недавно заказывал плату 8-слоёв, 5 класс точности, в процессе оформления заказа подобной опции не заметил, большего и не знаю, если честно. Через via 0.2 проливается, так что это реально актуальная проблема.

- 46 ответов

-

Полностью поддерживаю. Жаль, что Резонит вроде пока так не умеет. Или умеет, но с пересылкой в Китай.

- 46 ответов

-

Burenkov, премного благодарен за ответ! Именно такой подход мне наиболее симпатичен. Спасибо за разъяснение ключевых моментов, вроде общего подхода к работе, номеров форм декларации и т.д. Коллеги выше, конечно, тоже упоминали всё это, но вы объединили это всё в одну картину, за что отдельное спасибо. Скорее всего так и буду пробовать делать.

-

Могу вас огорчить ещё больше, это не соответствует действительности. SRAM-based FPGA не имеют ресурса на число загрузок конфигурации, как, впрочем, не имеет ресурса на чтение/записать любая SRAM память. P.S. зачем вы ворошите старые темы?

-

Там не просто аккаунт нужен, там под NDA, с проверкой анкеты в течение 2 дней, так что не всё так просто.

-

Коллеги, очень много полезной инфы, спасибо, по-немногу начинаю разбираться. Вопрос такой, за рубежом многие предпочтут оплату через PayPal, например, тот же Tindie. Как-то процесс отправки товара коррелирует со способом/фактов оплаты или это два несвязанных процесса вообще? Допустим, на том же Tindie мне приходят заказы, я получаю оплату на PayPal, упаковываю девайс и несу на почту. Оформляю EMS с декларацией того, что это и куда оправляю. Я правильно всё понимаю, или же нет? Как выше совершенно верно заметили, у меня нет абсолютно никакого опыта взаимодействия ни с налоговой, ни с таможней, поэтому буду рад простым и детальным объяснениям. P.S. Когда наконец созрею до отправки девайса обязательно отпишусь здесь как всё делаю и что в итоге вышло.

-

Спасибо, jartsev! Да, цена пересылки немаленькая, но на фоне себестоимости пересылаемого товара может быть вполне приемлемой. Спасибо, baumanets, крайне интересно, есть много вопросов. В контексте данной темы планируется поштучно пересылать небольшие девайсы или отладочные платы физическим лицам по миру (в основном Америка и Европа). Вес одной посылки едва будет больше 1кг, включая упаковку. По поводу оформления юр.лица, кажется, всё понятно. Пожалуй, это самый интересный момент. Допустим я планирую отправлять через EMS. Что же такое нужно написать в этой самой декларации, чтобы посылка без проблем нормально уехала, если речь идёт об электронике (без аккумуляторов, если что). Это мы с вами понимаем, что такое "отладочная плата" и т.д. А что в декларации написать, чтобы таможня это правильно поняла?

-

Да, спасибо, я, конечно, читал про этот проект. Ребята молодцы. Но там все юридические проблемы решены тем, что они нашли резидента в США, т.е. это в каком-то смысле партнерство, о котором коллеги выше писали. Да, и про них тоже слышал. Это, пожалуй, вариант, который мне больше всего нравится. Но опять же, как с ними работать из России? Как-то же собранный мною девай должен покинуть границы этой страны без проблем?

-

Это очень интересный вопрос. Как-то же это китайцы делают...почему же мы не можем? Где-то пишут, что можно регистрироваться на али как продавец из России, но рынок Россией же и будет ограничен, в другом месте пишут, что эти ограничения сняли. Надо изучать вопрос. Спасибо, учту эти моменты. Скажу честно, это для меня совсем тёмный лес, но отступать как-то не хочется. Я, конечно, планирую регулярные поставки, может 100шт в год, а может и меньше, кто же знает как дело пойдёт? Если это не такая проблема с вашей точки зрения, то не могли бы вы хотя бы в общих чертах описать каким образом это сделать?

-

Доброго дня всем! Интересует вопрос реализации собственных электронных разработок в мире. Речь идёт о мелкосерийном производстве. У меня есть один проект, который я развиваю на некоторых иностранных форумах. Понемногу мне начинают писать желающие приобрести экземпляр, бета-версию. Суть проекта роли не играет, предлагаю вообще не затрагивать вопрос тематики проектов, т.к. обсуждение может уйти в неверное русло. Разумеется предполагается, что устройство не делает ничего плохого или незаконного, не связано с криптографией, нет радиопередатчика, негласного сбора информации и т.д. и т.п. Для простоты будем считать, что это некая отладочная плата с микроконтроллером или ПЛИС. Техническая сторона вопроса так или иначе имеет решение, т.е. можно разработать, заказать компоненты, собрать, протестировать и упаковать. И вот теперь, главная суть этого топика, как готовый и упакованный товар отправить покупателю, получить оплату и, разумеется, заплатить налоги, т.к. хочется работать легально и открыто. Я знаю о проблемах импорта заграничной электроники, а как обстоят дела с экспортом? Может быть кто-то нибудь может поделиться опытом? Я думаю, что это будет полезно всем.

-

Точный механизм не знаю, но могу предположить. Кроме напряжения, у вас по умолчанию ещё указывается current strength в миллиамперах (2, 4, 8, 12, 16 ma). Если напряжение питания буфера повышается, то повышается и его current strength. А это значит, что чтобы ток выхода буфера был тем же самым, надо немного прикрыть транзистор, чтобы с новым значением питания он выдавал тот же ток, который требуется. Вот компилятор, видимо, и меняет эту тонкую настройку буфера в дебрях битстрима, чтобы с новым напряжением LVCMOS33, вместо предыдущих LVCMOS25, токовая способность буфера была на том же значении в 4ma, к примеру.

-

Нет, ну это то как раз понятно. Slew rate и drive strength это ок, принимаем, а напряжение то зачем ей знать? Оу...пока писал это предложение, кажется, понял. Напряжение то влияет на параметры тех же slew rate или drive strength. Вот компилятор и подкручивает эти параметры в соответствии с напряжением банка, например. Да, и получается, что если сменить напряжение без ведома ПЛИС, то характеристики буфера поплывут. Спасибо за наводку)

-

Возьмём какую-нибудь микросхему CMOS логики, например, тот же буферный элемент. У неё будет некоторый диапазон рабочего напряжения. Все пороговые уровни лог.единицы, нуля на вход и выход имеют некоторую естественную зависимость от напряжения питания микросхемы. Я, конечно, не тополог/микроэлектронщик, но насколько мне известно такая простая вещь не нуждается в какой-либо обратной связи от напряжения питания. Иными словами, буфер не знает каким напряжением он запитан, но характеристики его работы от входного напряжения известны. Если попытать спроектировать это видение на ПЛИС, то непонятно, зачем конфигурации знать каким напряжением питается тот же LVCMOS буфер. Я прекрасно понимаю, что есть разница, когда мы задействуем другой тип буфера или стандарт, LVDS/SSTL/HSTL и тд...но что там может дополнительно конфигурироваться при изменении питания LVCMOS - мне не очень понятно. Да и потом есть ситуации, когда напряжение банка хочется изменять на ходу. Например тот же SDIO, там инициализация на 3.3, а потом подаётся карточке специальная команда и питание можно понижать до 1.8 и повышать частоту интерфейса. Как это грамотно сделать на ПЛИС, если конфигурация фактически не предполагает возможность изменения питания банка на горячую? Внешний буфер - не в счёт.

-

Понятно, жаль. Кстати, проделал почти тоже самое на xilinx spartan-7, только проект ещё проще, просто один порт выходит из модуля и выводит единицу. Скомпилировал с конфигом LVCMOS18, потом LVCMOS25. Сравнил, в итоге где-то в дебрях битстрима появилась разница, естественно разница была и в контрольной сумме в конце. Ещё была разница в заголовке, т.к. там в тексте сохраняется время компиляции, но это не в счёт. Для чистоты эксперимента вернул опять LVCMOS18, в итоге по сравнению с первой компиляцией разница только в заголовке в начале, время компиляции отличается, что логично. Другой разницы нет и контрольная сумма в конце та же самая. Печаль, видимо всё таки эти настройки что-то изменяют в IO-портах.

-

А RBF он генерирует? Давайте лучше его сравним. Это точно чистый битстрим без лишней шелухи, чего не могу сказать про POF. И да, вы уверены, что если два раза подряд скомпилировать одно и то же, то разницы нет? P.S. альтерщики, извините, но как же надоело разнообразие форматов по сути одного и того же: sof, pof, jic, rbf, rpd...