BSACPLD

Свой-

Постов

912 -

Зарегистрирован

-

Посещение

-

Победитель дней

5

Весь контент BSACPLD

-

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

P.P.S. Под не работающей прошивкой я понимаю запустившуюся прошивку у которой не работает какой-либо модуль. На одной память начинала глючить - каждый 4 байт нули в старших битах, на другой на IDELAY не выставлялась нужная задержка. В общем совершенно разные рандомные глюки. -

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

На проблемных чипах глючат совершенно разные части проекта. Один раз даже было, что ILA не видел клок с пина, стоило немного по другому разложить проект и ILA стал видеть клок. Причем частота там была совсем небольшая - 40 МГц. Вот не верю я, что на 40 МГц ILA не работает. Да. Их в первую очередь проверил. Проблема решалась именно заменой ПЛИС на чип из другой партии. -

Китайские ПЛИС

BSACPLD ответил МАСТЕР LO тема в Работаем с ПЛИС, области применения, выбор

Коллеги, кто уже использовал JFMK50T4 в серии, у Вас чипы с QR кодами или без? Были ли проблемы с глюками чипов? Для текущего проекта мы купили две партии чипов. Одна под номером N5B06C0F без QR кода. Вторая под номером N6B09C0F с уникальным QR кодом на каждом чипе. В итоге все чипы из партии N5B06C0F работают нормально, а из партии N6B09C0F около 30% глючат. Все тайминги в проекте выполняются, констрейны прописаны, асинхронщины нет. Глюки проявляются в виде частичной неработоспособности проекта в зависимости от раскладки проекта по кристаллу. Также на некоторых чипах был вообще странный эффект: - загружаю прошивку при комнатной температуре, охлаждаю плату, проект работает. - перезагружаю прошивку по JTAG при минусовой температуре, проект не работает. - нагреваю плату до комнатной температуры, проект не работает. - даю глобальный сброс на всю логику в проекте, проект не работает. - перезагружаю прошивку по JTAG, проект начинает работать. Пробовали перепаивать чипы с реболлингом - не помогает. Помогает только замена на чипы из партии N5B06C0F. Такое ощущение, что во второй партии на попалась отбраковка с частично не рабочими ячейками / памятью... Было ли у кого-нибудь что-то подобное? -

Сравнил, есть небольшие различия, но только в части ручной установки - драйвера для NVIDIA, yarn, mdadm плюс автоматически установленные пакеты, которые они за собой подтянули. Для начала сравню по вашему списку библиотек, потом попробую нового пользователя создать. Если не поможет, придется в обратную сторону клонировать систему с рабочей машины - только вот через dd уже не получится, на рабочей машине диск большего размера.

-

Обновления 21.1 и 21.2 не ставил - стоит исходная версия Linux Mint 21. NAME="Linux Mint" VERSION="21 (Vanessa)" ID=linuxmint ID_LIKE="ubuntu debian" PRETTY_NAME="Linux Mint 21" VERSION_ID="21" HOME_URL="https://www.linuxmint.com/" SUPPORT_URL="https://forums.linuxmint.com/" BUG_REPORT_URL="http://linuxmint-troubleshooting-guide.readthedocs.io/en/latest/" PRIVACY_POLICY_URL="https://www.linuxmint.com/" VERSION_CODENAME=vanessa UBUNTU_CODENAME=jammy В обоих случаях версия 11.0.21. openjdk version "11.0.21" 2023-10-17 OpenJDK Runtime Environment (build 11.0.21+9-post-Ubuntu-0ubuntu122.04) OpenJDK 64-Bit Server VM (build 11.0.21+9-post-Ubuntu-0ubuntu122.04, mixed mode, sharing)

-

Так я же и написал про версию ОС В логах написано про версию 10.0. На обоих компах по идее должно быть всё одинаково, т.к. я клонировал систему через dd. На клонированной системе ставится без проблем, на исходной вылезает ошибка. После клонирования, кроме видеодрайвера для NVIDIA и yarn, никаких дополнительных пакетов я не устанавливал. На момент установки QuestaSim, на обоих компах были установлены самые последние версии обновлений системы. UPD. Вот с версией java все не так однозначно... В логах консоли пишет про версию 10.0, а если отдельно вызвать java -version, то будет 11.0.21. Похоже, что установщик QuestaSim использует свою собственную версию java вместо системной.

-

Ошибка установки QuestaSim 2021.1 на Linux

BSACPLD опубликовал тема в Среды разработки - обсуждаем САПРы

Коллеги, сталкивался ли кто-нибудь с такой ошибкой при установке QuestaSim 2021.1? ~/Distributive/QuestaSim_2021.1$ Using Java version 10.0 Exception in thread "main" java.lang.ClassFormatError: Unkn <Unknown> at java.base/jdk.internal.misc.Unsafe.defineAnonymousClass0(Native Method) at java.base/jdk.internal.misc.Unsafe.defineAnonymousClass(Unsafe.java:1223) at java.base/java.lang.invoke.InvokerBytecodeGenerator.loadAndInitializeInvokerClass(InvokerBytecodeGenerator.java:291) at java.base/java.lang.invoke.InvokerBytecodeGenerator.loadMethod(InvokerBytecodeGenerator.java:283) at java.base/java.lang.invoke.InvokerBytecodeGenerator.generateCustomizedCode(InvokerBytecodeGenerator.java:680) at java.base/java.lang.invoke.LambdaForm.compileToBytecode(LambdaForm.java:870) at java.base/java.lang.invoke.LambdaForm.prepare(LambdaForm.java:828) at java.base/java.lang.invoke.MethodHandle.<init>(MethodHandle.java:465) at java.base/java.lang.invoke.BoundMethodHandle.<init>(BoundMethodHandle.java:54) at java.base/java.lang.invoke.BoundMethodHandle$Species_LIILL.<init>(java/lang/invoke/BoundMethodHandle$Species_LIILL) at java.base/java.lang.invoke.BoundMethodHandle$Species_LIILL.make(java/lang/invoke/BoundMethodHandle$Species_LIILL) at java.base/java.lang.invoke.BoundMethodHandle$Species_LIIL.copyWithExtendL(java/lang/invoke/BoundMethodHandle$Species_LIIL) at java.base/java.lang.invoke.MethodHandles.filterArgument(MethodHandles.java:3858) at java.base/java.lang.invoke.MethodHandles.filterArguments(MethodHandles.java:3844) at java.base/java.lang.invoke.StringConcatFactory$MethodHandleInlineCopyStrategy.generate(StringConcatFactory.java:1619) at java.base/java.lang.invoke.StringConcatFactory.generate(StringConcatFactory.java:750) at java.base/java.lang.invoke.StringConcatFactory.doStringConcat(StringConcatFactory.java:659) at java.base/java.lang.invoke.StringConcatFactory.makeConcatWithConstants(StringConcatFactory.java:575) at java.base/java.lang.invoke.CallSite.makeSite(CallSite.java:322) at java.base/java.lang.invoke.MethodHandleNatives.linkCallSiteImpl(MethodHandleNatives.java:250) at java.base/java.lang.invoke.MethodHandleNatives.linkCallSite(MethodHandleNatives.java:240) at java.desktop/java.awt.RenderingHints$Key.getIdentity(RenderingHints.java:110) at java.desktop/java.awt.RenderingHints$Key.recordIdentity(RenderingHints.java:114) at java.desktop/java.awt.RenderingHints$Key.<init>(RenderingHints.java:158) at java.desktop/sun.awt.SunHints$Key.<init>(SunHints.java:58) at java.desktop/sun.awt.SunHints.<clinit>(SunHints.java:274) at java.desktop/java.awt.RenderingHints.<clinit>(RenderingHints.java:219) at java.desktop/java.awt.font.FontRenderContext.<init>(FontRenderContext.java:112) at java.desktop/sun.swing.SwingUtilities2.<clinit>(SwingUtilities2.java:107) at java.desktop/javax.swing.UIManager.getLAFState(UIManager.java:246) at java.desktop/javax.swing.UIManager.maybeInitialize(UIManager.java:1480) at java.desktop/javax.swing.UIManager.getDefaults(UIManager.java:708) at com.mentor.install.controlpanel.Install.main(Install.java:1495) Ставил Linux Mint 21 на комп, потом клонировал её на другой комп. Потом обе системы жили своими жизнями некоторое время. На первом компе не ставится, на втором всё поставилось без проблем. Понятно, что не хватает каких-то библиотек, только вот как понять чего именно не хватает? -

Цена 11000 руб.

-

Продам дымоуловитель АТР-7011 (Москва, самовывоз). Б/У В комплекте дополнительные фильтры 4 шт. Цена 1500 руб. Почта для связи bsa-one(собака)yandex.ru, либо в личку.

-

Продам компьютер AMD A8 9600 RADEON R7, 8 ГБ DDR4-2400, 500 ГБ HDD 7200rpm, MSI A320M-A PRO (Москва, самовывоз). Штатный кулер от процессора был заменён на более тихий. Компьютер использовался в качестве стенда для тестирования PCIe плат, каких-то особых наворотов в нём нет - самый обычный компьютер. Установлена Linux Mint 21 с ядром 5.15.0-79. Цена 12000 руб. Причина продажи: проект где был нужен стенд завершён, стоит без дела уже полгода. Почта для связи bsa-one(собака)yandex.ru, либо в личку.

-

В 2022-SP4.2 получилось - больше не выбрасывает. В 2022-SP6.1 проект не собирается - валится на этапе Device Map.

-

У меня как раз именно эта директива используется и это никак не решает проблему с пропаданием сигналов отладчика в итоговом битстриме.

-

Аналогично. Похоже, что на этапе сборки проекта выбрасывается часть сигналов. А ещё у меня были проблемы с ложным срабатыванием триггера, либо наоборот отсутствием срабатывания на часть сигналов - в зависимости от настроек глубины буфера в Inserter. В последней версии 2022.2-SP6.1 проект вообще перестаёт собираться после добавления .fic файла. Такое ощущение, что Pango ни разу не тестировали свой софт на хоть сколько-нибудь сложном проекте...

-

Коллеги, у вас не было такого бага, что все тайминги выполняются, но встроенный лог. анализатор не срабатывает на некоторые сигналы? Либо наоборот ложные срабатывания. Либо после загрузки прошивки пишет, что набор сигналов в ПЛИС и в проекте различается. Директива syn_keep = 1 на нужных сигналах стоит, но, похоже, что Synplify все равно оптимизирует данные сигналы. Иногда не до конца, иногда полностью их выкидывает...

-

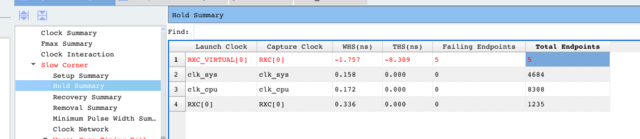

С hold разобрался - у меня была неправильно выставлена задержка на входной ЛЗ. Увеличил с 78 до 100 и ругань на hold исчезла. Видимо я неправильно учёл задержку в клоковом буфере...

-

Так у меня же set_input_delay, что я написал, не противоречит документации...

-

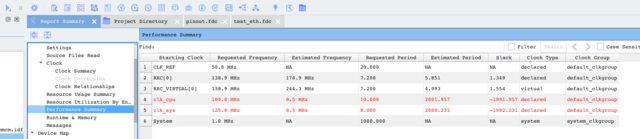

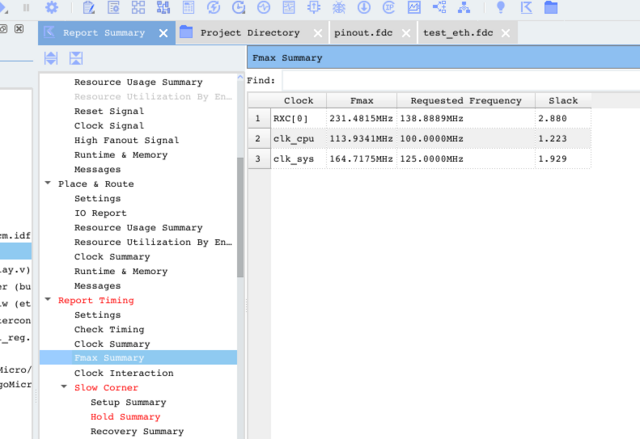

Тогда ещё вопрос. Как правильно констрейнить IDDR? Скопировал рабочие констрейны с Xilinx/Fudan: create_clock -period 7.200 -name {RXC_VIRTUAL[0]} create_clock -period 7.200 -name {RXC[0]} [get_ports {eth_rxc[0]}] # RGMII set_false_path -rise_from [get_clocks {RXC_VIRTUAL[0]}] -rise_to [get_clocks {RXC[0]}] set_false_path -fall_from [get_clocks {RXC_VIRTUAL[0]}] -fall_to [get_clocks {RXC[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -max 0.500 [get_ports {eth_rx_ctl[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -min -0.500 [get_ports {eth_rx_ctl[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -max -add_delay 0.500 [get_ports {eth_rx_ctl[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -min -add_delay -0.500 [get_ports {eth_rx_ctl[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -max 0.500 [get_ports {eth_rd[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -min -0.500 [get_ports {eth_rd[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -max -add_delay 0.500 [get_ports {eth_rd[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -min -add_delay -0.500 [get_ports {eth_rd[0]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -max 0.500 [get_ports {eth_rd[1]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -min -0.500 [get_ports {eth_rd[1]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -max -add_delay 0.500 [get_ports {eth_rd[1]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -min -add_delay -0.500 [get_ports {eth_rd[1]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -max 0.500 [get_ports {eth_rd[2]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -min -0.500 [get_ports {eth_rd[2]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -max -add_delay 0.500 [get_ports {eth_rd[2]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -min -add_delay -0.500 [get_ports {eth_rd[2]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -max 0.500 [get_ports {eth_rd[3]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -min -0.500 [get_ports {eth_rd[3]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -max -add_delay 0.500 [get_ports {eth_rd[3]}] set_input_delay -clock [get_clocks {RXC_VIRTUAL[0]}] -clock_fall -min -add_delay -0.500 [get_ports {eth_rd[3]}] И какое бы значение входной задержки я не ставил, всё время получаю ругань на hold: Также смущает очень кривая оценка частот во время синтеза: При этом финальные частоты получаются нормальные:

-

Для меня это тоже актуально. Сейчас перешёл к написанию констрейнов. Возник вопрос как прописать false_path между клоками с выхода PLL. В Vivado я просто брал названия клоков из отчёта о времянках и писал их в set_false_path. Здесь такое не прокатывает - PDS не может найти клоки по названию которое сам же написал в отчёте по таймингам. Неужели вручную придётся прописывать клоки для каждого выхода PLL через create_generated_clock?

-

А формат обычный Intel HEX или Verilog HEX?

-

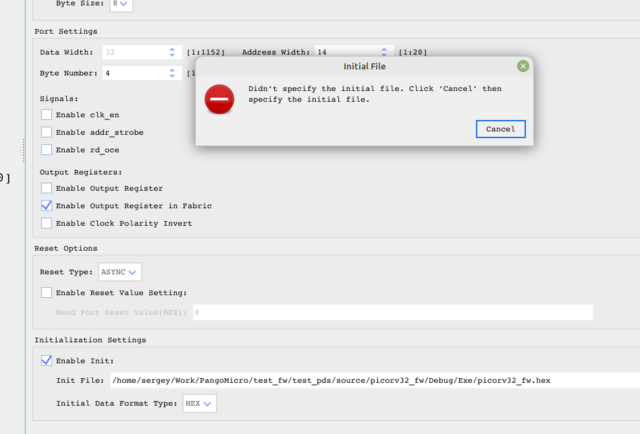

Коллеги, кто-нибудь сталкивался с такой ошибкой? Пробовал и в Linux и в Windows версии - везде одна и та же ошибка при попытке указать файл для инициализации памяти.

-

Тогда остаётся только где-то найти на них описание или User Guide актуальной версии... В UG040006_Logos2 Series FPGA Input Output Interface (IO) User Guide V1.1.pdf я не нашёл описания GTP_IDDR_E1 и GTP_ODDR_E1. По набору сигналов они конечно похожи на IDDR / ODDR от Xilinx, но есть небольшие различия.

-

Хм... Меня смутило, что в названии GTP... Обычно такие названия для трансиверов...

-

С PDS в первом приближении разобрался... При портировании демо проекта с Xilinx/Fudan возник вопрос где посмотреть templates для примитивов и макросов. В самом PDS соответствующие разделы пустые. В частности интересует на что заменять следующие примитивы и макросы: IBUF IDELAYCTRL IDELAYE2 BUFG BUFR STARTUPE2 xpm_memory_spram IDDR ODDR

-

Спасибо. Нашёл. А кроме PCIe и SERDES нет больше IP? CSI-2, например?... И какую версию PDS лучше брать, PDS_2022.2_sp4.2_ads или PDS_2022.2_sp4.2_synplify? PDS_2022.2_sp4.2_ads у меня вроде как нормально завёлся, стоит ли смотреть PDS_2022.2_sp4.2_synplify?

-

Коллеги, мне тут отладка от Alinx наконец приехала. Начал изучать. Поставил PDS, запустил, и не обнаружил IP для PCIe. Только элементарные IP блоки типа BRAM, PLL, и т.д. Подскажите, пожалуйста, как правильно добавлять PCIe в проект. Или может быть где-то можно посмотреть готовый пример под PCIe?