ilkz

-

Постов

132 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные ilkz

-

-

Есть такой вариант:

1) Компилите проект в Eclipse

2) Выполняете Make Targets -> Build -> mem_init_generate -> OK

3) В Quartus добавляете файл software/project_name/mem_init/meminit.qip в проект

4) Компилите проект в Quartus

5) Полученный SOF уже содержит проинициализированную память для Nios II.

6) Конвертируете SOF в нужный формат и заливаете в конфигурационное устройство.

Спасибо, Ваш метод хорош, но он приводит к ненужной пересборке ПЛИС в случае если изменился только код NIOS (а он меняется на порядок чаще).

Вопрос по-прежнему открыт...

-

В проекте, где ниос работает на onchip memory использую вариант doom13. При производстве прошивается только .pof.

В моем случае ниос работает в ddr2-памяти.

-

Получается возможность сделать единый файл прошивки из .sof+.elf, и залить его сразу, отсутствует?

-

Опубликовано · Изменено пользователем des00

Используйте тег codebox для размещения больших сегментов кода (с) Модератор · ПожаловатьсяБуквально недавно шил в память один старый проект, собранный в Q7.1. Для заливки во флеш использовал Q 11.1. Делал следующее:Залил через программер sof

Открыл flash programmer там указал sopcinfo и добавил файлы на заливку: sof + elf

нажал programm flash.

отключил/включил питание. Все заработало

Делаю в точности как Вы описали - не стартует, горит светодиод ERROR.

Выхлоп флэш-программера:

Info: Info: ******************************************************************* Info: Info: Running Quartus II 32-bit Convert_programming_file Info: Info: Command: quartus_cpf --no_banner --convert D:/projects/pack/firmware.sof D:/projects/pack/firmware_ext_flash.rbf Info: Info: Quartus II 32-bit Convert_programming_file was successful. 0 errors, 0 warnings Info: Info: Peak virtual memory: 189 megabytes Info: Info: Processing ended: Fri Feb 20 14:32:58 2015 Info: Info: Elapsed time: 00:00:01 Info: Info: Total CPU time (on all processors): 00:00:01 Info: Using cable "USB-Blaster [uSB-0]", device 1, instance 0x00 Info: Resetting and pausing target processor: OK Info: Reading System ID at address 0x08000040: Info: ID value verified Info: Timestamp value was not verified: value was not specified Info: Info: : Checksumming existing contents Info: Info: Checksums took 1.2s Info: Erase not required Info: Info: 00000000 ( 0%): Programming Info: Info: 00020000 ( 3%): Programming Info: Info: 00040000 ( 7%): Programming Info: Info: 00060000 (11%): Programming Info: Info: 00080000 (14%): Programming Info: Info: 000A0000 (18%): Programming Info: Info: 000C0000 (22%): Programming Info: Info: 000E0000 (25%): Programming Info: Info: 00100000 (29%): Programming Info: Info: 00120000 (33%): Programming Info: Info: 00140000 (36%): Programming Info: Info: 00160000 (40%): Programming Info: Info: 00180000 (44%): Programming Info: Info: 001A0000 (47%): Programming Info: Info: 001C0000 (51%): Programming Info: Info: 001E0000 (55%): Programming Info: Info: 00200000 (58%): Programming Info: Info: 00220000 (62%): Programming Info: Info: 00240000 (66%): Programming Info: Info: 00260000 (69%): Programming Info: Info: 00280000 (73%): Programming Info: Info: 002A0000 (77%): Programming Info: Info: 002C0000 (80%): Programming Info: Info: 002E0000 (84%): Programming Info: Info: 00300000 (88%): Programming Info: Info: 00320000 (91%): Programming Info: Info: 00340000 (95%): Programming Info: Info: 00360000 (99%): Programming Info: Info: Programmed 3488KB in 52.8s (66.0KB/s) Info: Device contents checksummed OK Info: Leaving target processor paused Info: Using cable "USB-Blaster [uSB-0]", device 1, instance 0x00 Info: Resetting and pausing target processor: OK Info: Reading System ID at address 0x08000040: Info: ID value verified Info: Timestamp value was not verified: value was not specified Info: Info: : Checksumming existing contents Info: Info: Checksums took 0.1s Info: Erase not required Info: Info: 02000000 ( 0%): Programming Info: Info: 02020000 (37%): Programming Info: Info: 02040000 (75%): Programming Info: Info: Programmed 338KB in 5.5s (61.4KB/s) Info: Device contents checksummed OK Info: Leaving target processor paused

-

Параллельная, CFI. Режим - 1bit-PS.

Ой, а ключика --epcs я и не заметил...

-

Попробуйте flash programmer в Eclipse. Там вручную конвертировать и объединять sof и elf не нужно.

Так для того, чтобы им воспользоваться, надо все равно сначала .sof залить (иначе он не видит что в чип залито), плюс потом .POF, чтобы сам образ ПЛИС во флэшке оказался. А мне надо уйти от этих, по сути, лишних для производственника действий. Хочу просто один файл (содержащий и ПЛИС и ОС), который заливается через какой-то программатор (пускай пока через quartus_pgm), после чего устройство готово к использованию.

-

Опубликовано · Изменено пользователем ilkz · Пожаловаться

Добрый день!

Имею кит CIII_DEV_KIT. В проекте есть NIOS с флэшкой.

Такая проблема: надо собрать .sof и .elf в один файл и залить, чтобы запускалось.

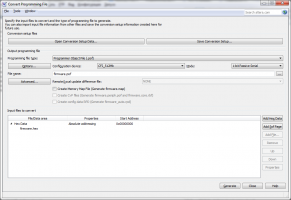

Делаю так:

sof2flash --epcs --input=project.sof --output=hw.flash --verbose elf2flash --input=project_nios.elf --output=sw.flash --boot="$ALTERA/nios2eds/components/altera_nios2/boot_loader_cfi.srec" \ --base=0xc000000 --end=0x10000000 --reset=0xe000000 --verbose nios2-elf-objcopy -I srec -O binary hw.flash hw.bin nios2-elf-objcopy -I srec -O binary sw.flash sw.bin cat hw.bin sw.bin > firmware.bin nios2-elf-objcopy -I binary -O ihex firmware.bin firmware.hex quartus_cpf -c make_pof.cof quartus_pgm pgm_pof.cdf

В make_pof.cof, соответственно, прописано:

В pgm_pof.cdf прописано:

Программатор долго сначала стирает, затем прошивает, но проект в итоге не стартует (горит светодиод ERROR).

Что я делаю не так?

Спасибо!

P.S.: Если делать по отдельности - сначала заливать только .POF с образом ПЛИС, потом .SOF с ней же, потом на нее накатывать .FLASH с ниосом, то все работает прекрасно. Но хочется уйти от такой кучи файлов.

-

Добрый день! Осваиваю TimeQuest, пытаясь починить варнинги.

Если у менять есть регистр, записываемый единожды (перед началом работы остальной части схемы) в домене clkA, значение которого используется в домене clkB (т.е. для домена clkB это как бы статический константный сигнал), то будет ли достаточным условием для корректности времянок задать set_false_path между clkA и clkB? Соответственно, в моем случае таких регистров и клоковых пар - несколько (и set_false_path я задаю так же для всех соответствующих клоковых пар).

-

Почему-то не работает (некорректно работает) сигнал byteenable, который использую для записи байтов в DDR2-память из своего 32-битного MM-мастера. Мастер подключен к памяти через Avalon MM Clock Crossing Bridge. По сигналтапу времянка записи моим мастером вроде ок, но чтение памяти ниосом дает неверный результат: я не только не вижу всех записанных байтов, но они еще и переставлены в каком-то неведомом порядке. Подскажите куда смотреть, а то времянка вроде соответствет даташиту на шину авалон, но результат - нет.

Запись:

Код чтения ниосом:

alt_u32 i = 0; alt_u32 mem_offset = 0; alt_u8 block_size = 100; alt_u8 src[block_size]; for(i = 0, mem_offset = 0; i < block_size; i++, mem_offset+=1){ src[i] = IORD_8DIRECT(DDR2TOP_BASE, mem_offset); } for(i = 0, mem_offset = 0; i < block_size; i++, mem_offset+=1){ printf("%8X: %8X\n", mem_offset, src[i]); }Лог чтения ниосом:

0: 6 1: 0 2: 0 3: 0 4: A5 5: 0 6: 0 7: 0 8: 80 9: 0 A: 0 B: 0 C: A5 D: 0 E: 0 F: 0 10: 0 11: 0 12: 0 13: 0 14: AA 15: 0 16: 0 17: 0 18: 0 19: 0 1A: 0 1B: 0 1C: 0 1D: 0 1E: 0 1F: 0 20: 0 21: 0 22: 0 23: 0 24: 0 25: 0 26: 0 27: 0 28: 0 29: 0 2A: 0 2B: 0 2C: 0 2D: 0 2E: 0 2F: 0 30: 0 31: 0 32: 0 33: 0 34: 0 35: 0 36: 0 37: 0 38: 0 39: 0 3A: 0 3B: 0 3C: 0 3D: 0 3E: 0 3F: 0 40: 0 41: 0 42: 0 43: 0 44: 0 45: 0 46: 0 47: 0 48: 0 49: 0 4A: 0 4B: 0 4C: 0 4D: 0 4E: 0 4F: 0 50: 0 51: 0 52: 0 53: 0 54: 0 55: 0 56: 0 57: 0 58: 0 59: 0 5A: 0 5B: 0 5C: 0 5D: 0 5E: 0 5F: 0 60: 0 61: 0 62: 0 63: 0

Ааа, написал тему и сразу же понял где ошибка: мастер всегда выставляет данные на нулевом байте, а должен - на том байте, который подчеркивается сигналом byteenable. Думаю, что тема закрыта.

-

!!! Hotfix !!!

В модуле обнаружилась веселая ошибка, приводящая к тому, что при использовании нескольких портов Квартус ругался. Ну и еще по мелочи пара исправлений. Выкладываю обновленный код.`include "timescale.v" module data_packer #( parameter nports = 8, parameter port_sizes = {8'd6, 8'd1, 8'd8, 8'd4, 8'd2, 8'd3, 8'd2, 8'd1}, parameter max_port_size = 8 // max port size, bytes ) ( datain, port_ready, reset, clk, mode, // 0 - forced mode (any port_ready[*] signal raise serialization), // 1 - wait mode (packer will be wait for all port_ready[*] signals before serialization, // port_ready[*] signals can come in any order and time) byte, byte_ready, data_packed ); function [max_port_size*nports*8-1 : 0] get_port_map (input integer nports); integer i, tmp; begin tmp = 0; get_port_map = 1'b0; // unsigned extend for (i = 0; i < nports; i = i + 1) begin get_port_map[i*8 +: 8] = tmp; tmp = tmp + port_sizes[i*8 +: 8]; end end endfunction function integer get_ports_list (input integer nports); integer i; begin get_ports_list = 0; for (i = 0; i < nports; i = i + 1) get_ports_list = get_ports_list + port_sizes[i*8 +: 8]; end endfunction localparam port_map = get_port_map(nports); localparam total_bits_len = get_ports_list(nports) * 8; input [total_bits_len - 1 : 0] datain; input [nports - 1 : 0] port_ready; input reset; input clk; input mode; output reg [7:0] byte; output reg byte_ready; output reg data_packed; reg [total_bits_len - 1 : 0] buffer; reg [nports - 1 : 0] ports_stored; reg [$clog2(max_port_size * nports) : 0] byte_cnt, offset; wire all_ports_stored = &ports_stored; wire serialize_en = byte_cnt > 0; wire serialization_done = {byte_ready, serialize_en} == 2'b10; integer n; genvar i, j; generate for(i = 0; i < nports; i = i + 1) begin: port localparam port_pos = port_map[i*8 +: 8] * 8; localparam port_size = port_sizes[i*8 +: 8] * 8; always @(posedge clk, posedge reset) begin if(reset) begin buffer[port_pos +: port_size] <= 0; ports_stored[i] <= 0; end else begin if(port_ready[i]) begin buffer[port_pos +: port_size] <= datain[port_pos +: port_size]; ports_stored[i] <= 1; end if(byte_ready) ports_stored[i] <= 0; if(serialization_done) buffer[port_pos +: port_size] <= 0; end end end endgenerate always @(posedge clk, posedge reset) begin if(reset) begin byte <= 0; byte_ready <= 0; data_packed <= 0; byte_cnt <= 0; offset <= 0; end else begin for(n = 0; n < nports; n = n + 1) begin if(port_ready[n] & !mode) begin byte_cnt <= port_sizes[n*8 +: 8]; offset <= port_map[n*8 +: 8]; end end if(mode & all_ports_stored) begin byte_cnt <= (total_bits_len >> 3); offset <= 0; end if(byte_cnt > 0) byte_cnt <= byte_cnt - 1; byte <= serialize_en ? buffer[((byte_cnt + offset - 1) * 8) +: 8] : byte; byte_ready <= serialize_en; data_packed <= serialization_done; end end endmodule -

Какая проблема ? :)

Ух е-мое как изящно олд-стайл нагнул нью-стайл :twak: . Проверил на моделяторе и на железе - все синтезируется и работает как задумано. Класс.

Век живи, век учись. B)

-

Опубликовано · Изменено пользователем ilkz · Пожаловаться

судя по коду port_map и port_sizes связаны однозначно (позиционно через generate), тогда какой смысл вводить 2 переменных, рискуя ошибиться (port_map постоянно увеличивается, в зависимости от port_size) если это можно рассчитать по месту ?а у вас нет произвольного числа параметров, у вас есть вектор port_sizes, длинна которого определенна в момент передачи параметра и nports который тоже определен при передаче параметра до создания параметра port_list.

Если будут проблемы с синтезом или пониманием синтезатора, то сделайте красивый финт. А именно, old-style Verilog 95 объявление, позволяет использовать в качестве разрядностей векторов localparam.

Т.е. по сути, задавать через параметр нужно только nports и port_sizes. Остальное будут вычисляемые параметры.

Если задать только два параметра (nports и port_sizes), то при итерировании в цикле да - мы сможем достать из вектора нужный размер для нужного порта. Но как посчитать смещение для этого порта, ведь нужно держать где-то сумму всех предыдущих размеров? Основная проблема-то именно в этом.

А так ваше предложение было бы почти идеальным решением. А совсем идеальным оно станет, имхо, если удастся обойтись только одним параметром - port_sizes, а все остальное - будет вычисляемым.

P.S.:

Т.е., в идеале нужно получить что-то такое:

parameter nports = 8, parameter port_sizes = { 8'd6, 8'd1, 8'd8, 8'd4, 8'd2, 8'd3, 8'd2, 8'd1}, ... localparam current_port_pos = 0; generate for(i = 0; i < nports; i = i + 1) begin: port localparam current_port_pos = current_port_pos + port_sizes[i*8 +: 8] * 8; localparam current_port_size = port_sizes[i*8 +: 8] * 8; // и тогда доступ к порту i будет таким: // datain[current_port_pos +: current_port_size] end endgenerate, но верилог так не разрешает, т.к. получается переопределение константного параметра, что недопустимо.

________________________________________________________________________________

_______________________________

ISE 14.7 ест и не давитьсяКвартус очень даже давится:

output [15:0] trx_data_out, input [15:0] data_from_trx ... assign trx_data_out[15:0] = data_from_trx[0:15];

выхлоп:

Error (10198): Verilog HDL error at pcm_test_hw.v(59): part-select direction is opposite from prefix index direction Error (10784): HDL error at pcm_test_hw.v(16): see declaration for object "data_from_trx" Error (12153): Can't elaborate top-level user hierarchy

Но если вручную расписать побитово через assign, то все будет работать.

-

Мощно! Респект!

Но всё же возьму на себя смелость предложить вам посмотреть на интерфейсы. Они проще и в использовании, гибче и позволяют передавать структурированные данные, что очень удобно на прикладном уровне.

Согласен, да вот все никак не хватает времени. Пока приходится крутиться в классическом верилоге.

-

а сумму посчитать функцией нельзя и запихать ее в параметр?

А у функции в верилоге разве может быть произвольное число входных параметров? Вся загвоздка-то верилога именно в том, что нельзя посчитать выражение (например, сумму) на этапе разворачивания кода перед дальнейшим синтезом. А если б можно было бы - так хоть функции, хоть макросы, хоть что угодно использовать можно было бы.

-

Опубликовано · Изменено пользователем ilkz · Пожаловаться

Привет!

Периодически встречаю вопросы в духе "Как на верилоге сделать модуль, у которого будет параметризируемым количество портов и их ширина?". В целом, все ответы сводятся либо к "Делайте много портов и много параметров на каждый порт в отдельности.", либо к "Используйте фиксированную ширину портов", либо к "Верилог не позволяет такое сделать - переходите на СистемВерилог". И вот пришлось и мне с таким вопросом столкнуться, но вникать в СистемВерилог было лень, поэтому решил заморочиться и решить-таки эту задачу. Предлагаю в копилку свое решение.

Итак, задача:

1. Сделать модуль, у которого можно настраивать параметрами количество портов, причем каждый порт может иметь свою ширину.

2. Модуль должен пригоден к повторному использованию без необходимости его редактирования.

Основной принцип:

1. Задаем количество портов, которые будут созданы.

2. Создаем массив размеров портов (на самом деле это не массив, но в контексте задачи можно сказать и так).

3. Создаем массив смещений для каждого порта (т.н. "карта портов").

4. Регистрируем порты в модуле.

5. Пользуемся :)

* Конкретно мой модуль предназначен для сериализации разноразмерных входных портов в поток байтов. Вы можете, при необходимости, сделать свою логику работы. Цель приведенного кода - показать основной принцип подхода к решению задачи.

Код:

`define register_port(n) port_sizes[n * 8 +: 8] module data_packer #( parameter nports = 8, parameter port_sizes = { 8'd6, 8'd1, 8'd8, 8'd4, 8'd2, 8'd3, 8'd2, 8'd1}, parameter port_map = {8'd21, 8'd20, 8'd12, 8'd8, 8'd6, 8'd3, 8'd1, 8'd0}, parameter ports_list = `register_port(0) + `register_port(1) + `register_port(2) + `register_port(3) + `register_port(4) + `register_port(5) + `register_port(6) + `register_port(7) , parameter max_port_size = 128, // max port size, bytes parameter total_bits_len = ports_list * 8 ) ( input [total_bits_len - 1 : 0] datain, input [nports - 1 : 0] port_ready, input reset, input clk, input mode, // 0 - forced mode (any port_ready[*] signal raise serialization), // 1 - wait mode (packer will be wait for all port_ready[*] signals before serialization, // port_ready[*] signals can come in any order and time) output reg [7:0] byte, output reg byte_ready, output reg data_packed ); reg [total_bits_len - 1 : 0] buffer; reg [nports - 1 : 0] ports_stored; reg [$clog2(max_port_size * nports) : 0] byte_cnt; wire all_ports_stored = &ports_stored; wire serialize_en = byte_cnt > 0; wire serialization_done = {byte_ready, serialize_en} == 2'b10; integer n; genvar i, j; generate for(i = 0; i < nports; i = i + 1) begin: port localparam port_pos = port_map[i*8 +: 8] * 8; localparam port_size = port_sizes[i*8 +: 8] * 8; always @(posedge clk, posedge reset) begin if(reset) begin buffer[port_pos +: port_size] <= 0; ports_stored[i] <= 0; end else begin if(port_ready[i]) begin if(mode) buffer[port_pos +: port_size] <= datain[port_pos +: port_size]; else buffer <= datain[port_pos +: port_size]; ports_stored[i] <= 1; end if(byte_ready) ports_stored[i] <= 0; if(serialization_done) buffer[port_pos +: port_size] <= 0; end end end endgenerate always @(posedge clk, posedge reset) begin if(reset) begin byte <= 0; byte_ready <= 0; data_packed <= 0; byte_cnt <= 0; end else begin for(n = 0; n < nports; n = n + 1) begin if(port_ready[n] & !mode) byte_cnt <= port_sizes[n*8 +: 8]; end if(mode & all_ports_stored) byte_cnt <= (total_bits_len >> 3); if(byte_cnt > 0) byte_cnt <= byte_cnt - 1; byte <= serialize_en ? buffer[((byte_cnt - 1) * 8) +: 8] : byte; byte_ready <= serialize_en; data_packed <= serialization_done; end end endmoduleПример его использования:

reg [31:0] port0; reg [7:0] port1; reg [15:0] port2; reg [2:0] rdy_port; `define register_port(n) port_sizes[n * 8 +: 8] localparam nports = 3; localparam port_sizes = {8'd2, 8'd1, 8'd4}; localparam port_map = {8'd5, 8'd4, 8'd0}; localparam port_list = `register_port(0) + `register_port(1) + `register_port(2); data_packer dp ( .reset (reset), .clk (sys_clk), .mode (mode), .datain ({port2, port1, port0}), .port_ready (rdy_port), .byte (), .byte_ready (), .data_packed () ); defparam dp.nports = nports, dp.port_sizes = port_sizes, dp.port_map = port_map, dp.ports_list = port_list;Как это работает:

1. Все порты в итоге классически объединяются в одну толстую шину.

2. Чтобы посчитать общую ширину толстой шины, необходимо просуммировать размеры всех портов. Тут верилог подкладывает свинью, не позволяя переопределить параметр на этапе разворачивания кода, чтобы можно было посчитать сумму.

3. В итоге, как ни крути, сумму придется все равно считать вручную. Но можно это достаточно красиво обернуть в дефайн (см. `register_port(n)).

4. Также верилог не позволяет задавать массивы в параметрах. Но это можно обойти с помощью конкатенации нескольких слов строго заданной ширины, имитируя тем самым массив.

5. Чтобы нужный порт отобразился в нужные биты буфера (в моей задаче), нужно задать смещение для каждого порта. Для этого испоьзуется параметр-псевдомассив port_map, в котором задаются стартовые индексы портов. На вход модуля сигналы должны подключаться в таком же порядке (см. пример использования).

6. Далее, в generate-цикле маппим входы модуля в буфер.

7. А в for-цикле загружаем байтовый счетчик для сериализации соответствующего порта.

В принципе, все. Подход и код в итоге оказался достаточно прост и удобен для использования. Также подход хорош тем, что дает пользователю минимум бюрократии по заданию всяких параметров и настроек.

Если что непонятно, спрашивайте.

Если есть предложения по улучшению - рад выслушать.

Всем спасибо.

-

Опубликовано · Изменено пользователем ilkz · Пожаловаться

Месторасположение не менялось.

Ща вот вспоминаю, был некоторое время назад случай - когда перекидывал какие-то файлы через bluetooth, то квартус после начал ругаться на лицензию (видимо из-за того что на время пересылки файлов в системе появился новый адаптер с новым uid'ом). Отключил адаптер, ребутнул комп - ругаться перестал.

UPD1: еще за это время ставил на комп GTK. Может оно что сбило?

UPD2: все ошибки касаются кастомных компонентов.

-

Опубликовано · Изменено пользователем ilkz · Пожаловаться

Сто лет уже как не запускал Квартус и, в частности, Qsys, а тут руки,наконец, дошли. При попытке открыть в Qsys'е старый рабочий проект, вываливается куча ошибок:

Error: System.: set ALTERA_HW_TCL_KEEP_TEMP_FILES=1 to retain temp files Error: System.: Command: C:/altera/11.1/quartus/bin/quartus_map.exe not_a_project --generate_hdl_interface=D:/projects/fpga/2.5/hw/mcu/ip/alignment_pad_inserter/alignment_pad_inserter.v --source=D:/projects/fpga/2.5/hw/mcu/ip/alignment_pad_inserter/alignment_pad_inserter.v --set=HDL_INTERFACE_OUTPUT_PATH=C:/Users/Pavel/AppData/Local/Temp/alt6295_7625902786790873569.dir/0001_sopcqmap/ Error: System.: Error: System.: Command took 0.140s Error: System.: Analyser output file not present: alignment_pad_inserter.v.xml Error: System.: No definition of alignment_pad_inserter in D:/projects/fpga/2.5/hw/mcu/ip/alignment_pad_inserter/alignment_pad_inserter.v Error: System.: set ALTERA_HW_TCL_KEEP_TEMP_FILES=1 to retain temp files Error: System.: Command: C:/altera/11.1/quartus/bin/quartus_map.exe not_a_project --generate_hdl_interface=D:/projects/fpga/2.5/hw/mcu/ip/ethernet_packet_multiplexer/ethernet_packet_multiplexer.v --source=D:/projects/fpga/2.5/hw/mcu/ip/ethernet_packet_multiplexer/ethernet_packet_multiplexer.v --set=HDL_INTERFACE_OUTPUT_PATH=C:/Users/Pavel/AppData/Local/Temp/alt6295_7625902786790873569.dir/0002_sopcqmap/ Error: System.: Error: System.: Command took 0.140s Error: System.: Analyser output file not present: ethernet_packet_multiplexer.v.xml Error: System.: No definition of ethernet_packet_multiplexer in D:/projects/fpga/2.5/hw/mcu/ip/ethernet_packet_multiplexer/ethernet_packet_multiplexer.v Error: System.: set ALTERA_HW_TCL_KEEP_TEMP_FILES=1 to retain temp files Error: System.: Command: C:/altera/11.1/quartus/bin/quartus_map.exe not_a_project --generate_hdl_interface=D:/projects/fpga/2.5/hw/mcu/ip/udp_payload_inserter/udp_payload_inserter.v --source=D:/projects/fpga/2.5/hw/mcu/ip/udp_payload_inserter/udp_payload_inserter.v --set=HDL_INTERFACE_OUTPUT_PATH=C:/Users/Pavel/AppData/Local/Temp/alt6295_7625902786790873569.dir/0003_sopcqmap/ Error: System.: Error: System.: Command took 0.120s Error: System.: Analyser output file not present: udp_payload_inserter.v.xml Error: System.: No definition of udp_payload_inserter in D:/projects/fpga/2.5/hw/mcu/ip/udp_payload_inserter/udp_payload_inserter.v Error: System.udpgen: TOP_LEVEL_MODULE not specified, file D:/projects/fpga/2.5/hw/mcu/ip/udpgen/udpgen.v contained multiple modules Error: System.: set ALTERA_HW_TCL_KEEP_TEMP_FILES=1 to retain temp files Error: System.: Command: C:/altera/11.1/quartus/bin/quartus_map.exe not_a_project --generate_hdl_interface=D:/projects/fpga/2.5/hw/mcu/ip/ramka_bridge/ramka_bridge.v --source=D:/projects/fpga/2.5/hw/mcu/ip/ramka_bridge/ramka_bridge.v --set=HDL_INTERFACE_OUTPUT_PATH=C:/Users/Pavel/AppData/Local/Temp/alt6295_7625902786790873569.dir/0005_sopcqmap/ Error: System.: Error: System.: Command took 0.130s Error: System.: Analyser output file not present: ramka_bridge.v.xml Error: System.: No definition of ramka_bridge in D:/projects/fpga/2.5/hw/mcu/ip/ramka_bridge/ramka_bridge.v

При этом все связи на месте, ничего не поехало.

При попытке открыть на редактирование какой-либо IP-модуль, возникает ошибка, хотя исходник не трогался:

Error: No modules found when analyzing D:/projects/fpga/2.5/hw/mcu/ip/udpgen/udpgen.v.

При этом если перейти на вкладки настроек модуля, то там в порядке - есть и интерфейсы и сигналы и т.п.

Ничего в проекте не трогалось, Квартус и его компоненты не переставлялись.

С лицухой все ок, да и ядра эти свои.

ОС: Win7x64, Квартус: 11.1sp2.

Что ему не так?

-

Так вроде его вернули в последних версиях, не? Где-то здесь читал, что он на самом деле не выпилен и его можно хитрым образом включить.

-

-

-

Понятно, значит дело в полосе захвата клока pll-кой. Тогда, все логично, так и должно быть )

Но тогда почему такого поведения нет в моделсиме, как писал dima32rus? Кстати, у меня в моделсиме такое поведение тоже не наблюдается (правда, в моделсиме я провожу только функциональное моделирование).

-

На временном пост-фиттерном моделировании (встренным моделятором) в квартусе 9.2SP2 и ниже видел такое странное дело, когда при вставшем в единицу LOCKED частота у PLL еще тактов 10-15 могла немного, совсем чуть-чуть, гулять. Может это были глюки симулятора или отображения сигналов, но глазом при различных масштабах зума времянки это было заметно. Поэтому при сбросе от LOCKED лучше делать небольшой счетчик, который либо отложит сброс схемы ненадолго, либо подольше подержит схему в сбросе.

-

Опубликовано · Изменено пользователем ilkz · Пожаловаться

Добрались руки снова взяться за это дело. Наваял модуль на основе Авалон ММ-мастера (который разделяет доступ читалки/писалки к внешней памяти). Сейчас, когда пытаюсь его встроить в Qsys-систему, возник вопрос: при создании компонента в списке сигналов у мастера отсутствует сигнал beginbursttransfer, хотя в слэйве у DDR2-контроллера он вроде как есть. Что с ним делать? Я его, конечно, дергаю в начале каждого берста, но может он не нужен?

Из этих источников получается что сигнал не актуален, либо его надо через кондуиты выводить-вводить. Но насколько это все правильно?

Источники:

http://www.altera.com/support/kdb/solution...262013_942.html

http://www.alteraforum.com/forum/showthread.php?t=25303

http://cubiccyclonium.net/support/kdb/solu...112006_773.html

UPD:

Avalon Interface Specifications, page 3-5: "beginbursttransfer is optional. A slave can always internally calculate the start of the next write burst transaction by counting data transfers. Altera recommends that you do not use this signal. This signal exists to support legacy memory controllers."

-

Andrew Su, спасибо за документ. Изучаю.

o_khavin, не совсем фифо - скорее именно адресуемую память, т.к. необходимо иметь возможность при необходимости NIOS'ом повторно прочитать некоторые ячейки из памяти (глобально хочу сделать что-то типа UDP с гарантией доставки, поэтому нужно иметь память, из которой при потерях нужно перечитывать и отсылать нужные данные повторно), соответственно, удалять данные из памяти нельзя.

CAM-память на ПЛИС

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Изменено пользователем ilkz · Пожаловаться

Есть внешняя толстая sdram (несколько сотен мегабайт), в которую под завязку записываются пакеты (по несколько килобайт каждый) со всякими полями.

Требуется сделать поиск пакета по значению его поля (значение в процессе работы может меняться, т.е. пакеты живые), т.е. по сути - поиск по памяти (чем быстрее будет поиск, тем лучше).

Ограничения такие:

- все пакеты имеют фиксированную длину

- один пакет встречается в памяти один раз (дубликатов нет)

- за одну операцию поиска надо находить только один пакет (т.е. маска поиска не содержит звездочек)

- интенсивность поиска пускай будет 1 раз в 200 мс

- есть ниос, но его использовать наверное не хотелось бы, т.к. (имхо) он для этого медленен (переубедите если не прав)

- время поиска - чем меньше, тем лучше

- количество плиток на поиск пускай не более 1500 для 3-го Сыклона (обсуждаемо)

Даже не знаю с чего начать и куда копать. Посоветуйте как подобные задачи вообще решаются.