slkhome

-

Постов

93 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные slkhome

-

-

В конечном счете либо реализовать по ТЗ, либо обосновать нецелесообразность реализации. Если это конечно для реальной жизни, а не только для лабораторки

-

On 11/12/2022 at 7:37 AM, Вадим Н. said:

Реально ли отказаться от визуального контроля в режиме "Wave" в пользу консольного вывода наподобие Test::Simple ?

На начальном этапе создания RTL все равно придется посмотреть глазками, а затем уже автоматизировать.

Например UART Tx как RTL, UART Rx как эталон. Затем известные передаваемые вектора, напирмер из файла, принимаются тоже в фейл и файлы сравниваются.

И результат сравнения выводится уже как сообщение в консоль или еще как.

Обычно на качественные тесты с покрытием, времени или людей не бывает.

-

19 hours ago, Egorrok said:

На сколько я понял, в задаче требуется решить на одном ОУ. Нашел такую схему, можно ли на ней реализовать мой случай, когда Uвх находится на нуле или все же нужно сперва расширять диапазон, а потом уже вторым смещать?

Сначала масштабировать, затем смещать.

14 hours ago, haker_fox said:Т.е. VCC на 5 В, а AVSS на -0.5, например.

Возможно чем-то это и лучше, так по мне мучасться с отрицательным доплнительным ИП - больше мороки чем выигрыш.

-

Just now, Egorrok said:

Вы имеете в виду входной сигнал равный 50 мВ преобразовать в 4,998 В ?

Посмотрите описания на ОУ AD8129, AD8137, и подобных. Там в описании много интересных схем применения. Наверняка там найдете все что нужно!

В итогде Вам нужно выбрать такое смещение ОУ, чтобы на выходе получился необходимый диапазон.

И удобнее масштабировать одним ОУ, а смещение другим.

Как реализовывать на обычных ОУ - ОУ со смещением можно найти на просторах инета, даже в Ютубе с картинами и пояснениями.

-

Сначала смасштабировать ОУ, грубо говоря 50 мВ в (5 - 0,002) В, преобразовать смещение 0 В в 0.002 через те же ОУ. Это конечно в Идеале.

В реальности тоже самое, но с запасом. Замем уже в Цифре скорректировать! Так сказать калибровка.

-

Опубликовано · Изменено пользователем slkhome · Пожаловаться

Параметры зазоров магнитопровода известны?

-

А чего не взять готовые модульные ИП и прикрутить к ним МК и прочий функционал, который вам нужен? По крайней мене с маломощными

-

9 hours ago, Shura.G said:

TQFP-144

Веротяно чего-то приличного с подобным корпусом тоже не найти

-

5 hours ago, jenya7 said:

when ST_IDLE => if (OUT_TRIG = '1') then OutState_2 <= ST_SET; end if;

Для начала рекомендую писать полные if then else end if, описываю все исходы.

И приведите тот код, который как раз вызывает ошибку.

В каком компиляторе это делаете?

-

2 hours ago, des00 said:

Пазл сошелся, а я уж было подумал что туплю)

Спасибо )

-

38 minutes ago, des00 said:

Если вам не сложно, буду признателен.

Если не сложно, то напишите что выясните по этим исходникам, плиз

-

4 hours ago, des00 said:

а как вы реализовывали когерентность записи от каждого из портов и разруливали приоритет read-first, write-first?

Честно говоря - уже не помню тонкостей. Это использовал для реализации вейвлет-преобразования. Нужно было быстро реализовать - поэтому было уже не до оптимизации. Место в кристалле было. Алгоритм работал.

Если есть желание поразбираться - могу поискать исходники

-

11 hours ago, alexPec said:

В идеале здесь бы пригодилась восьмипортовая память, но таковой нет, есть только двухпортовая. И на ultrascale+, где все реализовывается, она минимум 18кбит.

Был опыт реализации 4х портовой памяти, на 2х портовых ячейках блочной памяти.

По идее по такому же принципу ее можно еще раз масштабировать и сделать из 4х - 8ми портовую.

Только при этом возрастет количество задействованной памяти в 4 раза.

-

-

On 8/12/2022 at 5:16 PM, Nikita Demerza said:

Здравствуйте. У меня возникла идея написать специальную ос под fpga+arm soc-ы. Само ядро ос должно запускаться на ps(CPU), а все программы на fpga(перестраивается при запуске каждого приложения, возможно деление fpga на несколько областей для запуска нескольких приложений), так вот самый главный вопрос, от которого зависит возможность этого проекта: может ли ps часть прошить pl(fpga) часть?

Какие задачи стоят перед ОС?

Какая ниша предполагается у таких ОС?

Это прототипы для исследований или есть реальная потребность?

Это дипломная работа или диссертация?

ИМХО:

1. На сколько правильно поянл, Intel, а теперь Intel + Altera, подобрым вопросом уже давно озаботились. Тем более когда совместили CPU+PL+SDRAMDDR в одном корпусе. Читал когда-то у них уже даже есть какие-то инструменты, что бы писать ПО как раз с учетом того, что часть программ и будет подгружаться в PL и там работать на зверских скоростях. Конечно там увеличенная скорость загрузки в PL.

2. Для Зинков считаю, что лучше уж делать ускорители для решения конкретных задач, типа IP Core. А в ОС делать поддержку этих IPCores, или писать программы так, чтобы использовать ресурсы IPCores. И расчитывать, что реконфигурация будет происходить редко и медленно.

-

On 8/5/2022 at 4:15 PM, Vadim_nsk said:

AXI-Stream имеет ширину данных 32 или 64 разряда. А если мне надо 256 бит и все эти данные поступают от одного источника с одним клоком, как это правильно описать? Т.е. мне защелкивать каждые 32 бита от своего клока, надеясь, что снаружи на эти несколько входов не подали разные клоки? Но если я указываю один клок для всех шин, среда ругается, что нет клока ассоциируемого с шиной. Как это правильно разрулить?

Присоединяюсь к вышеописанным рекомендациям и еще - Пишите гайды для своих корок. Это ну оч. полезно! И верояно только Вы и будете их пользовать, судя по Вашим вопросам.

-

-

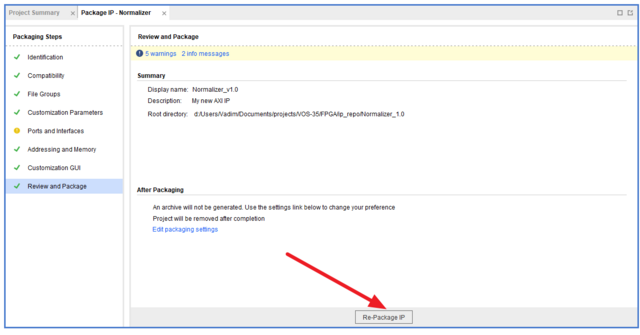

Какая версия Вивады у Вас?

Присылайте для начала хотябы свой этот IP.

Не могу понять чего у вас не получается.

Там для Вашей корки нужно добиться еще хотябы чтобы не было Варнингов.

-

Т.е. я правильно понимаю - у Вас одно ядро внутри другого?

-

У Вас нормально подлкючен репозиторий где лежит Ваш IP core?

-

Там по имеющейся схеме на светодиод выше оговоренный идет сигналс с генератора сброса, который мониторит все напряжения. Так что где-то с напругой беда или с сбросовой микрухой. А там уже дальше копат - не сдохла ли SoC ....

-

И еще в некоторых случаях чтобы избежать неоднозначности положения фронтов комбинационных сигналов, которые могу влиять в итоге на симуляцию идельной модели.

-

... а в дальнейшем они будут прсутствовать в моделях ваших проектах для симуляции пост синтез, пост пост мап, мост рут.

-

Как вы смотрели напряжения? У Вас есть полная схема?

Я на windows 11 установил весь необходимый софт для Spartan-6 : ISE 14.7, Synplify Premier DP P-2019.03-SP1, Questa Sim-64 2021.1

в Среды разработки - обсуждаем САПРы

Опубликовано · Пожаловаться

Как вариант, можно на docker это установить. Потом может и для автоматизации пригодиться.

Недавно пришлось собирать docker image с CenOS6+ISE14.7+Matlab2013.