Skryppy

Свой-

Постов

210 -

Зарегистрирован

-

Посещение

Весь контент Skryppy

-

Понятно. Спасибо.

-

Спасибо, отредактировал сообщение. Использовал директивы inline, unroll, pipeline,dataflow. Так и не смог отвязаться от valid data_in2.

-

Алгоритм этой функции простой - коммутировать данные на выход при наличии команды. просто valid сигналов данных data_in1 и data_in2 может быть разный. Сделал функции my_func1, my_func2. Но результат тот же. Я не пойму как засунуть функции в параллельные процессы #include "ap_int.h" void my_func1(int data_in, int command, int *data_out) { static bool flag; if (command == 1){ flag = true; } if (command != 0 && command != 1){ flag = false; } if (flag == true){ *data_out = data_in; }else{ } } void my_func2(int data_in, int command, int *data_out) { static bool flag; if (command == 1){ flag = false; } if (command != 0 && command != 1){ flag = true; } if (flag == true){ *data_out = data_in; }else{ } } void test( int data_in1, int data_in2, int command, int *data_out1, int *data_out2 ) { #pragma HLS INTERFACE ap_vld port=data_in1 #pragma HLS INTERFACE ap_vld port=data_in2 #pragma HLS INTERFACE ap_vld port=command #pragma HLS INTERFACE ap_vld port=data_out1 #pragma HLS INTERFACE ap_vld port=data_out2 #pragma HLS PIPELINE II=1 my_func1(data_in1, command, data_out1); my_func2(data_in2, command, data_out2); }

-

Спасибо, но все равно не понятно, как сделать порты независимыми. Добавил еще flag, но все равно нет данных: static bool flag1 = true; static bool flag2 = true; if (command == 1){ flag1 = true; } if (command == 1){ flag2 = false; } if (command != 0 && command != 1){ flag1 = false; } if (command != 0 && command != 1){ flag2 = true; } if (flag1 == true){ *data_out1 = data_in1; } if(flag2 == true){ *data_out2 = data_in2; }

-

Vivado hls, проблема с valid сигналов

Skryppy опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Сделал в Vivado HLS проект: #include "ap_int.h" void test( int data_in1, int data_in2, int command, int *data_out1, int *data_out2 ) { #pragma HLS INTERFACE ap_vld port=data_in1 #pragma HLS INTERFACE ap_vld port=data_in2 #pragma HLS INTERFACE ap_vld port=command #pragma HLS INTERFACE ap_vld port=data_out1 #pragma HLS INTERFACE ap_vld port=data_out2 static bool flag; if (command == 1){ flag = true; } if (command != 0 && command != 1){ flag = false; } if (flag == true){ *data_out1 = data_in1; }else{ *data_out2 = data_in2; } } Не могу понять, как сделать порты data_in1 и data_in2 независимыми друг от друга. Когда сигналы valid data_in1 и data_in2 =1, то все работает нормально Но если valid data_in2 = 0, то на выход не подается и data_in1, хотя по идеи они независимые Пытался делать их в разных if-else блоках, итог такой же. Может кто сталкивался с такой проблемой? -

HDL-coder использую совместно со Stateflow -для генерации кода,в Stateflow делаю блоки управления (они тактируются частотами не более 100 МГц). Все высокочастотные блоки беру из Xilinx System Generator.

-

Работаю с матлабовскими HDL-coder, Stateflow, Xilinx System Generator -проекты в железе работают на частотах больше 400 МГц (Virtex7). Громадные проекты(30-80% ресурсов Virtex7), отлаживать одному (особенно, когда раз в неделю получаешь новые указания, на доработки) просто нереально без матлаба. Когда компиляция в железе(Xilinx ISE) уже готового кода занимает более суток, цена каждой ошибки очень высока по времени(и нервам).

-

В книге Лайонса "ЦОС" есть пример, как правильно выбрать частоту дискретизации сигнала, чтобы перенести его на более низкую частоту без децимации (зависит от ширины спектра).

-

Если набор частот фиксированный, то можно в Matlabовском Simulinke накидать модельку - генератор+анализатор спектра, Экспортировать данные, затем в reapeating sequence загружаем разный набор данных -подключаем к анализатору спектра, если уровень шумов нас устраивает, то сохраняем данные.

-

мне кажется,что всплески из-за блока convert

-

А когда мало умножителей в ПЛИСах можно пойти на ухищрения: заменить операцию умножения операцией суммирования и сдвига числа(например число 10 можно представить как 2^3 + 2^1, а степень двойки это сдвиг числа влево). Матлаб, например, может реализовать фильтр на HDL языке с заменой умножителей на такие структуры (алгоритм CSD или Factored-CSD).

-

Задержка сигнала

Skryppy ответил NSergeevich тема в Языки проектирования на ПЛИС (FPGA)

Если преобразовывать частоты с помощью dcm (или mmcm) блоков, то там просто выставляете сдвиг по фазе, какой вам нужен и не паритесь. А в верилоге подключаете стандартные блоки xilinx. -

БПФ

Skryppy ответил dima_spb тема в Алгоритмы ЦОС (DSP)

Советую почитать Р. Лайонса "Цифровая обработка сигналов", там много интересного найдете. -

Также конечные автоматы хорошо тестируются и реализуются матлабом -пакет stateflow. Большие модели реализовать,а самое главное проверить код (все ли состояния автомата учтены, ничего не потеряли ли мы по дороге среди кучи других автоматов) очень тяжело, матлаб позволяет это сделать быстро и просто.

-

fdatool | quantization parameters

Skryppy ответил ilo тема в Алгоритмы ЦОС (DSP)

С арифметикой с фиксированой точкой все на самом деле просто: пусть есть число 0.25 , чтобы его представить в двоичном виде надо зарезервировать 1 бит под знак, 0 бит под целую часть и столько бит, чтобы корректно представить число 25 , т.е. 5 бит. итого имеем: word length=1+0+5=6, fraction length=5. Обычно точности в 16 бит хватает для нормальной работы фильтров. -

Модель АЦП в Simulink

Skryppy ответил Artunique тема в Алгоритмы ЦОС (DSP)

Пример модели АЦП есть в самом матлабе: ищите в хелпе "Designing a Receiver with an ADC" . Также советую погуглить фразу "adc simulink model". -

Реализация полифазного интегратора

Skryppy ответил _sda тема в Алгоритмы ЦОС (DSP)

Я такую же задачу решал при реализации полифазного CIC фильтра. Вот тестовая схемка (без оконечного сумматора и интеграторов): Так как при рекурсии постоянно увеличивается разрядность сигнала после суммирования,то первый сумматор должен иметь настройку точности не Full, а заданную пользователем(например,30 бит). В первой схеме так и сделано,но лучше будет если суммировать с полной точностью,а после сумматора, перед блоком округления поставить регистр,тогда временные характеристики будут намного лучше. P.S.: не тестировал как эта реализация будет работать в схеме цифровой обработки. integrator.rar -

Погуглите файл :Intro to System Generator Part 2 Ссылка: http://webcache.googleusercontent.com/sear...mp;client=opera Там посмотрите про fixed point,сложение чисел и переполнение при сложении (overflow) и т.д.

-

Можете заранее расчитать коэффиценты заграждающих фильтров в FDATools пакета MATLAB,там,кстати можете экспортировать фильтр в C header. "С Coder" матлаба также позволит вам реализовать различные фильтры, причем вы сами настраиваете арифметику-с плавающей или фиксированной точкой. А про перестраиваемые фильтры обсуждение было в соседней теме "Цифровой узкополосный фильтр с динамически изменяемой центральной частотой".

-

Перестраиваемый фильтр можно сделать путем набора различных комбинаций коэффициентов фильтров(заранее посчитанных,например, в Матлаб и экспортированных в удобочитаемую для железа форму,т.е. *.coe файлов), при необходимости загружать нужную характеристику из массива. Для Xilinx есть готовая корка IP FIR Compiller в которой присутствует функция Reloadable coefficients.

-

Перенос частоты

Skryppy ответил Skryppy тема в Алгоритмы ЦОС (DSP)

Спасибо. Я кажется нашел решение: Буду использовать преобразователь Гильберта,получу комплексный сигнал,затем умножу его на экспоненту и получу или суммарные или разностные частоты. -

Перенос частоты

Skryppy ответил Skryppy тема в Алгоритмы ЦОС (DSP)

Так зачем тогда квадратурный преобразователь,я могу просто умножить исходный сигнал на cos(wt). И умножать на -sin не имеет надобности. вроде смысл в квадтарутном переносе как раз в том,чтобы не появлялось лишних частот,или я неправ? -

Перенос частоты

Skryppy ответил Skryppy тема в Алгоритмы ЦОС (DSP)

Только разностный сигнал останется если умножить cos(wt) на соs исходного сигнала,но почему так делать надо -непонятно :( -

Перенос частоты

Skryppy опубликовал тема в Алгоритмы ЦОС (DSP)

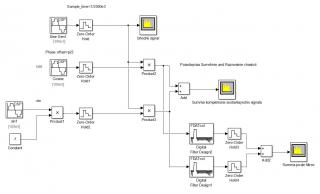

Здравствуйте.Помогите,пожалуйста, разобраться в цифровом переносе частоты. Что я хочу сделать : немного перенести частоту (300кГц) по диапазону,пускай на 100 кГц вниз.Тут мне не нужно интерполировать и децимировать сигнал. Итак,что я делаю: беру исходный сигнал,умножаю его на cos(wt) и -sin(wt),получаю и суммарные частоты и разностные (первый график).Но,по идеи должны быть только или разностные или суммарные частоты. Поставил фильтр и задавил ненужные частоты(второй график),но я так понимаю,что при квадратурном переносе недолжно быть и тех и других частот одновременно,что я делаю неправильно или так и должно быть? Схема: Графики: Модель Simulink: vopros_o_perenose_spectra.rar -

Спасибо всем,все заработало.