GriXa

Свой-

Постов

54 -

Зарегистрирован

-

Посещение

Весь контент GriXa

-

PCI

GriXa ответил go2winner тема в Работаем с ПЛИС, области применения, выбор

PCI или PCI Express? Если PCI Express, то 1) Возьмите схему любого KIT'a и скопируйте часть с PCIE в свой проект. Если устройство напрямую связано с PCIE, то схема соединения весьма проста. 2) Достаточное количество вентилей зависит только от размера Вашего проекта. 3) Зависит от операционной системы. Для своей разработки необходимо писать драйвер. Для тестов, возможно, есть примеры от Xilinx. Под Линукс проще написать примитивный драйвер для чтения/записи, чем под Win. Как вариант, попробовать сконфигурировать PCI Express как стандартное COM или LPT устройство, и пользоваться стандартными драйверами ОС. -

Lattice ECP5

GriXa ответил jorikdima тема в Работаем с ПЛИС, области применения, выбор

Добрый день, напишите, что Вам нужно скачать. -

Контур платы в Footprint компонента

GriXa опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Добрый день. Возник вопрос. Есть разъем (к примеру, Amphenol FCI 10025026-10100TLF) требующий определнного выреза в печатной плате. Существует ли способ создать футпринт для него со слоем контура платы? Пока что для решения этой щадачи, разместил линию контура в слое графики футпринта. И при создании проекта вставил скопированную из Decals линию контура, совместил с футпринтом и дорисовал остальную часть контура. Есть ли способ сделать это как-то логичнее? Или идеологически правильнее иметь контур платы в библиотеке, а в футпринте отрисовывать только посадочные площадки? Ну и по совместительству еще один вопрос: можно ли в PADS Layout выделить линию шелкографии футпринта? Спасибо! -

Lattice ECP5

GriXa ответил jorikdima тема в Работаем с ПЛИС, области применения, выбор

Dimond, на мой взгляд, смотрится значительно проще Квартуса, ISE или Vivado. Меньше примочек и свистелок. Самый большой недостаток, как мне кажется, отсутствие широко поддерживаемого комьюнити. Мало обучающих видео, статей и различных материалов. А в остальном, вполне приятный для разработки софт. Как "бонус" симплифай и ActiveHDL. -

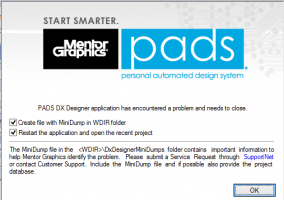

Добрый день! Заменил путь к папке WDIR_PADSVX_2, и сразу все заработало. Премного благодарен Вам за совет.

-

Благодарю за ответ. Но, к сожалению, ошибка возникает даже при создании нового проекта. Откат тоже не помог.

-

Редакторы HDL

GriXa ответил zorromen тема в Среды разработки - обсуждаем САПРы

2 Tpeck: Про Notepad++, к сожалению, ничего сказать не могу. Но вот отличный плагин Veditor для Eclipse парсит VHDL код, и сигнализирует об ошибках синтаксиса. Не всегда плагин работает безупречно. Но на мой взгляд вполне удачное бесплатное решение. 2 Flip-fl0p: Прошу прощения за некропостинг, но чтобы избавиться от удобно использовать records types. Подробнее про его использование написано у Jiri Gaisler в статье A structured VHDL design method в разделе 5.5 Using record types. -

Добрый День! По непонятной причине перестали грузиться проекты в Mentor PADS. После запуска DxDesigner, при открытии Netlist проекта, возникает ошибка: Pads Integrated проекты запускаются на десятый раз, или вылетают с аналогичной ошибкой. Переустановка, к сожалению, не помогла. Кто-нибудь сталкивался с решением подобной проблемы? Заранее благодарю.

-

Создание PCI устройства

GriXa ответил gradient78 тема в Предлагаю работу

Мог бы посоветовать для изучения ПЛИС фирмы Лэттис, у них сейчас промо-акция, можно за хорошую цену купить плату с PCIE. http://www.latticesemi.com/ECP5promo Делал для нее проекты и пробовал писать примитивнейший драйвер для Линукса. -

Добрый день! Кто-нибудь связывался с симуляцией PCIE Endpoint x1 для Lattice 5UM в Active-HDL 10.2? Проблема в странных ошибках при компиляции файла xxx_beh.v, который содержит библиотеку симуляции PCI-Express ядра. Когда симуляция запускается из скрипта, прилагаемого к сгенерированному ядру, ошибок не возникает. Когда создаю отдельный проект для тестирования собственных модулей, возникают ошибки из-за того, что active-hdl не может найти defines, находящиеся в другом файле этого же проекта. Файлы в проект добавляю такие же, как указаны в скрипте. Все остальное компилируется без проблем. Заранее благодарю за помощь.

-

Вроде ее еще можно купить.

-

Появилось свободное время, и удалось решить данную проблему. Похоже, для заливки большого файла в LPDDR платке LX9MicroBoard не хватало тока. Как только вместо 5 вольт через USB-кабель подключил 5 вольт от лабораторного ИП, проблема пропала.

-

На мой взгляд, классический Hello world на ПЛИС - это кусок кода на чём-то вроде VHDL или Verilog, который мигает светодиодом на плате. Microblaze и использование различных IP - это, как мне кажется, следующий шаг в изучении ПЛИС. Что касается Вашего вопроса про FFT, то ознакомтесь с описанием AXI интерфейса. Дело в том, что если в Microblaze используется шина AXI, то это Full-AXI. А у модуля FFT - AXI-Stream. Просто так их друг к другу не подключить. Надо использовать "переходник" MemoryMapped to Stream. Буфер или фифо можно использовать уже в памяти Microblaz'a

-

Спасибо! Но проблема как раз в том, что программа не грузится ни по GDB, ни через XMD.

-

Спасибо за ответ! Память, похоже, работает адекватно. Небольшие файлики пишутся и проверяются без проблем в разных областях памяти. Как только пытаюсь загрузить файл размером от 0.5К, прогресс загрузки умирает. Набраться терпения и подождать - тоже не помогает. 10-15 минут не дают никакого результата.

-

Добрый день! Большой Elf-файл не хочет записываться в LPDDR. XPS 14.7, LX9Microboard Spartan6 Создал проект Microblaze в XPS, подключил LPDDR-память к M_AXI_DC, M_AXI_IC (128Mb) В SDK создал проект, который пытаюсь через XMD-консоль загрузить в память. Небольшая программка грузится и запускается без проблем. При загрузке бОльшей программы, все подвисает. Вот что выдает консоль: XMD% dow project.elf System Reset .... DONE Downloading Program -- project.elf section, .vectors.reset: 0x00000000-0x00000007 section, .vectors.sw_exception: 0x00000008-0x0000000f section, .vectors.interrupt: 0x00000010-0x00000017 section, .vectors.hw_exception: 0x00000020-0x00000027 section, .text: 0xa8000000-0xa800e287 section, .init: 0xa800e288-0xa800e2c3 section, .fini: 0xa800e2c4-0xa800e2e3 section, .ctors: 0xa800e2e4-0xa800e2eb section, .dtors: 0xa800e2ec-0xa800e2f3 section, .rodata: 0xa800e2f4-0xa800e947 section, .data: 0xa800e948-0xa800eed3 section, .sdata: 0xa800eed4-0xa800eed7 section, .bss: 0xa800eed8-0xa800ef33 section, .heap: 0xa800ef34-0xa800f337 section, .stack: 0xa800f338-0xa800f737 Download Progress.. Дальше строка прогресса не шевелится и все подвисает. ILA в проект не лезет, щупом тоже никуда не прислониться. Может кто знает, в чем может быть проблема?

-

Вроде бы разобрался. Ответ нашел на форуме Xilinx здесь В качестве примера взял проект

-

Добрый день! Подскажите пожалуйста, в каком направлении необходимо копать, чтобы в Xilinx SDK настроить Burst передачу данных по AXI4 шине. Если я правильно понимаю, стандартный xil_io может писать только один строб данных. С DMA все понятно, а информацию про расширенное использование AXI не нашел. ZedBoard, Vivado 2014.4 Спасибо.

-

RED Pitaya Open-Source генератор, осциллограф и ещё куча всего на Xilinx Zynq 7010 SoC

-

SPI на VHDL

GriXa ответил Loota тема в Языки проектирования на ПЛИС (FPGA)

Тактовая частота должна приходить на какую-нибудь ножку Вашей epm. На какую именно - можно понять из схемы. 50 нс это 20 МГц. Посмотрите, какой генератор стоит в Вашем устройстве. Если, к примеру, 20 МГц - то один такт уже и будет 50 нс. Если нужно сделать задержку больше одного такта, используйте счётчик. Конструкция выглядит примерно так: if counter < MAX_VALUE then counter <= counter + 1; else counter <= (others => '0'); end if; Исходя из значения частоты, приходящей в кристалл, расчитывается величина MAX_VALUE. Если нужно сделать задержку меньше одного дакта, то без встроенной pll не обойтись. В EPM, насколько я знаю, pll нету. -

2 eugen_pcad_ru: На мой взгляд, в теории не всё так однозначно: резервирование, к примеру, вроде бы является методом повышения характеристик надёжности.

-

Как мне кажется, надёжность увеличится ровно в 1 раз. Что может сделать сам по себе такой же второй блок, и как решить, какой из двух дал сбой? Чтобы это понять, нужно делать третий блок для сравнения, который при получении отличных результатов, говорит, что увидел ошибку. И что с этой ошибкой потом делать. Эта методика используется для создания систем безопасности, где требуется высокая надёжность, и где дублирование системы делается не только в кристалле, но и во всём устройстве (дублирование датчиков, входов и выходов, постоянная проверка питающего напряжения и так далее). Там, где при обнаружении ошибки должно происходить какое-либо действие: что-нибудь отключаться или переходить в безопасный режим. В этом случае, ошибка (обрыв провода, короткое замыкание, выход из строя датчика) ловится не только в железе, но и внутри кристалла. Для сертификации таких устройств прошивка ПЛИС должна отвечать определённым требованиям. В этих требованиях и говорится, что должны быть одинаковые, независимые друг от друга блоки, разделённые в кристалле зонами безопасности. И результат работы этих блоков должен всё время сравниваться. Самое интересное, что и софт, разводящий кристалл, должен быть сертифицирован. То есть не все версии, к примеру ISE, одинаково полезны :) Для всех остальных случаях, ИМХО, подобная избыточность не нужна.

-

Инициализацая регистров делается с помощью констант, выглядит примерно так: architecture xxxx type reg_type is record reg1 : std_logic; reg2 : std_logic; end record; constant reg_t_init: reg_type := ( reg1 => '0', reg2 => '0'); begin combinator process (d,r) xxxx end process combinator process (clk) begin if rising_edge (clk) then if reset = '1' then r <= reg_t_init; else r <= rin; end if; end if; end process; end;

-

A structured VHDL design method

GriXa опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Доброго всем времени суток. Поиск на форуме по этой теме не дал результатов. Недавно натолкнусля на интересный стиль написания VHDL кода. Называется он вроде как two-process method. В кратце об этом методе можно почитать, набрав в поисковике "A structured VHDL design method" (Jiri Gaisler). Основная идея - entity состоит из двух процессов: комбинаторного и последовательного (combinational and sequented logic) и содержит всего один вход и один выход, плюс сигнал тактирования и сброса. В package в виде type record описывается подробно, что входит в состав входного и выходного сигналов. Поведение блока описывается с помощью комбинаторной логики и переменных. Синхронный процесс назначает входные регистры и считывает выходные. Использование variables в теле комбинаторного блока для больших проектов, по идее как сокращает время симуляции. Помимо удобства понимания программы, огромный плюс этого метода заключается в том, что если в процессе написания проекта необходимо добавить какой-либо сигнал или регистор, то он добавляется только в поле описания типа. В качестве примера приведён кусок кода из статьи. Он описывает работу элементарного счётчика. library ieee; use ieee.std_logic_1164.all; package count8_comp is -- component declaration package type count8_in_type is record load : std_logic; count : std_logic; din : std_logic_vector(7 downto 0); end; type count8_out_type is record dout : std_logic_vector(7 downto 0); zero : std_logic; end; component count8 port ( clk : in std_logic; d : in count8_in_type; q : out count8_out_type); end component; end package; library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use work.count8_comp.all; entity count8 is port ( clk : in std_logic; d : in count8_in_type; q : out count8_out_type); end; architecture twoproc of count8 is type reg_type is record load : std_logic; count : std_logic; zero : std_logic; cval : std_logic_vector(7 downto 0); end; signal r, rin : reg_type; begin comb : process(d, r) -- combinational process variable v : reg_type; begin v := r; -- default assignment v.load := d.load; v.count := d.count; -- overriding assignments v.zero := ’0’; if r.count = ’1’ then v.cval := r.val + 1; end if; -- module algorithm if r.load = ’1’ then v.cval := d.data; end if; if v.cval = "00000000" then v.zero := ’1’; end if; rin <= v; -- drive register inputs q.dout <= r.cval; q.zero <= r.zero; -- drive module outputs end process; regs : process(clk) -- sequential process begin if rising_edge(clk) then r <= rin; end if; end process; end; -

Письмо, к сожалению, не появилось в почтовом ящике