cdsinit

Свой-

Постов

72 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о cdsinit

-

Звание

Участник

- День рождения 07.11.1983

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Посетители профиля

1 331 просмотр профиля

-

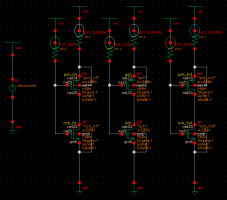

Еще раз про САПР - Cadence IC5141 или IC61x. Инструкция и примеры входят в комлект. Работает он под Linux. Есть и другие САПР аналогичного применения, например Tanner L-Edit, Synopsys Custom Designer. Для проверки DRC/LVS и экстракции паразитов использую Cadence Assura, для аналогового моделирования Cadence Spectre/Ultrasim (пакет MMSIM). Просмотр результатов моделирования в Simvision (Cadence IUS) или Synopsys CustomExplorer.

-

Есть еще заказное проектирование, заключающееся в разработке схемы на уровне отдельных транзисторов и последующем ручным или полуавтоматическим рисованием топологии (Cadence IC5141). Моделирование схемы выполняется на SPICE-подобных симуляторах (Spectre, Ultrasim, HSPICE, Nanosim). Проверка топологии и экстракция паразитных RC делается на Assura (еще есть Calibre, Hercules, StarRC). Разобраться в этих программах можно, почитав прилагаемую к ним документацию и посмотрев примеры. Заказное проектирование приходится применять для блоков, которые затруднительно или невозможно получить путем синтеза из Verilog-модели - блоки памяти, регистровые файлы, ФАПЧ, АЦП и т. п. Процесс заказного проектирования мне кажется несколько интересней программирования на Verilog, однако вакансий на эту специальность я давно не вижу.

-

Медь в глубоких субмикронных процессах используется по причине большей стойкости к эффекту электромиграции ( http://ru.wikipedia.org/wiki/Электромиграция ) Явление электромиграции актуально для всех слоев металлизации. Шины питания (для них наиболее жесткие нормы по EM) могут находиться в любом слое. Тепло в ИС на объемном кремнии отводится в основном через подложку, кремний хороший проводник тепла.

-

Пожарная сигнализация в квартире

cdsinit ответил MAGician тема в В помощь начинающему

Поискал по словам "тепловой извещатель", стало относительно понятно, что это такое. На картинке нормально замкнутый извещатель, в котором две упругие пластины спаяны легкоплавким сплавом. При нагреве сплав плавится и цепь разрывается. Хотел его убрать при ремонте, но теперь не буду -- при обрыве может быть тревога, если эта система еще работает. -

Пожарная сигнализация в квартире

cdsinit ответил MAGician тема в В помощь начинающему

Вопрос в тему. В доме 1980 г. постройки над входной дверью стоит такой датчик. Напряжение на контактах ~ 1 мВ. Какие могут быть предположения относительно того, для чего он нужен? Сразу в 01 сообщает при пожаре? Состояние у него весьма сомнительное. -

Помогите выбрать авторегистратор

cdsinit ответил rembiok тема в АВТО электроника

Очень хочется такой, но как это сделать? -

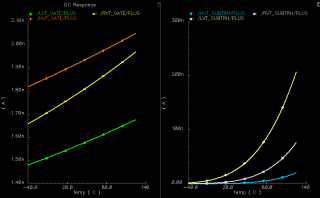

Есть еще варианты SF и FS - небольшие перекосы между P и N транзисторами. Как я понял, по быстродействию они весьма близки к TT. "With the scaling of CMOS technologies, the gap between nominal supply voltage and threshold voltage has decreased significantly. This trend is further amplified in low-power nanometer libraries, which feature cells with identical size and functionality, but different threshold voltages. As a consequence, different cells may have different delay behaviors as the temperature varies within a circuit. For instance, cells with low-threshold devices may experience an increase in delay when temperature increases, whereas cells using high-threshold devices may experience the opposite behavior." Аномалии видимо начинаются по причине того, что напряжение питания настолько низкое, что сравнимо с суммой абсолютных величин порогов P и N транзисторов. С ростом температуры пороги уменьшаются, подвижность тоже. Уменьшение порогов приводит к снижению задержек, а уменьшение подвижности наоборот к их росту. Этим можно объяснить рост задержек у низкопороговых транзисторов с повышением температуры и уменьшение задержек у высокопороговых.

-

При этом, правда, нужно учитывать возможность технологических отклонений. Модели для углов SS, TT, FF у меня дают очень большое различие по утечкам - почти 2 порядка между SS и FF.

-

PLL генератор

cdsinit ответил BlackOps тема в Цифровые схемы, высокоскоростные ЦС

В схеме. Как раз добавлены два триггера, потом элемент ИЛИ и счетчик тактов. Вместо счетчика можно аналоговое реле времени использовать, площадь примерно одинаковая. А это как? Отслеживают тот факт, что напряжение после захвата фазы перестает изменяться? -

PLL генератор

cdsinit ответил BlackOps тема в Цифровые схемы, высокоскоростные ЦС

Такую реализацию я тоже видел. В обоих способах необходимо после обнаружения захвата фазы выдерживать некоторое время, чтобы избежать ложного срабатывания. Это можно делать как счетчиком тактов опорного сигнала, так и конденсатором с источником тока. -

В современных технологиях есть возможность делать на одном кристалле транзисторы с различными пороговыми напряжениями - Low, Regular, High. Как текут закрытые инверторы показано на картинке. С ростом температуры затворные и подпороговые утечки растут, последние очень сильно. Транзисторы с высоким порогом применяют в тех частях схемы, где не требуется быстродействия.

-

PLL генератор

cdsinit ответил BlackOps тема в Цифровые схемы, высокоскоростные ЦС

Когда-то я делал детектор захвата фазы для интегральной схемы и решил задачу как раз таким образом -- XOR на выходы UP и DN фазового детектора. Когда система ФАП захватила фазу, UP и DN принимают форму коротких импульсов, появляющихся примерно в одно и тоже время - соответственно на выходе XOR либо ноль, либо небольшая иголка, которая потом фильтруется схемой из NOR и четного числа инверторов перед ним ("ФНЧ"). Для исключения ошибок используется что-то вроде реле времени с конденсатором. Выход XOR, отфильтрованный "ФНЧ", управляет ключем, разряжающим конденсатор (сброс реле времени), в то же время конденсатор заряжается постоянным током, подобранным так, чтобы процесс длился несколько мкс. Напряжение на конденсаторе -- фактически и есть признак захвата фазы. Признак LOCK появляется лишь через некоторое время после захвата, однако пропадает почти сразу, когда фаза сбилась. -

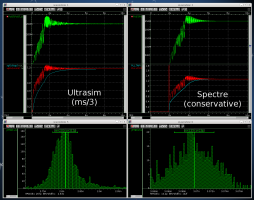

Сделал окружение для тестирования симулятора Ultrasim. Архив с файлами доступен по ссылке http://ifolder.ru/26559696 Желающие могут адаптировать окружение под другие симуляторы. Тестирование симулятора заключается в моделировании PLL с некоторыми настройками точности и наблюдении за джиттером выходного сигнала. Для справки приведены результаты работы программ Ultrasim и Spectre из пакета MMSIM110.

-

Синтез звука.

cdsinit ответил -=Женек=- тема в Математика и Физика

Звук похожий на музыкальный из одной строчки кода: http://countercomplex.blogspot.com/2011/10...ne-line-of.html На AVR пока не пробовал делать, опыт по МК мал. -

К процессу этот вопрос не применим. Можно сказать, на сколько МГц расчитана конкретная память по этому процессу. Написано, что у CLK min_period=1.150 нс (типичные условия TT/1,0/25 - процесс/питание/температура) => 869 МГц максимум В наихудших условиях (SS/0,9/125) память работает медленнее, и min_period=1.874 => 533 МГц максимум Микросхема должна проектироваться так, чтобы быть работоспособной как на быстром (FF), так и на медленном (SS) процессах. Это необходимо для того, чтобы не терять выход годных при неизбежных технологических отклонениях на производстве.