warrior-2001

Свой-

Постов

554 -

Зарегистрирован

-

Посещение

Весь контент warrior-2001

-

Ни одна pll вам не гарантирует синфазность входного и выходного клока. Есть режим "zero что-то там", но там синфазность с выходным клоком на выходном пине. Внутри ПЛИС так не получается.

-

Добрый день! Удалось на практике применить HMC7044?

-

Коллеги пытались использовать ядро для ЦАПов от Техасов (ТИ). Сходу не получилось, а потом им таки купили ядро готовое.

-

Трансиверы - конечно использовал. У меня поток был 4 Gbps. CDR - использовал, но можно и без него, если опора есть на входе ПЛИС правильная.

-

Мы так и в QuestaSim делаем. C++ подтягиваются на "ура".

-

НПП Электромаш появился в Таганроге? Это филиал или удалённое подразделение? И чем вы занимаетесь в области ПЛИС?

-

Это самый простой базовый вариант. Я соединял вендоры и по SFPDP, и по Fibre Channel. Проблем никаких не было. Но начинал с базы.

-

Офис в центре Ростов на улице Большая Садовая. Это 40 минут пешком либо 15-20 минут на любом транспорте от пригородного ЖД вокзала.

-

Ростов на Дону обозначен в топике. В Таганроге я бы сам с радостью открыл удаленное подразделение, но Москва пока не видит разницу между Ростовом и Таганрогом. Посему некоторые катаются на работу каждый день из Таганрога в Ростов. Это порядка 80 км от двери до двери. По Московским меркам - вполне нормально.

-

Ох и тему развели тут по приборам. Парк приборов в лаборатории, да и у меня на столе - далеко за 20 млн. выходит по стоимости. Сквозной маршрут проектирования тоже порядка 50 млн. И это необходимость. Однако знаю людей, которые похожие по трудоёмкости вещи делают на куда более скудном оборудовании и ломаном САПР. Однако мне сделать то же самое куда проще, чем им. В среднем на 10-15% получше стало, плюс выплаты премий стабилизировались. Но в целом до Москвы с Питером не дотягиваем конечно

-

Вопрос спроса и предложения никто не отменял. Я технический специалист и не возражаю, если мне будут платить больше за ту же работу. А руководство не возражает, если я продолжаю усердно работать без поднятия ЗП. Но вот в чём дело - все кандидаты, что приходят на собеседование, отчего-то по уровню не дотягивают до требований. А те, что дотягивают - получают примерно схожие оклады и не собираются ради +/- 20% от оклада менять работу. А стартапы всякие с окладами 200к+ - это хорошо конечно, но рискованно. И только Мск и окрестности. Так что, как писали выше в схожих ветках, при средней ЗП в 20-30к оклады разработчиков вне Мск не могут быть 100к+. Это суровая правда. А соглашаться с ней или нет - дело каждого. Если так рассуждать - надо всем делать сайты и уходить из электроники... Своих сотрудников мы находим, однако не всегда быстро. П.С. А вакансии по прежнему актуальны.

-

Вакансии актуальны. Ниже привожу ссылки на вакансии. Инженер-программист 2 категории Инженер-программист 2 категории (программист ПЛИС/FPGA Designer)

-

Вакансии актуальны. Приведу ниже ссылки на вакансии. Инженер 1 категории Ведущий инженер-разработчик Ведущий инженер-схемотехник

-

Я оперирую обычно к документации на Quartus/Vivado. "Intel® Quartus® Prime Pro Edition Software and Device Support Release Notes". Table 1. Memory Requirements for Processing Designs

-

Абсолютно верно! Не советую прыгать на новую версию для этих камней. А по поводу размером - что эта информация вам даст? Я с таким часто сталкивался, но в итоге, если проект утаптывается в объём и проходит временные ограничения - то мне всё равно - 15% или 25%. Не думаю, что от этого критически изменится потребление. П.С. - вангую, что есть в проекте IP блоки. Их пересборка под новую версию и привела к росту проекта. В IP блоках что-то улучшили и допилили согласно Errdata.

-

Добрый день! А где находитесь территориально?

-

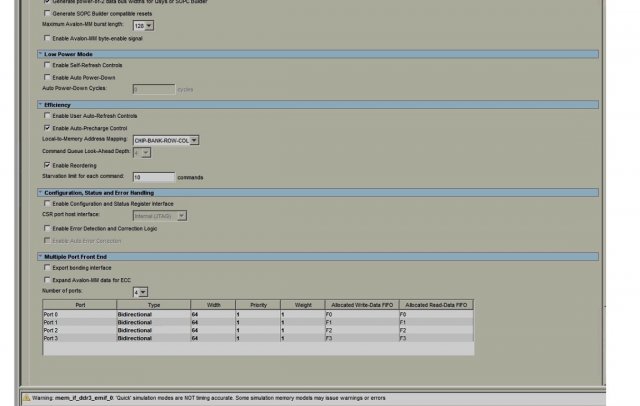

Приветствую! Вот пример - в Qsys система, где есть переход между AMBA AXI И вот таким многопортовым контроллером памяти. Как только по Ambа заканчивается транзакция - формируется bresp, а данные ещё бегут по аванолу в фифо соответствующего порта - и это поток. А с другого порта (пустого) мой блок тестирования сразу начинает читать. В Quartus 10 pro уже другой контроллер памяти и там такого не получится, но вот раньше возможность создать гонки при доступе к памяти была!

-

Добрый день! Добавлю ложку дёгтя. Не помню, как у Xilinx Но у Intel есть возможность включения режима reordering для контроллеров DDR. Если стек задать большим и очереди фифо в памяти ПЛИС установить жирные, то интерфейс контроллера DDR - AMBa AXI4 выдаст последний BVALID, однако данных в самой памяти физически ещё не будет! В ПЛИС я успевал вычитывать из памяти старые данные, ибо лез туда, куда "не долетели" данные из очереди фифо. Однако это было тестирование ради тестирования. Когда за дело брался ARM процессор - данные давно уже были по своим адресам.

-

Это к вопросу толерантности и отказа от термина Slave. Жуть конечно...

-

Помощь в отладке платы

warrior-2001 ответил oxid тема в Предлагаю работу

А разве не увеличили до 2'20? По теме - локация автора темы не указана? Куда ехать на осмотр устройства?- 14 ответов

-

Действительно. Подзабыл я уже об этом.

-

Версия САПР какая? У 10 Арии плавающая точка аппаратная, в отличие от Xilinx. Странное что-то у вас получилось...

-

Может вы не так с ними дружите? На форуме были их представители. Сейчас Mentor могут купить и те, кто якобы "не может его купить по политическим причинам"! Если что - могу выдать контакты в личку.

-

Как странно. Пользователи Altera/Intel и не знаю о такой проблеме с SignalTap. Если это не баг Vivado - то это знатный камень в разработчиков, отвечающих за механизмы отладки прошивок ПЛИС у Xilinx. Подобную ошибку разве не обсуждали на форумах Xilinx? Где тут у нас активные пользователи Хилых?

-

Если хотя бы один трансивер в банке задействован в режиме bonding, то далеко не факт, что оставшиеся трансиверы можно использовать с другим клоком и в другом режиме. Quartus по этому поводу как минимум warning должен выдавать. Посему начните с полного анализа лога!