eugen_pcad_ru

-

Постов

695 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные eugen_pcad_ru

-

-

Единого рецепта нет. Похожие темы уже обсуждались.

-

Полные наименования ссылок - это правильно. Беда в инерционности мышления контроллеров и согласователей. Предлагаю не спорить с ними и сделать как требуют. Но если уж хотите поспорить, пишите служебную записку, и пусть на ней напишут резолюцию "руководстововаться ОСТ (или ГОСТ) таким-то". Вы в этом случае себя прикрываете.

-

1 SVF подходит для JTAG-a.

2 Проще всего грузить по спиай файлом rbf.

3 Гарантированное число перепрошивок макса 100 раз (по факту может быть и больше)

4 В случае пропадания питания, зависит от характера пропадания. Например, если сначала заискрит (скажем в розетке) потом пропадет (в процессе прошивки). По плис можно и потерять/

-

Может быть Вам имеет смысл работать с числами с фиксированной (не плавающей) точкой?

-

Всем привет!

Пытаюсь разобраться с простым проектом под fx3 суusb3014 (см. архив "fx3.zip").

С записью вроде всё понятно. Проблема с чтением. При любой попытке чтения считываю нули и получаю ошибку типа

"BULK IN transfer failed with Error Code:997". Предполагаю, что это связано с тем, что сигнал RD никогда не устанавливается в "1".

К сожалению, временной диаграммы в проекте нет.

Может ли кто-либо по коду пояснить, как нужно "завести" проект в режиме чтения (fx -> host)?

Заранее спасибо за любые рекомендации и ответы!

С уважением,

Евгений

-

Сигнал реальный с выхода ацп? Может присутствовать постоянка как результат оцифровки. Если критично, вычитайте. Была какая-то книга по разъяснению этого эффекта... если нужна, пишите в личку.

-

Алгоритм Герцеля не подойдет?

-

Всем привет!

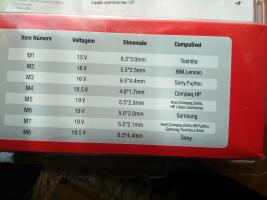

В продаже активно продаются универсальные источники питания для ноутбуков (см. например rexant.jpg).

В комплекте к ним идут несколько часто используемых адаптеров (см. adapters.jpg).

Кто-нибудь может подсказать наименования (артикулы) разъемов и (или) ответных частей в ноутбуках?

Заранее спасибо за любую информацию!

С уважением,

Евгений

-

Добрый день Golikov A., еще раз.

Был реализован проект на базе Virtex5FX70T (внутри PowerPC), в качестве конфигурационной флэшки XCF128XFTG64C,

подключенная по параллельной шине.

В программе PowerPC была реализована функция приема новой прошивки по PCIe, сохранение ее в DDR2, а потом перепрошивки флэш.

Реально работает.

Думаю, аналогично можно что-то похожее реализовать и на Спартане6, вставив в проект, например Microblaze простенькой конфигурации.

С Альтерой не работал, советовать не берусь.

Удачи.

2Andrew Su:

Virtex5FX70T и XCF128XFTG64C были в одной JTAG-цепочке? Служебными ножками ПЛИС дергала при записи в XCF?

-

№2 предпочтителен. К сожалению, в сложных проектах не всегда возможен. Пришел к необходимости замены ПЛИС с б0льшим числом глобальных тактов.

-

12 рублей?

-

Всем доброго дня!

Ищу информацию на ГК199-ТС ТУ 6329-082-07614320-11 производства компании Морион (http://www.morion.com.ru).

Лучше всего ТУ. Или хотя бы схему включения и пояснение использования пина Uупр.

Заранее спасибо всем откликнувшимся!

P.S.: Краткое описание с сайта производителя прилагаю (42, ГК199-ТС.pdf).

-

В таблице 2 речь идет о функциональном назначении элемента, располагаемом на основном поле УГО.

То есть формально можно обозначить элемент как DA, а на его поле проставить TR.

ИМХО также можно разрисовать упрощенную схему и обвести ее прямоугольником. То есть так как у Вас, тоже правильно.

-

Спасибо! В сторону конвейера смотрел. Но этот вариант оставил на "после экспериментов с DSP".

Буду пробовать.

-

Схемы типа "не устанавливать", по ЕСКД не проходят. Делайте варианты исполнения.

-

Итак, в итоге:

зубры типа Ментора и Альтиума курят в сторонке от ГОСТов. Для выпуска документации по ЕСКД используются либо устаревшие либо малоизвестные пакеты.

Всем спасибо!

P.S.: Забавно, что на форумах Ментора предлагают пути обхода ГОСТов и приобретения лицензии.

-

Основная задача модуля состоит в вычислении выражения

"Count := (Count + stdv_to_nat(step)) mod Modulus;"

Все остальное по большому счету не нужно.

Попробую переделать с учетом рекомендаций.

А еще был бы не плох пример с использованием предлагаемой выше конструкции

"accum <= accum + sxt(data, 48)"

с использованием DSP и без использования.

P.S.: Критика хороша. Но к сожалению пока дельных советов по теме вопроса не увидел.

-

2Amurak: Пусть будет "не простенький" ;)

-

Может дело в топологии печатной платы? Экран хотя бы в виде крышки присутствует?

-

Всем доброго времени суток!

Написал под Spartan-6 на VHDL простенький аккумулятор (код прилагаю).

Но с целью повышения рабочей частоты (разрядность 30 бит, частота где-то 100 МГц) возникла идея задействовать для этих целей встроенные блоки DSP48A.

Добавил еще две строки

attribute USE_DSP48: string;

attribute USE_DSP48 of simple_accum: entity is "yes";

(в прилагаемом файле они закомментированы).

В Summary от ISE 14.7 появляются блоки DSP, но в большом количестве (34 из 180). Да и частоту не удалось повысить.

По всей видимости что-то делаю не так.

Прошу помощи.

Заранее спасибо за любые рекомендации по оптимизации кода с целью повышения быстродействия!

-

Два... :) https://yandex.ru/search/?text=autocad&...=9582&lr=11

Вот пример из Пульсоникса:

Почти никаких ограничений на набор сеток, толщин линий, диаметров точек соединений, количество альтернативных символов и футпринтов, углы поворота, выбор текстовых символов разделителей (гейтов,пинов), шрифт ISOCPEUR.

Вход в шину можно сделать прямым, если задать 0 размер скоса, но тогда он имя цепи тоже прилепит без отступа, но можно потом группой выделить и подвинуть.

Так, возник смежный вопрос. В шаблоне основной подписи есть слова Rev., Signature и т.п. Это тоже сейчас по какому-то госту?

-

Всем доброго времени суток!

Рисую схемы, сдаю по ЕСКД. В связи с долгой эксплуатацией пикада и набора утилит выпускаю документы, полностью пригодные для проверки нормоконтролем.

Спустя почти 10 лет после прекращения поддержки PCAD-а, решил пересесть на что-то поновее.

Бегло просмотрел два пакета: 1) Alium Designer и 2) Expedition Enterprise (DxDesigner) от Mentor Graphics.

Что неприятно удивило:

В альтиуме пропала возможность задания произвольных толщин линий (по ЕСКД 0,3мм...0,4мм), в DxDesigner-e в компоненте нельзя использовать произвольный (в т.ч. русский) шрифт и вводы в шину отмечаются маркерами, которых к сожалению также нет в ЕСКД.

Теперь собственно вопрос:

Сдает ли кто-либо по ЕСКД "чистые" схемы (без ретуширования и прочих никому не нужных операций), разработанные непосредственно в схемных редакторах Altium-а или DxDesigner-а? Если сдаете, поделитесь пожалуйста "вырезками" из схем, скажем в pdf-формате демонстрацией основных оформительских камней с сохранением масштаба 1:1 для удобства просмотра:

1 компонент с использованием русских шрифтов,

2 линии вводы в шину (толщиной 0,3мм...0,4мм)

3 просто соединение линий (размер точки)

4 внешний вид позиционных обозначений и наименований цепей (обычное и повернутое)

5 использование разнесенного позиционного обозначения (автоматически с использованием знака ".")

и т.п.

Заранее спасибо!

P.S.: Зачем это мне нужно? Для фокусировки работы по изучению САПРа, лучше всего удовлетворяющего требованиям ЕСКД. Ссылки на дополнительные справочные материалы типа "Шпаргалка по переходу с пакета PCAD200Х на пакет ..." приветствуютсяsm.gif

P.P.S.: Если кто-либо использует другие пакеты, не описанные мной выше, также буду рад посмотреть на их результаты.

P.P.P.S.: Мнение "Да не надо заморачиваться, проще уговорить нк пропустить схему в таком виде" знаю и прошу тут не дублировать.

-

А клемники задействовать не вариант?

-

Вариант 1

Формируется общая часть, в ней перечисляются элементы, которые есть всегда.

Затем пишется АБВГ.ЧЧЧЧЧЧ.ЧЧЧ-01

и далее пишутся элементы (и их количество) для первого варианта имсполнения

и т.д.

Количество листов в спецификации не ограничено. "Не влезет" непонятно почему.

Вариант 2

Разрабатывается формально новое изделие со своим комплектом ЕСКД.

Что лучше, зависит от способа сдачи (проведения испытаний, согласования документации и т.п.)

Как-то так наверное.

P.S.: Лично мне второй вариант нравится больше. Потому как каждый раз в трудоемкость закладывается новая разработка (документации). А корректировка существующей по 1-му варианту(а ее будет много, тут никуда не денешься) формально отрицательно сказывается на результативности работы, так как показатель качества работы напрямую зависит от числа выпускаемых извещений.

P.P.S.: А, еще забыл: для варианта 1 на Э3 должны быть приведены ВСЕ элементы групповой спецификации. То есть к примеру если у Вас допустима замена микросхемы, то на схеме их должно быть две, что также приводит к "нечитаемости" схемы.

Среда разработки pBlaze IDE: где ее можно достать?

в Среды разработки - обсуждаем САПРы

Опубликовано · Пожаловаться

Есть. Поищу, выложу.