eugen_pcad_ru

-

Постов

698 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные eugen_pcad_ru

-

-

Автору топика: не делайте предлагаемого. Как потом настраивать, ловить коллизии, исключать ошибки на шине в ответ на 'неинтерфейсные' посылки со стороны мк и т.п.?

-

Где как принято' так и пишите. Нервы будут целее и аппетит лучше, а ответственность за качество документации несёт самоконтроль)

-

У малогабаритных разъемов маленький ресурс надежности (количество циклов сопряжений). Я бы взял любой разъем от аккумулятора смартфона.

-

На чём отлаживали, то и применяйте. Будет меньше проблем при настройке.

-

Меряете число переходов за фиксированную единицу времени, получаемую от другого точно известного опрника и усредняете результат. Точность оценки зависит от времени усреднения. И от частоты точно известного опорника. И никаких гигагерцев.

Вообще полистайте на досуге описание работы частотомеров, всё станет понятнее.

-

А что Вас смущает с разъемом? Есть например160-тиконтактные vme-розетки, в которые можно воткнуть 96-тиконтактные вилки. И это один из вариантов допустимых подключений. В большее можно воткнуть меньшее. Наоборот сложнее ))

-

http://xc3sprog.sourceforge.net

3-й спартан прошивал из командной строки. Через параллельный порт.

Только идея посадить чайника, чтобы прошивать плис, нежизнеспособна.

-

On 1/31/2019 at 9:56 PM, shunix said:

Во всех спорах правым окажется нормоконтроль. Лучше не нагромаждать кучу шрифтов в документах. Гостовские вполне подходят для единообразия.

P.S.: Из своего опыта знаю, как тяжело поддерживать впоследствии электронные документы с большим количеством шрифтов. А ещё лучше, если шрифты будут согласованы с заказчиком в руководящих указаниях по конструированию (РУК).

-

Да, принцип Покрышкина: один сбивает, другие загоняют )

Иногда проект ведется поэтапно. Одновременная правка проекта приводила к непонятным результатам.

-

1. Просто в проекте на каком либо символе, относящемся к FPGA ставится атрибут Type значение FPGA. После этого выполнив ПКМ>FPGA/HDL>Optimize_FPGA можно войти в IOPT для оптимизации назначения выводов плис, а также редактирования размещения остальных компонентов на плате.

Если FPGA не какая-то отечественная экзотика, то наверняка будет доступна для выбора. Нарисовать не получится, т.к. там в библиотеке еще кучу правил задают в специализированном закрытом формате.

2. Да.

Спасибо!

-

1. При перестановках пинов в FPGA I/O Optimizer (или I/O Designer) автоматом отслеживается правильность назначения сигналов по их типам - т.е. он например просто не даст засунуть сигнал в банк не с тем типом питания.

2. Есть также Xpedition Valydateс помощью которого можно быстро произвести различные проверки правильности схемы.

1 для IO-оптимайзера-дизайнера нужен проект под плис? и что делать, если в библиотеке io-оптимайзера-дизайнера нет нужной плис? самому нарисовать можно?

2 на сайте производителя "Your search for “Valydate” within mentor.com produced about 0 results". Если идти по ссылке, попадаю на "Schematic Integrity Analysis". Это оно?

-

Всем привет! Относительно недавно начал осваивать Xpedition Designer, прошу сильно не пинать) И чтобы не изобретать велосипед, прошу поделиться своим опытом у коллективного разума.

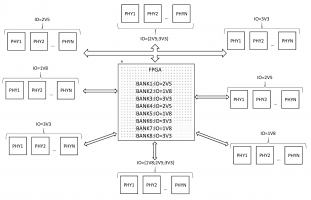

Нарисовал сложную схему в Xpedition Designer от Mentor Graphics. Для примера возьмем одну ПЛИС с несколькими банками и кучкой периферии. Естественно, уровни логики у всех разные. Есть периферия с толерантным управлением (см. рисунок). Далее проект отправляю на разводку, и там некритичная низкоскоростная периферия может изменить своё место. Конструктор раскидывает элементы по плате и ему тогда проще не тянуть сигналы через всю плис, а поменять метами на самой плис. Надеюсь, объяснил доходчиво)

После предварительной компоновки я вручную проверяю соответствие всех уровней логики. Потом еще по каким-то соображениям (изменение ширины платы под другой типоразмер корпуса, добавление радиаторов, вырезов в плате и т.п.) происходит перекомпоновка. В общем зачастую происходит несколько таких итераций и конечно в сжатые сроки) Со временем глаз "замыливается", и после второй-третьей проверки можно легко допустить ошибку: завести на 1,8В-периферию управление от 2,5В-банка; на разъем сопряжения с другими модулями тоже протянуть не те уровни и т.п. Сложность схем растет, количество периферийных микросхем тоже, ну и число ошибок от них не отстает)

Так вот собственно вопрос: кто как решает задачу автоматизации проверки? Есть такое в стандартных средствах от Mentor Graphics? Может какие скрипты применяются и т.п.?

Заранее спасибо за любые дельные советы!

-

Муторное это дело... полного аналога DNI нет. Проще всего вариант исполнения.

-

Дефолтного значения не увидел... его нет?

-

А подавать питание на осциллограф через удлиннитель, не имеющий 'земляной' шины. Не подходит?

-

Хм... Думается мне, что физически Вы получите бумажку с кодом или компакт-диск. Так как строго говоря файл не является чем-то материальным. А при покупке должна быть передана материальная ценность. Так по российским законам.

Поправьте меня юристы пожалуйста, если я не прав.

-

Для Э4 пакет не предназначен.

-

В документации Вам необходимо указать наименование и обозначение. Думаю можно просто 'X розетка'. Ну или что там по госту на уго, не помню.

-

Не совместимы. А у Вас драйвер под нужный дисплей есть? Под какую ОС?

-

Max2plus- ом пробовать надо. Если защита установлена, считаете файл с единицами.

-

Тока не хватает?

-

Если уж автор поднимает тему о "философии HDL-дизайна", то обсуждать ее надо с философами :-)

А тут чаще обсуждают практические вопросы реализации...

-

Распространяется. Аргументы Вы привели выше.

-

Программатор фирменный? Если китайский, там могут быть чудеса...

UZ или G

в Документация

Опубликовано · Пожаловаться

Упс, ошибся, голова была занята другим )

НОРМОКОНТРОЛЬ несёт ответственность за качество выпущенного документа.