-

Постов

3 012 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент GenaSPB

-

написано же... 128 килобайт. А про зависимость от размера был тест ранее, результаты выше - Да, после 64 кБ не сильно влияет. upd: в режиме софтового опроса: USB FLASH: Write speed 5622 kB/S HDD: Write speed 20097 kB/S (через USB -> SATA переходник, напомню)

-

Да у меня тоже можно в опросе проверять. Чаще всего оде несколько ускоряет - так как всё это изначально под super loop предназначено.

-

Я тольуо запись тестирую - 128k block writes через FatFS

-

И как неплохой результат: LUN #0: Inquiry Vendor : Hitachi Inquiry Product : HTS542512K9SA00 Inquiry Version : MSC Device ready MSC Device capacity : 117220824 KBytes Block number : 234441648 Block Size : 512 Это устройство даёт не менее 4 бегабайт в секунду на EHCI.

-

USBCMD, биты 23:16 - "interrupt treshold control" upd: убрал у всех элементов ASYNC флаг EHCI_CHR_HEAD - стало 3.7 мегабайта в секунду... Уже чувствуется USB HS

-

Изменив параметр "частота прерываний от контроллера" 8 на 1 - для получения прерывания по окончании обмена - получил вместо 400 килобайт скорость 2.5 мегабайта в секунду на USB FLASH. SATA HDD чуть позже.

-

Напомню - вот результаты моих тестов того же фреймворка, но на USB_OTG. Никаких потоков, просто суперцикл. Это Middleware от ST. Получить бы такую же скорость и можно считать повезло.

-

Разобрался... Надо не мешать самому EHCI toggle выполнять. В пределах каждого ендпоинта. Последовательность обеспечивает ST Middleware. Первая попытка - получилась скорость записи на флешку около 400 килобайт в секунду. Осталось раз в дсять ускорить.

-

Уточняю вопрос... ПРоисходит вот что: посде енумерации и выбора конфигурации в USB FLASH накопитель через BULK OUT endpoint идет первый INQUIRY запрос... Судя по статусу успешно. Но последующее чтение из IN endpoint не дожидается ответа. Вчитавшись в документацию, увидел рекомендацию HIGH SPEED OUT запросы предварять PING. Соответствующий флаг middleware даёт. Вопрос - EHCI transfer descriptor имеет флаг включения PING протокола - иадо ли разбивать такой обмен на два transfer descriptor - один без данных и с флагом PING и второй обычный OUT - или контроллер сам обрабатывает такое - и достаточно в OUT выставить соответствющий бит? Старз скажу - мне не помог второй вариант получить ответ от USB FLASH...

-

Интерфейс используется на один канал OTH_HS - потому это оттестировать удалось ранее.. Я вот уткнулся в то что транзакция IN по не контрол EP не стартует... OUT нормально. Енумерация по EP0 в лёт идет... Могу предоставить дамп - содержимое единственного элемента очереди асинхронных транзакций.

-

bare-metal обслуживание USB HOST на EHCI начало подавать признаки жизни... В составе ST USB HOST Middleware. Помогла дока от ColdFire с примерами дескрипторов для EHCI. И недавняя поездка к коллеге у которого есть LeCroy с блоком анализа USB сигналов. Дальше уже на более высоком уровне решать проблемы придется. А то в течении долгого времени получал после некоторых своих действий остановку передачи SOF пакетов. Сделал диагностическое USB device на это состояние и за день всё заработало. Так что обслуживание USB FLASH в составе Аиста скоро уже...

-

Не в курсе... хрустального шара нет.

-

Нашелся проект... https://github.com/mori-br/STM32F4HUB Не проверял.

-

Аналог - NFM? Цифра - QAM? В этих случаях требования к линейности разные. КПД разное. Запас по мощности == компоненты разные.

-

Не? DRA818V.pdf И еще всякие сборки от этого же произволителя

-

Надеюсь, смещением битов перед передачей Вы в программе не занимаетесь? В регистр данных должны попадать значения сэмплов как они есть.

-

В CMSIS давно куски есть... Попробуйте взять за основу: __STATIC_FORCEINLINE uint64_t __SMLSLD (uint32_t op1, uint32_t op2, uint64_t acc) { union llreg_u{ uint32_t w32[2]; uint64_t w64; } llr; llr.w64 = acc; #ifndef __ARMEB__ /* Little endian */ __ASM volatile ("smlsld %0, %1, %2, %3" : "=r" (llr.w32[0]), "=r" (llr.w32[1]): "r" (op1), "r" (op2) , "0" (llr.w32[0]), "1" (llr.w32[1]) ); #else /* Big endian */ __ASM volatile ("smlsld %0, %1, %2, %3" : "=r" (llr.w32[1]), "=r" (llr.w32[0]): "r" (op1), "r" (op2) , "0" (llr.w32[1]), "1" (llr.w32[0]) ); #endif return(llr.w64); }

- 10 ответов

-

- arm cortex-m3

- gcc

-

(и ещё 1 )

C тегом:

-

У Вас будет миллион раз прерывание... или десяток тысяч. Про номер прерыванмя читайте даташит. Вы собираетесь обрабатывать PA1 а упоминаете 9..5

-

Ограничьте ток через светодиод... Что ещё за причирны выхода из строя беспокоят? Кнопки (контакты) имеют "дребезг". Заводить на прерывание плохая идея.

-

В паузах для а-лав гонится спец код который по таблице в "-1" преобразуется. Мю-лав - другой код.

-

cooper pour и plane в пикаде это разные...

-

1) design rules? там не заданы умолчания? 2) проблемные цепи с атрибутом Clearence?

-

Не только. Можно и из массива загрузить. static void devcfg_write(void) { // About format see // PG374 (v1.0) June 3, 2020 // pg374-dfx-controller.pdf // Transfer the data. const uint_fast32_t dma_flags = 0x01; size_t nwords; const uint32_t * const p = getbitimage(& nwords); ASSERT((((uintptr_t) p) % 4) == 0); XDCFG->DMA_SRC_ADDR = (uintptr_t) p | dma_flags; XDCFG->DMA_DST_ADDR = 0xFFFFFFFF; XDCFG->DMA_SRC_LEN = nwords; XDCFG->DMA_DST_LEN = 0; while((XDCFG->INT_STS & XDCFG_INT_STS_DMA_DONE_INT) == 0) ; XDCFG->INT_STS = XDCFG_INT_STS_DMA_DONE_INT; // Clear DMA_DONE status }

-

Обратите внимание на этот дефайн в конфигурации #define FF_LBA64 1 /* This option switches support for 64-bit LBA. (0:Disable or 1:Enable) / To enable the 64-bit LBA, also exFAT needs to be enabled. (FF_FS_EXFAT == 1) */

-

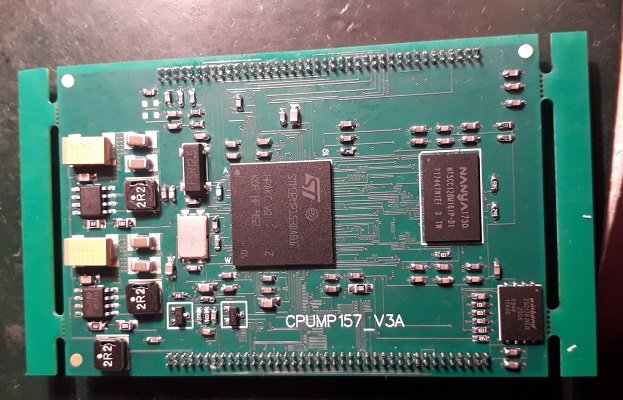

Тот самый Cortex-A7 dual core на 800 МГц. Пока вроде лежит https://www.chipdip.ru/product/stm32mp153fab1 - и не имеет тенденции исчезать вроде.