-

Постов

3 009 -

Зарегистрирован

-

Посещение

-

Победитель дней

2

Весь контент GenaSPB

-

Как раз с хабом включено всегда. Лог. У меня нет нотификаций с хаба - флешку вклчать до запуска. Кстати, нашлась usbphy0 (+0x400 от DRD) - возможно и EHCI на 0-м порту и USB DRD заработает после запуска без XFEL, из QSOI). Изменения в github

-

У меня система (упрввляющая/обрабатывающая звук программа SDR радиостанции) крутится в вариантах для двухядерных STM32MP157, ZYNQ 7020 и сейчас макет на Allwinner t113-s3. Все кеши работают, так же работают спинлоки в общей памяти для разделения доступа к ресурсам когда надо... И без мейлбоксов. Что я делаю не так?

-

Барьер вносить в каждое обращение? А strong ordered отменили уже?

-

Host я запустил давно на ehci. От второго мне device нужен

-

#define ENCODER_BITS (ENCODER_BITA | ENCODER_BITB) #define ENCODER2_BITS (ENCODER2_BITA | ENCODER2_BITB) #define ENCODER_INITIALIZE() \ do { \ arm_hardware_piog_inputs(ENCODER_BITS); \ arm_hardware_piog_updown(ENCODER_BITS, 0); \ arm_hardware_piog_onchangeinterrupt(ENCODER_BITS, ENCODER_BITS, ENCODER_BITS, ARM_OVERREALTIME_PRIORITY, TARGETCPU_OVRT); \ arm_hardware_piog_inputs(ENCODER2_BITS); \ arm_hardware_piog_updown(ENCODER2_BITS, 0); \ arm_hardware_piog_onchangeinterrupt(0 * ENCODER2_BITS, ENCODER2_BITS, ENCODER2_BITS, ARM_OVERREALTIME_PRIORITY, TARGETCPU_OVRT); \ } while (0) Использовать cmsis описание регистров не обязательно использовать их стиль инициализации периферии. Вот как например можно... Отвечал с телефона, строки повставлялись пустые... Unix/type.h нет в комплектах none-eabi. А stdint.h есть

-

Это не индусы. Это стиль CMSIS. Рекомендации есть или нет в печатном виде не знаю. А я тут долблю usb drd. Прерывания по bus reset и остальному идут, но почему-то не установить младший бит в регистре разрешения прерываний от ендпоинтов по приёму. Pull up включаю.

-

Это наследие из уникса. Тем часто еще промежуточный уровень буферизации появляется. Я так к cmsis style принятому в баре метал привожу с помощью самописнойт утилиты. Явно существуют где то инструменты для генерации таких заголовочников и svd файлов для отладки. Но пока делаю как могу. Понятно можно расширить описанием битов для получения xxx_Msk и xxx_Pos. Но пока не хочется. Хоть кому-то тут пригодился мой cmsis header? Вот и ответ. repstosw, откройте для себя stdint.h специально для нас с вами придумано.

-

Продолжаю приукрашивать https://github.com/ua1arn/hftrx/blob/develop/src/sdram/t113_ddr_decompiled.c Проставляю где надо volatile - когда идет обращение к регистрам

-

Или хотя-бы не начинать следующую пока ранее начатая не закончится.

-

Ожидание сбросов двух reset битов требуется. И после выдачи команды перед тем как ожидать статуса надо бы дождаться сброса бита запуска.

-

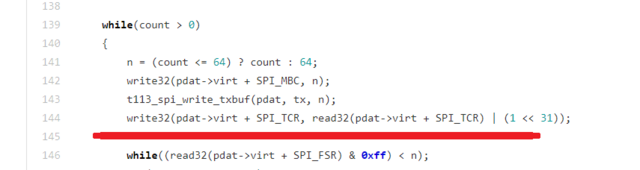

ДА, выдача бита 31 в регистре SMHC_CMD (CMD_LOAD) требует дождаться пока он снимется. Потом ждем разных статусов. То что там нигде на дожидаются сброса FIFO_RST или SOFT_RST после выдачи SDXC_HARDWARE_RESET - включающей эти биты - сразу бросается в глаза. т.е. одиночная ошибка - вызывающая отработку ветки со сбросом - следующая быстрая выдача команды встретит нерабочий host. Вот про SPI - где помечено красным надо ждать сброса бита запуска - иначе быстро не работает.

-

Внутири sdhci_t113_transfer что именно ожидаем? Я встречал некоторую неаккуратность в qspi драйвере (из исходников xfel). Устанавливался бит запуска обмена и дожидались появления запрошенного количества в выходном fifo. При повторном БЫСТРОМ вызове висло. Выяснилось - надо дождаться исчезновения бита запуска. Может и тут такое же упрощение?

-

У кого есть инфа про то - что за какой блок отвечает? Чтобы понять каким блокам ставить размер всего экрана а каким заполняемой области? ps: это еще к копированию не приступал

-

Проверил после подсказки... вертикальные линии или прямоугольники в один пиксель g2d сейчас не заполняет. Вместо этого рисует горизонтальную линию такого же размера (на вид) и не выставляется прерывание по готовности. Горизонтальные линии нормально.

-

оставил своё и добавил ваше - помогло. Но вообще где-то должен быть способ по настоящему синхронизироваться, не в ручную ловить момент. Т.е. как в STM32 LTDC и Renessas VD5: выставил в регистр новый адрес страницы, дождался когда дисплей на него перейдет - и все, поехал заполнять старый буфер.

-

Это как раз надеюсь на синхронизацию с vsync

-

Я попытался сделать: В dbuff ставится младший бит и ждем пока снимется. Но судя по иногда промаргивающему изображению, это не то... write32((uintptr_t) & glb->dbuff, 0x01uL); // 1: register value be ready for update (self-cleaning bit) while ((read32((uintptr_t) & glb->dbuff) & 0x01uL) != 0) ; // Allwinner_DE2.0_Spec_V1.0 // 5.10.3.4 Blender // GLB struct de_glb_t { uint32_t ctl; /** Offset 0x000 Global control register */ uint32_t status; /** Offset 0x004 Global status register */ uint32_t dbuff; /** Offset 0x008 Global double buffer control register */ uint32_t size; /** Offset 0x00C Global size register */ };

-

RX FIFO = 512 * 4 - Уточните какой у вас на процессоре размер памяти есть. Да, DMA есть только на тех где 4К

-

Есть только это: // 3.4.2.4 CPU0 Hotplug Process // // The Hotplug Flag Register is 0x070005C0. // The Soft Entry Address Register is 0x070005C4. // 3.4.2.3 NON_CPU0 Boot Process // // The Soft Entry Address Register of CPU0 is 0x070005C4 // The Soft Entry Address Register of CPU1 is 0x070005C8

-

Представьте нет. Разрешить работу VFP/NEON заранее... Ну это все кстати в CMSIS в ините процессора делается

-

Именно так. Для начала можете глянуть по ссылке, которую вы сами же привели.

-

Крутой прорыв тут:

-

На данный момент так (для CMSIS): system_allwnr_t113s3.h allwnr_t113s3.h t113_ddr_decompiled.c

-

Круто! Затащил в свой проект - работает!!!! Буду понемногу комментарии добавлять и приводить к более обычному виду исходника. СПАСИБО!