Andr2I

Свой-

Постов

380 -

Зарегистрирован

-

Посещение

Весь контент Andr2I

-

Вы совершенно правы - поставил сетку 1ps и увидел сдвиг. Спасибо!

-

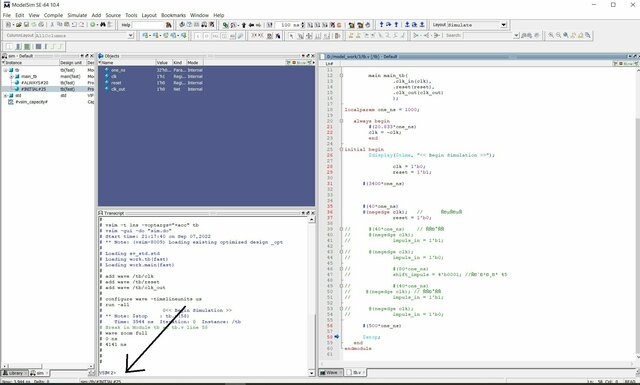

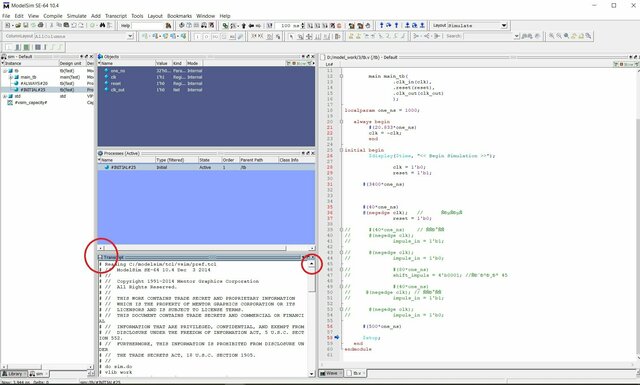

В тест бенче стандартно указываю `timescale 1ps / 1ps В .do файле vsim -t 1ns -voptargs="+acc" tb

-

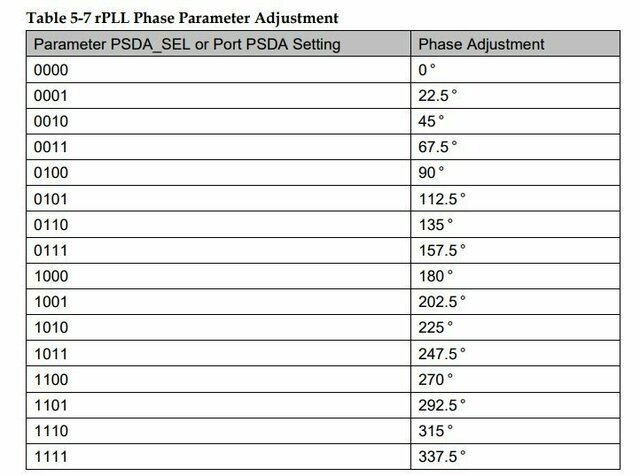

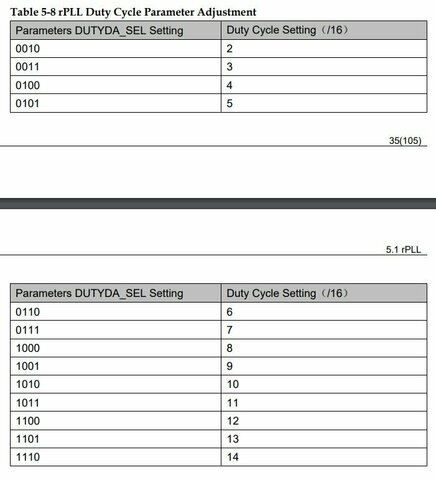

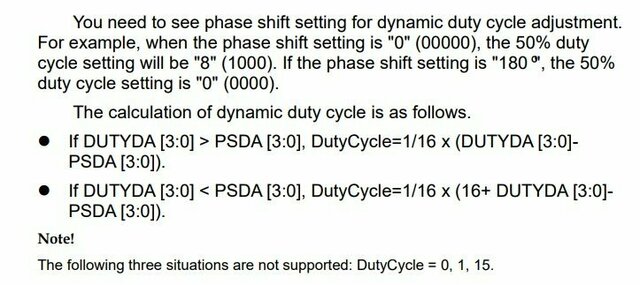

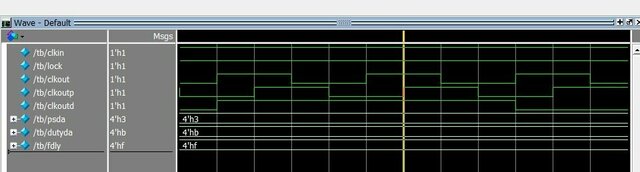

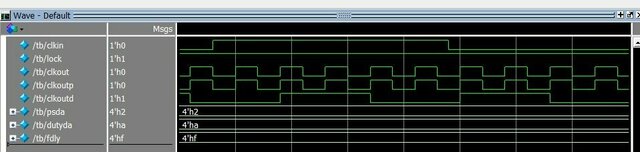

Спасибо всем ответившим! Мне удалось скормить Modelsim-у rPLL и посмотреть результаты. Но столкнулся с непонятным поведением rPLL. Я сконфигурировал ее с динамическим изменением фазы и захотел посмотреть как будет меняться фазовый сдвиг. Если сдвига нет, то все хорошо. Сдвиг на 90 градусов, тоже нормально. А вот между... Задаю сдвиг 67,5 градусов, а получаю такой же как и 90 градусов. Вроде все делаю по букварю Еще чуднее при сдвиге 45 градусов С чем это может быть связано? - моя криворукость или особенности китайской модели? - или это и в железе так?( rpll1.v sim.bat sim.do tb.v

-

Вероятно, глупость спрашиваю - если описание модуля целиком на verilog без использования примитивов, то что нужно взять из проекта GOWIN для временного моделирования?

-

Огромное спасибо! Счастье уже наступило - можно редактировать файлы и запускать моделирование без закрывания Modelsim. Сигналы выводится. Ни на что не ругается!

-

У меня такого точно нет) Приглашение есть. Для "особо одаренных", что вставить то нужно? После restart в закладке Симуляции Modelsim рисовать сигналы отказывается. Рисует только если запускаешь .bat файл.

-

Т.е. мне нужно прямо в папке GOWIN -а провести компиляцию с помощью Modelsim. Modelsim просит создать там папку Work - создавать? Это однократная процедура или каждый раз перед запуском .bat файла? Файл vsim.vlf? - у меня нет приложения, завязанного на него(

-

А где Вы его взяли? Из Вашего проекта или из папок GOWIN-а?

-

"Нельзя объять необъятное" Честно говоря, и не хочу. Я понимаю, что там кусок кода Modelsim, который люди специально обрезали и сделали удобным для работы. Гвозди можно забивать и молотком без ручки. Но зачем? - с ручкой мне удобнее))) И у меня все влезает в Спартан-6. Дорогие они шибко стали))) Это интересно. По мере погружения буду спрашивать. Насколько я понял, после беглого просмотра, QuestaSim заточена под sverilog. Мне он на данный момент не нужен. Хватает verilog. Modelsim побыстрее работает. Меньше весит. Из тех же соображений была и версия выбрана - мне бантиков не нужно. Каждый бантик отжирает быстродействие и ресурсы. Ничего тайного))). Все предельно просто. Пишу в блокноте. После ISE - тошнит... Функционального моделирования мне пока хватает. С DO-254 не работаю. 3.zip Обе нажимал. Ничего не происходит. Окно могу закрыть. Но Modelsim в следующий раз запускается по новой.

-

Правильно я понимаю, нужно из установленного GOWIN скопировать 2 файла GOWIN\IDE\simlib\gw1n\prim_sim.v и prim_tsim.v (если мне нужен gw1n) в рабочую папку WORK Modelsim и скомпелировать Modelmом? А в эту кучу пихать свои верилоговские файлы и макросы? Интересно конечно. Существует GUI, который за меня все макросы пишет, а я только тестбенч создаю в нормальном редакторе, а не в блокноте? Чувствую, что все не так безоблачно)))

-

Здравствуйте! Пытаюсь в фоновом режиме) разобраться с аналогичной задачкой - промоделировать rPLL. Для меня это довольно сложно, поскольку с ПЛИС постоянно не работаю и ранее мне хватало встроенного симулятора что для Altera, что для Xilinx. В последних версиях ПО это все убрали, но кристаллы у меня старенькие и софт аналогичный). Конечно в меня сейчас тапкой бросят))) - это совсем не кошерно, но мне всего хватало. Зато как было удобно... Написал и сразу отмоделировал. Для Gowin пришлось осваивать внешнее моделирование(. Поскольку использую верилог и всего хватает, поставил Modelsim 10.4. С песнями и бубном освоил пакетный режим и поведенческое моделирование. Вычитывание и правка .do файлов сильно не нравится, но... Еще больше напрягает, что при запуске .bat файла Modelsim каждый раз запускается вновь. Может знаете способ без перезапуска или что написать в .bat , что бы старое окно закрывалось? Но самое главное, не могли бы Вы поделиться полным набором файлов, которые Вы использовали для скармливания Questa rPLL? Включая common_tb_pkg::*; gowin_rpll_tb_pkg::*; Предполагаю, что последний создается GOWINом?

-

Добрый день! Не поделитесь результатами дальнейших попыток - удалось залить по SSPI? Есть желание вообще не разводить JTAG.

-

Есть большое подозрение, что при партии 100шт. буду послан далеко и надолго))) Самое интересное, что ни на aliexpress, ни на alibaba я не нашел их. lcsc.com тоже не показывает( P.S. Когда писал вопрос допустил ошибку - нужна мне простая GW2A-LV18LQ144C8/I7, а в наличии с непонятной в будущем доступностью GW2AR-LV18EQ144PC8/I7

-

Здравствуйте! Присматривая замену младшему Спартану 6 натолкнулся на Gowin. По параметрам как бы устраивает, но вопрос возник по доступности. После запросов поставщикам для GW2AR-LV18LQ144C8/I7 появилась цена 6000р. В тоже время для GW2AR-LV18EQ144PC8/I7 цена в elitane 1200-1500р. Странно - добавлено памяти 64мбит, а цена ниже. Какие могут быть причины: 1) это складские остатки. 2) Gowin перестал делать GW2A - ему более интересно делать новые чипы. 3) Чудеса логистики. Может кто поделится соображениями? Заранее благодарен.

-

Здравствуйте! Возможно вы владеет информацией - по какой цене сейчас можно купить GW2A-LV18LQ144C7/I6 или GW2A-LV18EQ144C7/I6 в количестве 20-50шт.? Интересует самый дешевый вариант с паябельным корпусом 144 ноги и шагом 0,5мм

-

"Коммутирующий конденсатор" - это конденсатор с ключами? А как ими управлять для получения синуса? И наконец - куда девается энергия при разрядке этого конденсатора - у синуса есть и фронт и спад?

-

Интересный у Вас демпфер, Алексей! Покрутил в голове - вроде все понятно, но зачем ток демфера проходит через датчик тока? - ведь ключ закрывается по уровню, когда ток через демфер вообще не течет?

-

Все проблемы возникают из-за полей рассеяния. Как правило, прямоходовые преобразователеи понижающие - первичка много витков, вторичка мало. Обмотка размагничивания с тем же количеством витков что и у первички будет лучше магнитосвязана с ней.

-

Чудит Квартус 9.1

Andr2I ответил Andr2I тема в Среды разработки - обсуждаем САПРы

С 2 и 3 вроде доперь :rolleyes: - квартус комперссирует ttf файлы и результат каждый раз непредсказуемо меняется. -

Чудит Квартус 9.1

Andr2I опубликовал тема в Среды разработки - обсуждаем САПРы

Заметил несколько странностей Квартуса 9.1 :laughing: 1) Есть проект под Cyclone2. Сделан в 6.0. Заливается ttf файл с контроллера. Перекомпелил в 9.1 - ерестал работать. Вернулся в 6.0 - все заработало. :rolleyes: 2) Сделал проект вод Cyclone3. Добавляю ячейки - ttf файл уменьшается. И вообще работает через раз - что-то второстепенное добавишь - заработало, уберешь - все стоит вообще. Тактовая частота одна - 128МГц. Критических ворнингов нет. Есть только Warning: Timing-Driven Synthesis is skipped because the Classic Timing Analyzer is turned on Warning: Clock latency analysis for PLL offsets is supported for the current device family, but is not enabled Проект состоит из многих мелких, каждый из которых нормально симмулируется и работает на частоте в 1,5 раза большей. 3) Изменил параметры компиляции с Auto Fit на Standart Fit - ttf файл несколько вырос. -

А что в этом такого страшного? Ну sepic с заполнением больше 0,5, ну и что?

-

Да нет, все правильно. Но у меня при входном 4В выход 5В. Диод шоттки. Заполнение явно больше 0,5. Все работает хорошо!

-

Да, погорячился :rolleyes: - конечно с понижением напряжения заполнение должно увеличиваться. Сбила с толку первая цитата.

-

Подскажите про UС3845

Andr2I ответил SKov тема в Силовая Преобразовательная Техника

+1 Хороший вариант для ТЗ. -

Не подскажите почему? :05: У меня сейчас нормально работает SEPIC на LT1613. Входное напряжение от 4 до 6В, на выходе 5В. Ток около 50 мА. Чудес не наблюдаю. Я так понимаю, при 6В на входе, заполнение больше 0,5.