Beby

Свой-

Постов

659 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Весь контент Beby

-

Предлагаю повнимательней взглянуть на Spartan-3AN. Spartan-3AN - это FPGA (Spartan-3A) со встроенным SPI ROM. У Spartan-3A(N) есть ряд опций по проверке своей прошивки уже после окончания процесса конфигурации. Возможно, они как раз Вам и подойдут. Опции можно посмотреть в Spartan-3 Generation Configuration User Guide в разделе Chapter 16 Configuration CRC.

-

1. Ну, так Вы не совсем то скачали... надо было Schematic Libraries качать. 2. Если ничего не путаю, то ISE 11.x уже не поддерживает Virtex-2 (да и давно пора о нём забыть).

-

Если Ethernet Phy не умеет это компенсировать - то работоспособность никто гарантировать не сможет.

-

Пропадает имя цепи

Beby ответил Koluchiy тема в Среды разработки - обсуждаем САПРы

Близко, но я делал по другому, и в подобной ситуации оно даже работало (!). У меня была такая ситуация: есть один net, но он имеет человеческое имя на верхнем уровне проекта и совсем нечеловеческое иерархическое имя там, где этому net'у присваиваются значения. А мне хотелось, чтобы имя в ChipScope было человеческое. Я использовал constraint SAVE применительно к net'у на верхнем уровне проекта, и в скомпилированном проекте оставалось именно это имя net'а. Работало в ISE 10.1/11.5. На VHDL это выглядело так: attribute S of signal_name: signal is "yes" -

Синхронизатор

Beby ответил AlphaMil тема в Работаем с ПЛИС, области применения, выбор

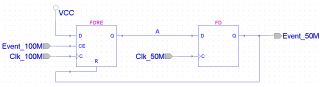

Это хорошо, что от одного генератора. Теперь остаётся уточнить, как Вы получали эти частоты: при помощи DLL ? Хорошо бы схемку (ну или HDL описание) глянуть этого места. Если всё сделать правильно, то и метастабильности не будет - а значит, всё будет тривиально (как функционально моделируется - так и работает,.. если, конечно all constraints are met). Т.к. схематика/описания схемы генерирующей clock 100М и 50М от автора не последовало, то предположу, что он сделал это место "правильно". Тогда для пересаживания импульса, длинной от 1 до 2 периодов CLK_100M на частоту 50М (получится импульс длинной в один период), достаточно такой схемы: ISE разведёт сигнал A с ограничениями как для 100М, и обратная связь (цепь Event_50M) со второго триггера на первый тоже будет разведена с ограничением как для 100М. Цепь Event_50M ко всем остальным синхронным элементам домена Clk_50M будет разведена с ограничениями как для 50М. Ну вот, как-то так примитивно всё получается,.. если схема генерирующая clock’и сделана правильно. -

Синхронизатор

Beby ответил AlphaMil тема в Работаем с ПЛИС, области применения, выбор

Это хорошо, что от одного генератора. Теперь остаётся уточнить, как Вы получали эти частоты: при помощи DLL ? Хорошо бы схемку (ну или HDL описание) глянуть этого места. Если всё сделать правильно, то и метастабильности не будет - а значит, всё будет тривиально (как функционально моделируется - так и работает,.. если, конечно all constraints are met). -

Синхронизатор

Beby ответил AlphaMil тема в Работаем с ПЛИС, области применения, выбор

Тут как-то совсем не прозвучало в исходном задании - являются ли исходные clock (100М и 50М) связанными - т.е. понимает ли среда при Place&Route какие соотношения между этими частотами или это асинхронные тактовые частоты ? Если есть асинхронщина, то будет и пара триггеров (метастабильный -> стабильный). Для достижения максимальной устойчивости работы проекта, как минимум, необходимо сделать так, чтобы линия данных между этими двумя триггерами была минимальной длины. А вот как это добиться уже зависит от конкретной ПЛИС (кстати, название среды разработки и семейство ПЛИС как-то тоже не были озвучены)... -

В большинстве случаев это так (исключение составляет только ущербный вариант с 5 и менее независимыми входами). Кстати, под этого ущербный вариант подпадает декодер. А для большого мультиплексора (собранного на LUT) более 6 входов на LUT и не надо (4 - данные, 2 - управление), для более глубокого мультиплексирования используются F7MUX (итого 2 LUT6: 8->1) и F8MUX (итого 4 LUT6 (один полный Slice): 16->1) Но на той картинке изображен не Xilinx Slice, а только его кусочек: Xilinx "LUT6" (2 связанных LUT5), а подписан как Slice - именно это я и имел в виду, говоря о неправильности картинки: Slice это всё-таки нечто гораздо большее, чем один Xilinx "LUT6". У Silce есть и другие проблемы: например, все синхронные элементы имеют один CLK. Эти «другие» проблемы лучше видны в FPGA Edit'е. Кстати, в семействах x7 этих проблем стало чуть меньше, чувствуется работа над ошибками. Да, RAM тяжело назвать "логической функцией"... но грамотное применение Distributed RAM часто уменьшает количество и глубину мультиплексоров собираемых на LUTx/ALM. По сути LUT6 - это и есть мультиплексор (64->1) содержимого его ОЗУ, а если задачу удаётся вывернуть так, что в это ОЗУ можно писать, то экономия становится колоссальной. Неее... - они исходили из других соображений. Спаренные входы 2xLUT5 позволяют значительно снизить количество входов в CLB, что заметно упрощает Routing Resource - а это может приводить к разным приятным последствиям. Xilinx утверждает, что если кому потребуется ну уж очень крутая логическая функция, то тогда к вашим услугам F7MUX и даже F8MUX (которые живут в том же Slice), ну, а то, что при этом погибнут несколько триггеров - и леший с ними - тут вопрос цены конечной ПЛИС в которую влезет проект (т.е. переплаты за того, что есть в ПЛИС, и чего мы не использовали). Неа - оно покруче оказалось ! Xilinx сказал, что они немного погорячились и перестраховались с завышенными задержками в -3, что мол в результате тестов оказалось, что то, что они выпускали под маркой -3, на самом деле работает как и -4 ! А -2 - как старый -3. В итоге бардак и неразбериха + необходимость перехода на свежие ISE (12.x + Speed File patch). У меня есть «старый» и «новый» DS_162 (Spartan-6 FPGA Data Sheet: DC and Switching Characteristics) – я их местами посравнивал «новые -3» по ряду параметров «быстрее» «старых -4» на 10 другой ps по разным параметрам !

-

Может для первой задачи Вам больше подойдёт Spartan-6 - если хватит ёмкости, то оно должно выйти заметно дешевле, что Virtex-2/5/6, да и Spartan-6 должен быть более шустрым, чем Virtex-2. Для второй задачки может оказаться интересным Virtex-5/6SX - у них значительно больше RAM (и block, и dsitributed) и DSP на LUT+FF, чем у аналогичных Virtex-5/6LX. Картинка приведена неправильная. Xilinx Slice состоит из много чего – там не только LUT. V6(x7) Slice’ы бывают 2 видов: SliceM и SliceL. SliceL – это SliceM в котором используются удешевлённые LUT6 (без возможности работы в режимах Shift Register и Distributed RAM). В S6 встречается еще более удешевлённый Slice – SliceX (от которого в x7 благоразумно отказались) - это SliceL без цепочек быстрого переноса. Но, при любом раскладе, для понимания структуры V6 Slice надо рассматривать целиком, а не какой-то огрызок показывать: Вот тут уже видно, что LUT6 – это более хитрая штука, чем то, что изображено на альтеровском рисунке. У всех SliceM LUT6 есть еще по 4 входа, которые «забыли» альтеровцы (2 DataIn, WE, WCLK) , а у нижних трёх LUT еще +6 входов (адрес записи данных, используемый в режиме Dual Port RAM) – итого от 10 до 16 входов на один SliceM LUT6 ! А Вы нам про какую-то «многофункциональность» говорите. Да, эти режимы не часто используются (поэтому и появились удешевлённые SliceL) – но как без этих режимов становится тоскливо ! Также надо иметь в виду, что у каждой V6 LE (LUT6+2FF) - по 3 выхода, которые можно использовать одновременно.

-

Так вроде же у супостата тут всё уже написано: From the Xilinx Virtex-6 Libraries Guide: "The BUFH primitive is provided to allow instantiation capability to access the HCLK clock buffer resources. The use of this component requires manual placement and special consideration and thus is recommended for more advanced users. Please refer to the Virtex-6 FPGA Clocking Resources User Guide (UG362) for details in using this component." You usually don't have to bother with this module, unless you know what you're doing. ... Обращаю особое внимание на последную приведённую строчку. Если есть какие-то конкретные вопросы - их надо конкретно задавать, иначе вряд ли кто что ответит, акромя: You usually don't have to bother with this module, unless you know what you're doing.

-

Первые впечатления от ISE

Beby ответил Мур тема в Среды разработки - обсуждаем САПРы

А галочка появилась забавная в опциах XST: VHDL 200X -

Xilinx ISE 13.1

Beby ответил vugluskr тема в Работаем с ПЛИС, области применения, выбор

В опциях XST появилась галочка VHDL 200x... -

Просмотр результатов синтеза

Beby ответил klop тема в Среды разработки - обсуждаем САПРы

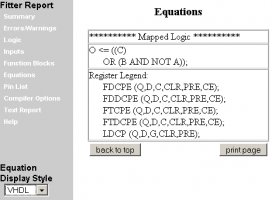

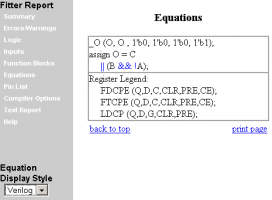

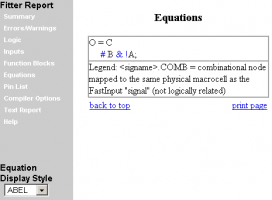

Отвечать удобней в обратном порядке, хе-хе. 3. В Xilinx ISE: Fitter - только у CPLD, у FPGA - MAP / P&R. 2. Нижеприведённый пример добытый в ISE 10.1.03, из кода library IEEE; use IEEE.Std_Logic_1164.all; Library UNISIM; use UNISIM.vcomponents.all; entity CLK is port ( A: in std_logic; B: in std_logic; C: in std_logic; O: out std_logic ); end entity; architecture Arc of CLK is begin O <= (not(a) and B) or C; end architecture; 1. Запустаем Fitter Report и бредём в раздел equation, а далее выбираем вид: Abel, VHDL или Verilog. .. Ну вот Вы его и увидели в отчёте fitter'а... а дальше-то что ?? -

Ссылок дать не могу, но попробую кратенько дать отправную точку, чтобы было легче читать документацию - без её чтения ливить нечего. 0. Ну, коли лень читать документацию, то необходимо взять FPGA Editor и внимательно рассмотреть ПЛИС - что, где и как лежит, а также как туда добраться - без понимания всего этого, работа с ПЛИС - баловство. 1. Есть куча синхронных элементов (nриггеры, блочная память, распределённая память и пр. дрянь). На всё это должны подаваться (да еще и синхронно в пределах одного clock domain !) различные тактовые сигналы. Линии, доставляющие эти сигналы, должны уметь работать с огромной нагрузкой (т.е. на этих линиях сидит много входов - количество входов обзывается: Fanout). Соответственно, у линий, доставляющие эти сигналы должны быть весьма мощные драйверы (буфера). 2. Так как из вышесказанного следует, что всё это сильно отличается от обычных линий, то такие линии и буферы были выделы в отдельную категорию - clocking resource... Ну а затем, по мере развития ПЛИС туда добавились и DLL, PLL и пр. прелести жизни. 3. По своему назначению, clock должен приходить только на тактовые входы синхронных элементов, поэтому, в большинстве ПЛИС, нет штатных линий для подачи clock'а на обычные линии. (именно поэтому у Вас и ругается MAP во втором случае. Вывод clock'а за пределы кристалла делается по иному, например через DDR регистр) 4. Для того, чтобы у схемотехника не сорвало крышу от работы с ненужными подробностями, система доставки одного clock'а примитивно изображается одним BUFG и подключенной к нему системой глобальных тактовых линий. 5. Clock - это дорогое удовольствие. Поэтому всё, что связанно с clock'ами в ПЛИС, находится в ограниченном количестве. 6. В ПЛИС есть особые ножки ввода(/вывода), от которых проложены особые трассы к BUFG (а в некоторых случае можно запитать с них и DLL/PLL - это уже надо рассматривать подробно FPGA Editor'ом). Вот как раз в документации подробно и расписано: откуда и до чего можно дотянуться. А т.к. всё это бурно развивалось 10 лет, то и информации в документации вывалено куча. Возможно, Вам имеет смысл проследить развитие clocking resource ПЛИС: Spartan-1 -> Spartan-2 (или Virtex-1), Spartan 3x, Spartan 6. Тогда всё станет просто и понятно: что, как и для чего было сделано, а также, почему оно было сделано именно так.

-

Вроде же минимальная стандартная (по IEEE 802.3) пауза между пакетами 12 тактов по 8нс (125МГц) каждый. Или я что-то не правильно понял ?

-

Отладка проектов

Beby ответил D-Luxe тема в Работаем с ПЛИС, области применения, выбор

Как что делать ?? - cross clock domain переход делать... для управляющих сигналов синхронизаторы делать, а для данных обычно надобно FIFO прилаживать. Вот над этим и ломают головы люди умные... как бы оно так половчее сделать, чтобы безотказно работало, да еще и с меньшей задержкой данные передавало, и места бы чтобы поменьше занимало. Вот и приходится ставить синхронизаторы для перехода с ClkX на ClkY, а чтобы MAP/P&R голову долго не ломали по дополнительному constaint'у накладывать приходится на каждое направления перехода (как я и писал ранее)... Да и в самих синхронизаторах constaint’ов разных по пачке, чтобы подавлялась метастабильность получше. -

Отладка проектов

Beby ответил D-Luxe тема в Работаем с ПЛИС, области применения, выбор

1. При такой записи SYS_clk0 и SYS_clk1 будут для Timing Analyzer'а связаны по фазе, а в реальности этого может и не быть - не зря же они на разные входы подаются... 2. Для особоневерующих есть более интересный случай, если взять соотношение частот не 2, а, например, 1.01 - вот потеха начнётся... Для тех, кому лень код писать, а покрутить гаечки хочется: VHDL: library IEEE; use IEEE.Std_Logic_1164.all; Library UNISIM; use UNISIM.vcomponents.all; entity CLK is port ( IN_D: in std_logic; IN_CLK: in std_logic_vector(1 downto 0); OUT_Q: out std_logic_vector(1 downto 0) ); end entity; architecture Arc of CLK is signal CLK_UB: std_logic_vector(OUT_Q'Range); signal CLK: std_logic_vector(OUT_Q'Range); signal D: std_logic; signal Q: std_logic_vector(OUT_Q'Range) := (others => '0'); attribute iob: string; attribute iob of Q: signal is "false"; begin D_IBUF: component IBUF port map ( I => IN_D, O => D ); IO: for i in CLK'Reverse_Range generate CLK_IBUF: component IBUFG port map ( I => IN_CLK(I), O => CLK_UB(i) ); CLK_BUFG: component BUFG port map ( I => CLK_UB(I), O => CLK (i) ); Q_OBUF: component OBUF port map ( I => Q(I), O => OUT_Q (i) ); end generate; Q(0) <= D when rising_edge(CLK(0)); Q(1) <= Q(0) when rising_edge(CLK(1)); end architecture; UCF: NET "IN_CLK<0>" TNM_NET = CLK0; NET "IN_CLK<1>" TNM_NET = CLK1; TIMESPEC TS_CLK_0 = PERIOD "CLK0" 5 ns HIGH 50%; TIMESPEC TS_CLK_1 = PERIOD "CLK1" TS_CLK_0*1.01 HIGH 50%; Для ленивых результат от P&R: ------------------------------------------------------------------------------------------------------ Constraint | Check | Worst Case | Best Case | Timing | Timing | | Slack | Achievable | Errors | Score ------------------------------------------------------------------------------------------------------ * TS_CLK_1 = PERIOD TIMEGRP "CLK1" TS_CLK_0 | SETUP | -1.706ns| 177.356ns| 1| 1706 * 1.01 HIGH 50% | HOLD | 0.678ns| | 0| 0 ------------------------------------------------------------------------------------------------------ TS_CLK_0 = PERIOD TIMEGRP "CLK0" 5 ns HIG | N/A | N/A| N/A| N/A| N/A H 50% | | | | | ------------------------------------------------------------------------------------------------------ P.S. Вот с этим (метастабильностью) и развлекаются при cross clock domain переходах. -

Подскажите плату

Beby ответил D-Luxe тема в Работаем с ПЛИС, области применения, выбор

В Virtex-5 много косяков с PCI-E, о них можно почитать в соответствующем документе: Virtex-5 FPGA Integrated Endpoint Block for PCI Express Designs User Guide, раздел Known Restrictions. В котором расписано, какие заплатки надо собирать, на косяковые места в PCI-E Embeded Core. Возможно Spartan-6 в этом отношении будет получше... хотя кто знает ? Есть еще потаённое семейство Virtex-6CXT (прародитель Kintex-7, слабее обычных Virtex-6, но заметно лучше Spartan-6), возможно оно окажется наиболее интересным,.. вот только не знаю: есть ли платы на этом семействе. -

Просмотр результатов синтеза

Beby ответил klop тема в Среды разработки - обсуждаем САПРы

Ну ISE выдавало подобные штуки в отчёте fitter'а... а дальше-то что ? -

Посоветуйте ПЛИС

Beby ответил vovanse тема в Работаем с ПЛИС, области применения, выбор

Да штука неплохая, но может оказаться более интересным вариант со встроенной SPI ROM: XC3S50AN-4TQ144C (для тех, кто не в курсе: N - говорит о наличии встроенного SPI ROM, с которого можно грузиться). -

Э-хе-хе - начнём от печки... 1. Какой кристалл у Вас ?

-

Маленькая поправка: просто Spartan (да и просто Virtex тоже) уже в морге и назначен день похорон (см. Product Discontinuation Notice): Final orders are accepted until October 18, 2011. Final deliveries must occur on or April 18, 2012. Некрофилы еще могут успеть заказать себе немного того и этого,.. но есть ли смысл ?..

-

Отладка проектов

Beby ответил D-Luxe тема в Работаем с ПЛИС, области применения, выбор

Максимум - 2, но ведь не всегда надо переходить в обе стороны, иногда используются и односторонние переходы - всё зависит от конкретной схемотехники. Если быть более точным, то timing analyzer в ISE c 9.1 по 11.5 (в остальных не помню) выдаёт только warning: some constraints are not met. При компиляции среда как-то раскладывает элементы и пытается это развести, затем оценивает, с какими constraints проблемы и старается итерационно эти проблемы устранить. В параметрах генерации Post-P&R Static Timing Report есть поле Report Unconstrained Paths, впишите туда 250 - и увидите 250 путей не имеющих constraint'ов. Так Вы увидите, на что именно Вы забыли наложить ограничения; далеко не на всё, что там указано, имеет смысл накладывать ограничения... но ознакомиться с этим списком просто необходимо. -

Отладка проектов

Beby ответил D-Luxe тема в Работаем с ПЛИС, области применения, выбор

Да, именно частоты (или периоды) необходимо задать только у входных clock'ов (лучше назначать на связь, относящуюся к положительной половинке входной ножки). И стараться ни в коем случае не задавать их на внутренние линии. Да в этом случае Вам необходимо описать 5 разных constraint для входных частот (я так понял clock generator - это нечто (PLL/DLL и пр.) внутри ПЛИС). Однако, коли частот пять, то должны появиться и cross clock domain переходы - вот для этих переходов понадобится еще наложить некоторое количество дополнительных constraint - по одному на каждый переход на каждое направление перехода.