-

Постов

1 220 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные PCBtech

-

-

поддерживаю

вот например разбираясь с OrCAD_Capture_TclTk_Extensions.pdf (SPB_xx\tools\capture\tclscripts\) отсутствие хелпа по командам, усложняет написание расширений (вернее я забросил эту попытку совсем).

Подскажите все-таки что-нибудь про команды

(например команда alias, без аргументов, открывает окно funkeys, мелочь а приятно :rolleyes: )

Команды можно посмотреть, выполняя соответствующие функции меню или нажимая кнопки.

Все протоколируется в специальном файле. В Capture все команды можно отображать на экране.

-

Где описаны команды PCB Designer для командной строки? Хелпа у меня нет, его антивирус убил...

Конкретно интересует установка компонента по заданным координатам.

Параллельно хелпу есть PDF-файлы с тем же содержимым.

Там все описано.

Зачем вам команды в командной строке, если все можно сделать через меню или горячие кнопки?

Ну, если что, координату можно ввести командой x 100 200

где 100 - это требуемая координата x, а 200 - это y

А если нужна относительная координата, то команда ix 100 200

-

Добрый день!

В рамка семинара вы можете осветить тему косимуляции моделей в pspise и simulink моделей? и если есть ссылки на литературу по этой теме можете поделиться?

Да, одна из тем будет:

Использование алгоритмических моделей в PSPICE.

В том числе можем показать и связь между PSpice и Matlab/Simulink.

Какие еще темы были бы вам интересны?

-

Через Import Gerber втянуть герберы получается только по одному файлу, а вот как их потом состыковать, точно наложить друг на друга?

Да, удобнее через IPC-2581, то же самое, что герберы, но слеплено вместе и отцентровано.

Или вариант еще лучше - Allegro/OrCAD Productivity Toolbox, там функционал панелизации есть, среди многих других полезных фишек.

-

-

Вебинар: Ускорьте вашу разработку печатных плат

Знакомство с улучшениями в Cadence Allegro 17.2

Дата: Среда, 19 октября 2016

Время: 18:00 Мск, 60 минут

Чем быстрее вы справитесь с проектом печатной платы, тем больше будет прибыль вашего предприятия и,

возможно, ваша премия.

Присоединяйтесь к нашему вебинару и посмотрите, как вам могут помочь последние улучшения в Cadence Allegro/OrCAD PCB Editor 17.2.

- Уменьшение количества пересылок проекта между разработчиком платы и 3D-конструктором.

- Сокращение времени на трассировку дуг. Используйте трассировку вдоль контура.

- Создавайте переходные отверстия с обратной сверловкой автоматически. Все правила будут обеспечены системой, и документация будет безошибочной, равно как и производственные файлы.

Ознакомьтесь с последними техниками повышения вашей эффективности, и автоматизацией рутинных работ.

Зарегистрироваться для просмотра вебинара >

-

Работаю в OrCAD PCB Designer Standart.

Встал вопрос мультипликации плат на одной заготовке.

Можно конечно и в сам 350, что я раньше и делал, но хотелось бы знать как это делать в

рабочей программе.

В пикаде и альтиуме я делал без проблем.

Панелизация есть в OrCAD Productivity Toolbox

Либо, как наши разработчики делают - рисунок контура панели и размещение плат на панели - в специальном слое,

а топология - только на месте самой левой нижней платы.

Подразумевается, что в остальных местах - полная копия топологии.

Еще один вариант - через Import Gerber втянуть герберы платы и размножить их,

там уже проблем не будет.

Но вопрос, что потом делать, когда вы захотите поменять топологию. Заново мультиплицировать?

-

А где найти, этот скил cwidth.il, в папке с программой не нашел, скинте пожалуйста.

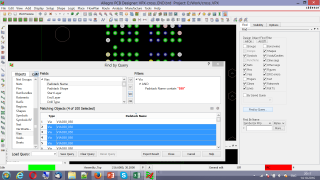

И второй вопрос, как можно выделить via, строго одного диаметра на всей плата ??, выделить чтобы потом сделать replace..

Ну а чем Вам не нравится Find By Query?

Все что угодно можно найти и отфильтровать.

А скилл для изменения ширины - вот, только надо его проверить под вашу версию Allegro.

Но может быть, он и не нужен, т.к. FindByQuery может и линии нужной ширины выделить спокойно:

-

В Москве с 28 ноября по 2 декабря проходит конференция по моделированию печатных плат

Форум PCB-2016 http://www.pcbsoft.ru/pcb-2016

Там специалисты могут "в рамках семинара" вашу плату промоделировать в Sigrity и найти,

откуда помеха прет. И подскажут, как скорректировать проект.

возникла (неожиданно) задача пройти EMI тест, ну и без подготовки это не получилось (помехи в области >1ГГц)по результатам измерения - видны гармоники 35dBuV/m, а нужно, в соответствии с профилем, где-то на 10dBuV/m меньше (я не вдаюсь в то, какой тест, по какому стандарту и т.д. - делали это специальные люди со специальными приборами, антеннами, в безэховой камере и т.д. - по моему, в рамках такого вопроса это не важно)

при этом гармоники от процессора достаточно маленькие и удовлетворяют маске, а от ПЛИС не удовлетворяют.

причем у ПЛИС, скорее всего, эта частота присутствует только в ядре, то есть помеха с питания ядра (это мое дилетантское предположение)

ну естественно, большая часть этой цепи - полигон во внутренних слоях, но есть места, где этот полигон идет по торцу платы, ну и соответственно, в источнике и под плисиной выходит на внешние слои

-------------------

можно ли это как-то промоделировать с весьма малыми трудозатратами и низкой квалификацией в RF? ну то есть у меня есть pcb, есть частота, я могу задать какие-то значения тока (предположить все динамическое потребление ядра на этой частоте) и т.д.

собственно - какие софты для этого существуют (if any) ну и стоит ли с этим связываться или задача не для любителя?

-------------------

цель -

1) подтвердить подозрение, что источник помех это питание ядра

2) изменить pcb и проверить - улучшилось или нет

-

Здравствуйте,

можно подробнее про Capture через удаленный рабочий стол?

Запускаете на другом компьютере или виртуальной машине под Windows, делаете "удаленный рабочий стол", ну как бы терминал,

работаете из Линукса.

Это вам ваши сисадмины лучше расскажут.

-

Купили виндовую версию, а ради двух человек из 11 никто линуксовую не будет брать.

Пытаюсь 16.6 поставить под wine, виснет на этапе начала установки.

Если вы купили лицензии, то не важно, для какой ОС - можете скачать с сайта саппорта версию для Линукса, будет работать точно также.

А насчет установки схемного редактора под Wine - надо будет уточнить у специалистов.

А может, ограничиться работой с Capture через удаленный рабочий стол?

-

А Capture может?

А для Capture, да, нужен wine.

-

Здравствуйте.

У нас контора закупила Cadence Allegro/OrCAD 17.2, кто-нибудь запускал сию программу на wine?

Allegro PCB Editor может работать под Linux, зачем вам wine?

-

Новый видеоролик о том, как в Sigrity извлечь топологию подложки leadframe и промоделировать паразитные свойства.

-

В Москве планируется провести семинар по моделированию в PSPICE.

28 ноября 2016 года.

Приедет зарубежный специалист с огромным опытом SPICE-моделирования,

создания и подстройки моделей, и др..

Пока предполагается тематика проектирования и моделирования силовых схем, DC'/DC преобразователей,

но если есть пожелания по добавлению тем по моделированию аналоговых прецизионных схем,

или каких-то других тем, прошу писать в этой ветке форума.

-

Планируем провести полнодневный семинар по моделированию в PSPICE, в Москве 28 ноября,

в рамках PCB-форума 28 ноября - 2 декабря.

Будем рады любым пожеланиям по тематике, нюансам, которые нужно будет рассмотреть,

любым вопросам и проблемам, с которыми вы столкнулись и которые надо решить.

Пожалуйста, комментируйте в этой теме.

-

Добрый день

Возник вопрос у издательства - имеет ли смысл переиздавать книгу?

OrCAD Pspice

АНАЛИЗ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ

Джон КЕОУН

http://programming-lang.com/ru/comp_soft/keoun/0/j0.html

Кто что посоветует?

-

А по результатам данного семинара будут выкладываться материалы?

Или тут то же, что было в Питере, но в урезанном варианте?

Семинар проходит с живым показом в системах моделирования, а не по слайдам.

В принципе тематика совпадает с тем, что было в Питере, но это всегда немножно по-другому.

Например, сейчас выступает Антон Супонин с демонстрацией своего исследования с помощью Sigrity -

о том, какие вырезы добавлять в плейнах под проходными конденсаторами для устранения

скачка импеданса. Это если скорость передачи в канале выше 3 Гбит/с.

Материалы выложим на сайте www.pcbsoft.ru

там на главной странице внизу можно подписаться на рассылку наших новостей,

тогда вы узнаете и о появлении материалов, и о последующих семинарах по различным темам,

связанным с проектированием печатных плат.

-

Прошел первый день семинара в Ростове-на-Дону.

Как обычно, наш эксперт Срджан Джорджевич очень интересно рассказывает и показывает нюансы анализа качества трассировки.

Сегодня было описание анализа по постоянному току и нагреву платы (на основе Sigrity PowerDC),

а также целостности питаний (на основе Sigrity PowerSI).

Завтра - анализ и верификация целостности сигналов - последовательные интерфейсы и параллельные шины

(утилита Sigrity SystemSI), а также нюансы трассировки DDR.

В том числе, по ходу дела проводится и анализ проектов, присланных заказчиками,

из различных САПР - Altium, P-CAD, Mentor, Zuken.

По найденным проблемам и ошибкам - рекомендации по их корректировке.

В целом - как всегда, все внимательно слушают, задают вопросы, по-моему - это получится очень полезно для всех посетителей.

В четверг-пятницу аналогичный семинар проводим в Екатеринбурге. Если кто-то из близлежащих городов еще не записался - следует поторопиться.

-

В описании HotFix 004, а не 005.

В описании - QIR1, то есть первый квартальный релиз.

Hotfix 005 исправляет некоторые найденные ошибки, но не добавляет функционал.

Квартальные релизы добавляют новый функционал.

-

Вышел хотфикс OrCAD/Allegro 17.2 s005 (1,1 GB).

Что скажете про него?

Проверим - напишем.

Должно появиться много интересных улучшений.

Кстати, компания Cadence предлагает сейчас мощные сборки именно версии 17.2 по очень невысокой цене,

нам кажется, что это может быть очень интересно для текущих пользователей Allegro/OrCAD,

желающих опробовать дополнительные опции версии 17.2.

Вот небольшое описание:

Их можно установить параллельно с имеющимися лицензиями 16.6, переключаться с помощью программы Switch Release.

Update:

Вот описание новых возможностей первого квартального обновления Allegro/OrCAD QIR1 версии 17.2

Во-первых, новый редактор 3D (его надо включить через настройки).

Во-вторых, модернизированный поиск объектов с помощью запроса - Find-by-Query

В-третьих, интересный оптимизатор ручной трассировки (центровка линий между падами, итд.)

Что еще интересного:

- групповая трассировка шин с привязкой к крайней трассе

- создание бэндлов ("связок") с привязкой к углу наклона 45 градусов.

- назначение нескольких слоев для трасс внутри одного бэндла

- улучшенный вид "разделенного экрана", чтобы увидеть оба конца бэндла

- трассировка микрополосковых линий полигонами для СВЧ-плат - похоже, что эту функцию перетащили из RFOption в базовую лицензию

- поддержка Chip On Board и, соответственно, сварных перемычек - похоже, эту функцию перенесли из APD/SiP в базовую лицензию Allegro!

В дополнительных опциях:

- сравнение двух PCB-проектов с графической индикацией отличий.

В схемном редакторе тоже появились новшества:

- просмотр схемы в виде HTML

- сравнение двух схем с сохранением отличий в HTML

- защита схем паролем

- настраиваемое окно поиска

- настраиваемое окно Browse Parts

- наконец-то сделали "Найти и заменить" для имен цепей, портов, коннекторов итд.

К системе аналогового моделирования PSPICE:

добавлены несколько мануалов:

■ PSpice TCL Command Reference

Describes PSpice and PSpice Advanced Analysis TCL APIs in detail.

■ PSpice TCL Sample Scripts

Describes various sample scripts that you can use directly, or with minimum path

changes, in PSpice and PSpice Advanced Analysis.

■ PSpice Device and System Modeling with C/C++ and SystemC

This document has been updated with the new content with respect to the following four

types of PSpice DMI model simulation: Digital C/C++, Analog C/C++, VerilogA, and

SystemC

Полное описание новых возможностей QIR1:

Hotfix_SPB17.20.005_README_Release_Notes.pdf

Если кому-то недоступен сайт http://support.cadence.com/

и поэтому вы не можете скачать дистрибутив и хотфиксы,

обращайтесь, сделаем временный ключ для доступа.

-

Поизучал вашу первую ссылку. Там все понятно, и я так делал. Но. Полный набор

кривых для всех шагов не нужен. Нужны только два крайних случая - worst case. Так вот, Orcad Pspice почему-то считает отдельно максимальное отклонение

в "+" и в "-". Вот это меня поставило в тупик, для меня это глупость. Мне нужен весь диапазон макс отклонений. Там в видео показано, как вывести эти два

графика одновременно. Это для меня было новым.

Используя общий поиск, вне зависимости от языка нашел отличное видео с продвинутым Монте-Карло:

https://www.youtube.com/watch?v=ptpi-6UPrO8

Там уже вещи полезные для меня.

Планируем в ноябре провести в Москве большой семинар по SPICE-моделированию.

Хотелось бы понять, какие темы наиболее актуальны для российских разработчиков.

Т.е. моделирование каких систем, какие задачи, какие проблемы надо решить.

-

Что-то я сомневаюсь, что можно прометаллизировать торец платы, если нет металлизации по краю на Top и Bottom, хотя бы узкой полоски.

А так - да, надо указать на чертеже область металлизации и область отсутствия металлизации торца.

Вопрос новичка:-надо две платы сопрячь. Смотри sam_1.jpg

- хотелось бы для экономии места на плате применить

концевой разъем от SAMTEC типа QTS-EM. Смотри sam_2.jpg.

У него два ряда контактов - один попадает на TOP платы,

второй - на BOTTOM и выводы GND - они попадают на

край платы EDGE. Смотри sam_3.jpg

Вопрос :

- Как на 4-слойной плате в Allegro PCB выполнить металлизацию

края EDGE в зоне разъема, чтобы припаять потом

его выводы GND?

По картинке - как сделать EDGE METAL?

Потом они туда накладывают SOLDER PASTE из шприца.

Хотя бы намекните, куда смотреть.

Спасибо

-

Webinar Not Available.

This webinar or its recording was removed. Please contact the organizer for more information.

Новая локальная ссылка на вебинар:

https://yadi.sk/i/MkxwRDFnv4yMS

Горячая линия по САПР Cadence Allegro

в Cadence

Опубликовано · Пожаловаться

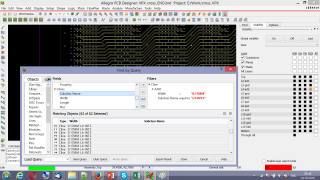

В Allegro можно так, например:

Нажимаете команду Move или горячую кнопку.

Потом выбор компонента из списка:

и указание, на какое расстояние его переместить:

Годится?